Register 61: Ethernet MAC Receive Interrupt Watchdog Timer

(EMACRXINTWDT), offset 0xC24

This register, when written with non-zero value, enables the watchdog timer for the Receive Interrupt,

RI (Bit 6), of the EMACDMARIS register at EMAC offset 0xC14.

Ethernet MAC Receive Interrupt Watchdog Timer (EMACRXINTWDT)

Base 0x400E.C000

Offset 0xC24

Type RW, reset 0x0000.0000

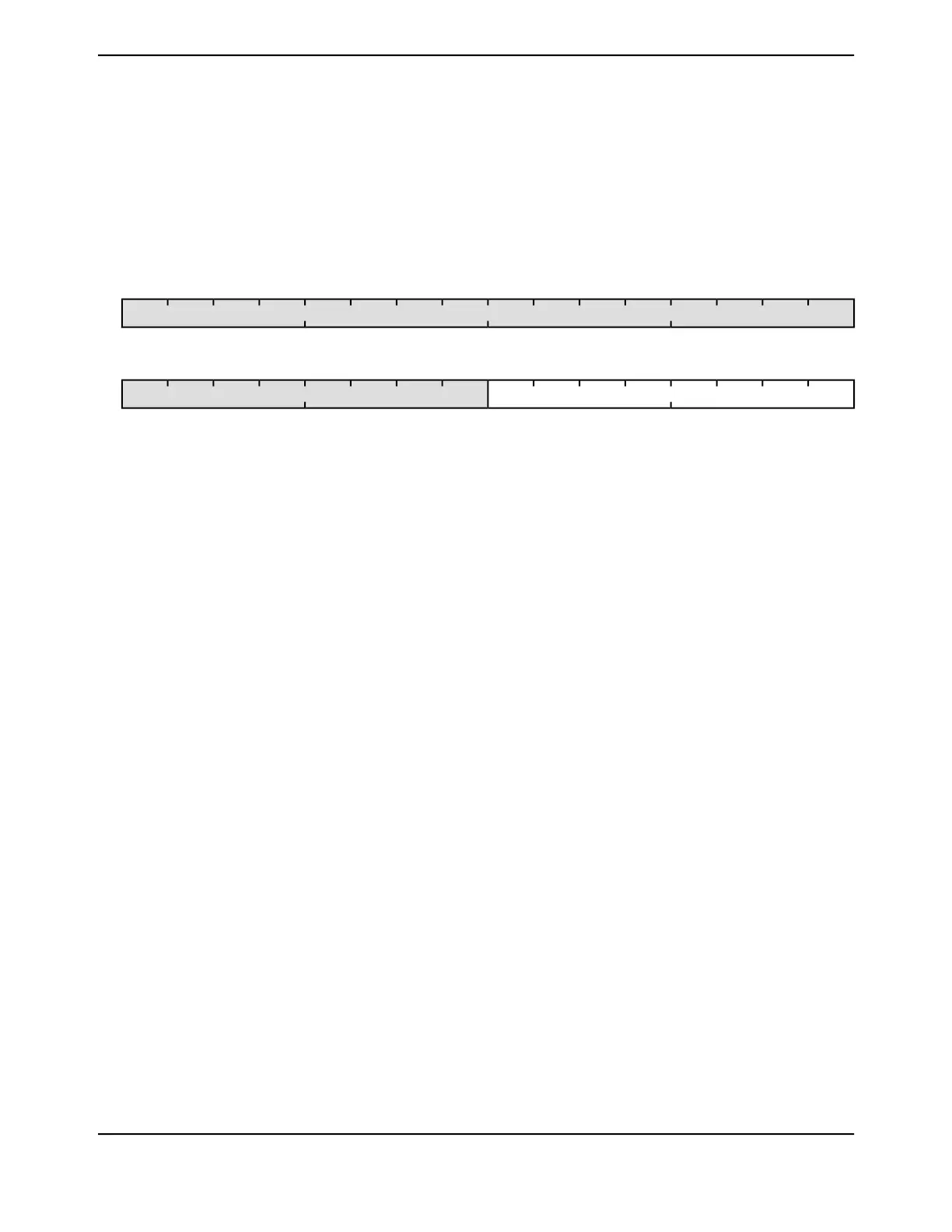

16171819202122232425262728293031

reserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

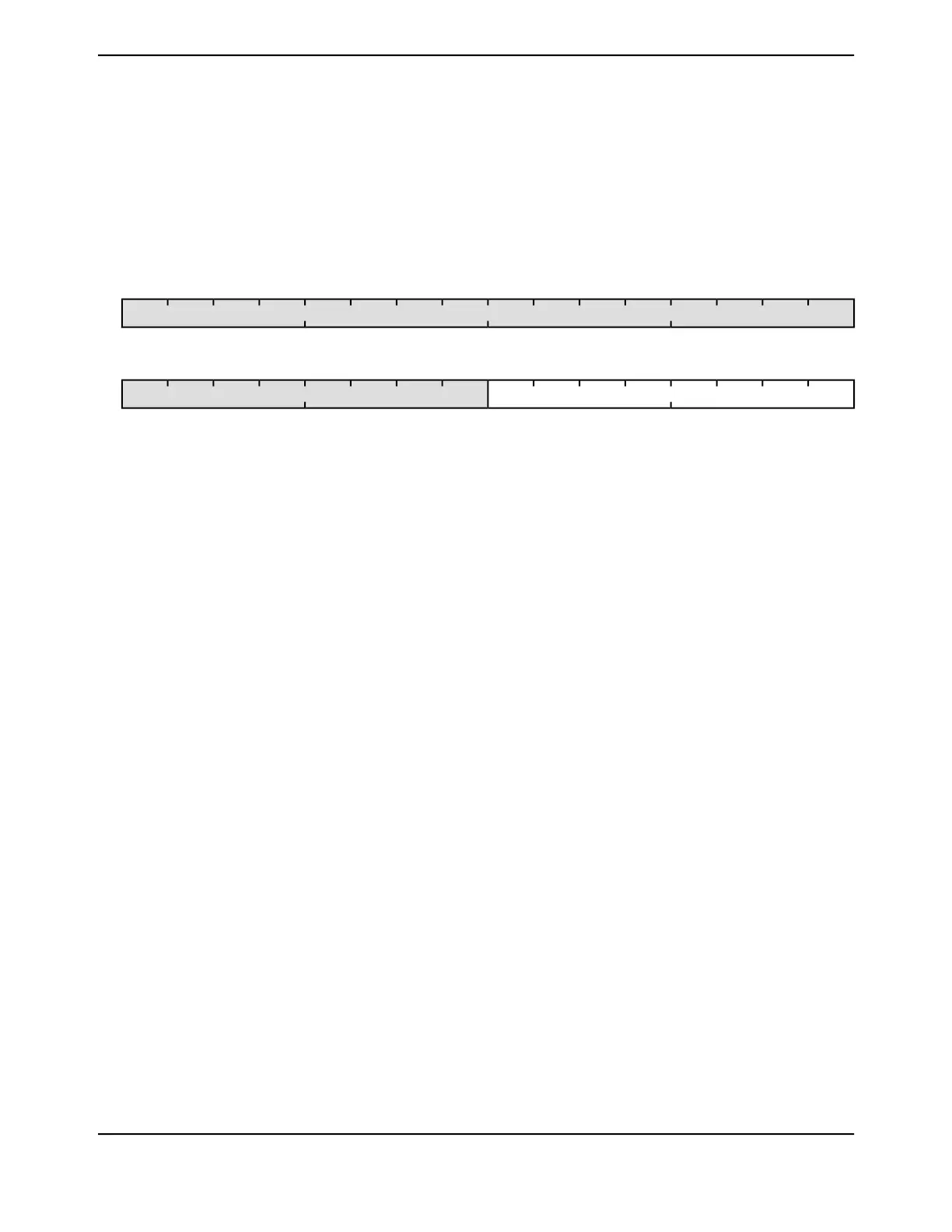

0123456789101112131415

RIWTreserved

RWRWRWRWRWRWRWRWROROROROROROROROType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0ROreserved31:8

Receive Interrupt Watchdog Timer Count

This field indicates the period in which the receive counter expires. The

value in this field is programmed by 256 to calculate the number of

system clock periods the timer must count.

Watchdog Timer Period = (RIWT * 256) system clocks.

When the watchdog timer runs out, the RI bit is set and the timer is

stopped.

If the RDES[31] bit is clear, the watchdog timer is reset.

0x0RWRIWT7:0

June 18, 20141576

Texas Instruments-Production Data

Ethernet Controller

Loading...

Loading...