Register 72: MPU Region Base Address (MPUBASE), offset 0xD9C

Register 73: MPU Region Base Address Alias 1 (MPUBASE1), offset 0xDA4

Register 74: MPU Region Base Address Alias 2 (MPUBASE2), offset 0xDAC

Register 75: MPU Region Base Address Alias 3 (MPUBASE3), offset 0xDB4

Note: This register can only be accessed from privileged mode.

The MPUBASE register defines the base address of the MPU region selected by the MPU Region

Number (MPUNUMBER) register and can update the value of the MPUNUMBER register. To

change the current region number and update the MPUNUMBER register, write the MPUBASE

register with the VALID bit set.

The ADDR field is bits 31:N of the MPUBASE register. Bits (N-1):5 are reserved. The region size,

as specified by the SIZE field in the MPU Region Attribute and Size (MPUATTR) register, defines

the value of N where:

N = Log

2

(Region size in bytes)

If the region size is configured to 4 GB in the MPUATTR register, there is no valid ADDR field. In

this case, the region occupies the complete memory map, and the base address is 0x0000.0000.

The base address is aligned to the size of the region. For example, a 64-KB region must be aligned

on a multiple of 64 KB, for example, at 0x0001.0000 or 0x0002.0000.

MPU Region Base Address (MPUBASE)

Base 0xE000.E000

Offset 0xD9C

Type RW, reset 0x0000.0000

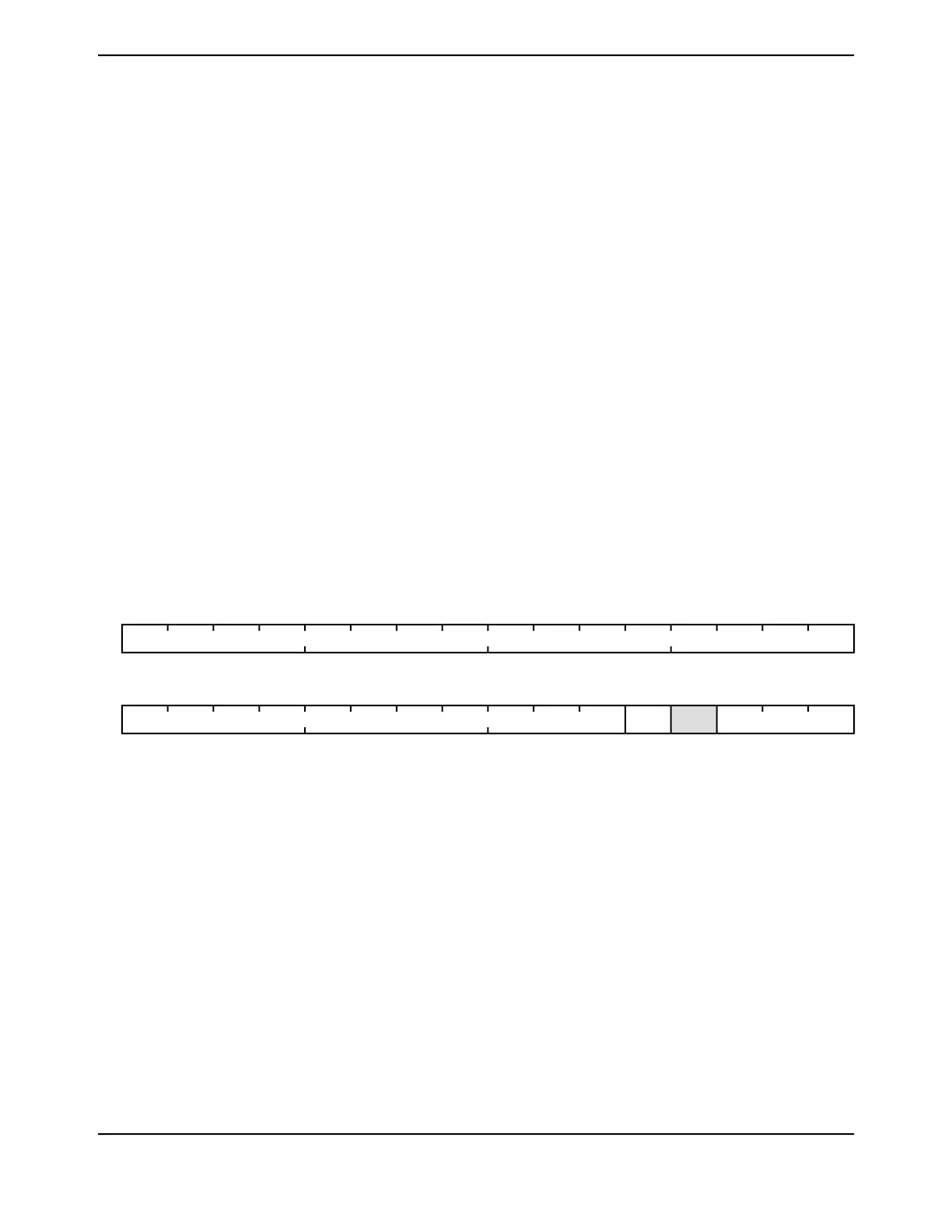

16171819202122232425262728293031

ADDR

RWRWRWRWRWRWRWRWRWRWRWRWRWRWRWRWType

0000000000000000Reset

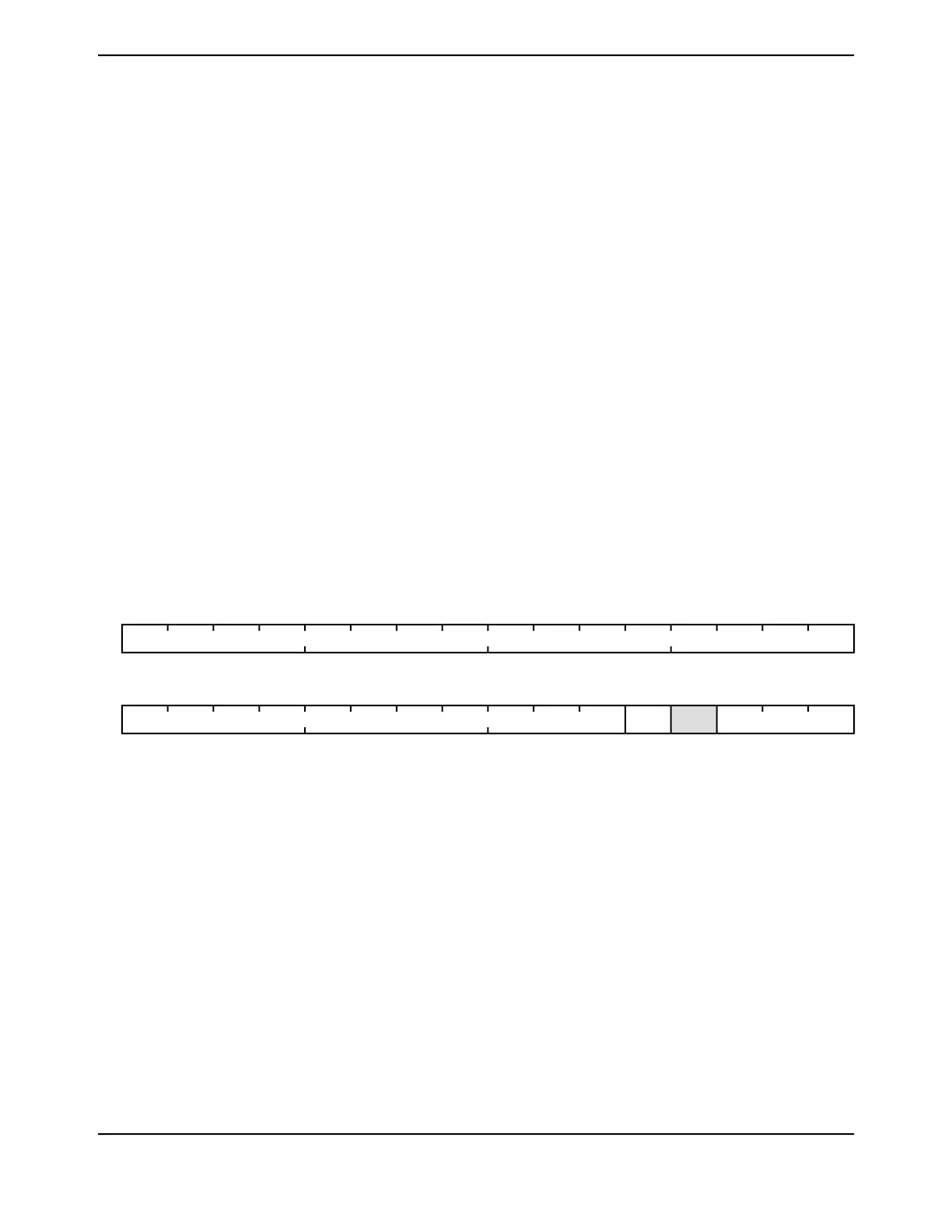

0123456789101112131415

REGIONreservedVALIDADDR

RWRWRWROWORWRWRWRWRWRWRWRWRWRWRWType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

Base Address Mask

Bits 31:N in this field contain the region base address. The value of N

depends on the region size, as shown above. The remaining bits (N-1):5

are reserved.

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0000.000RWADDR31:5

197June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...