Register 8: UART Control (UARTCTL), offset 0x030

The UARTCTL register is the control register. All the bits are cleared on reset except for the Transmit

Enable (TXE) and Receive Enable (RXE) bits, which are set.

To enable the UART module, the UARTEN bit must be set. If software requires a configuration change

in the module, the UARTEN bit must be cleared before the configuration changes are written. If the

UART is disabled during a transmit or receive operation, the current transaction is completed prior

to the UART stopping.

Note: Registers that contain bits for modem control or status only apply to the following UARTs:

■ UART0 (modem flow control and modem status)

■ UART1 (modem flow control and modem status)

■ UART2 (modem flow control)

■ UART3 (modem flow control)

■ UART4 (modem flow control)

Note: The UARTCTL register should not be changed while the UART is enabled or else the results

are unpredictable. The following sequence is recommended for making changes to the

UARTCTL register.

1. Disable the UART.

2. Wait for the end of transmission or reception of the current character.

3. Flush the transmit FIFO by clearing bit 4 (FEN) in the line control register (UARTLCRH).

4. Reprogram the control register.

5. Enable the UART.

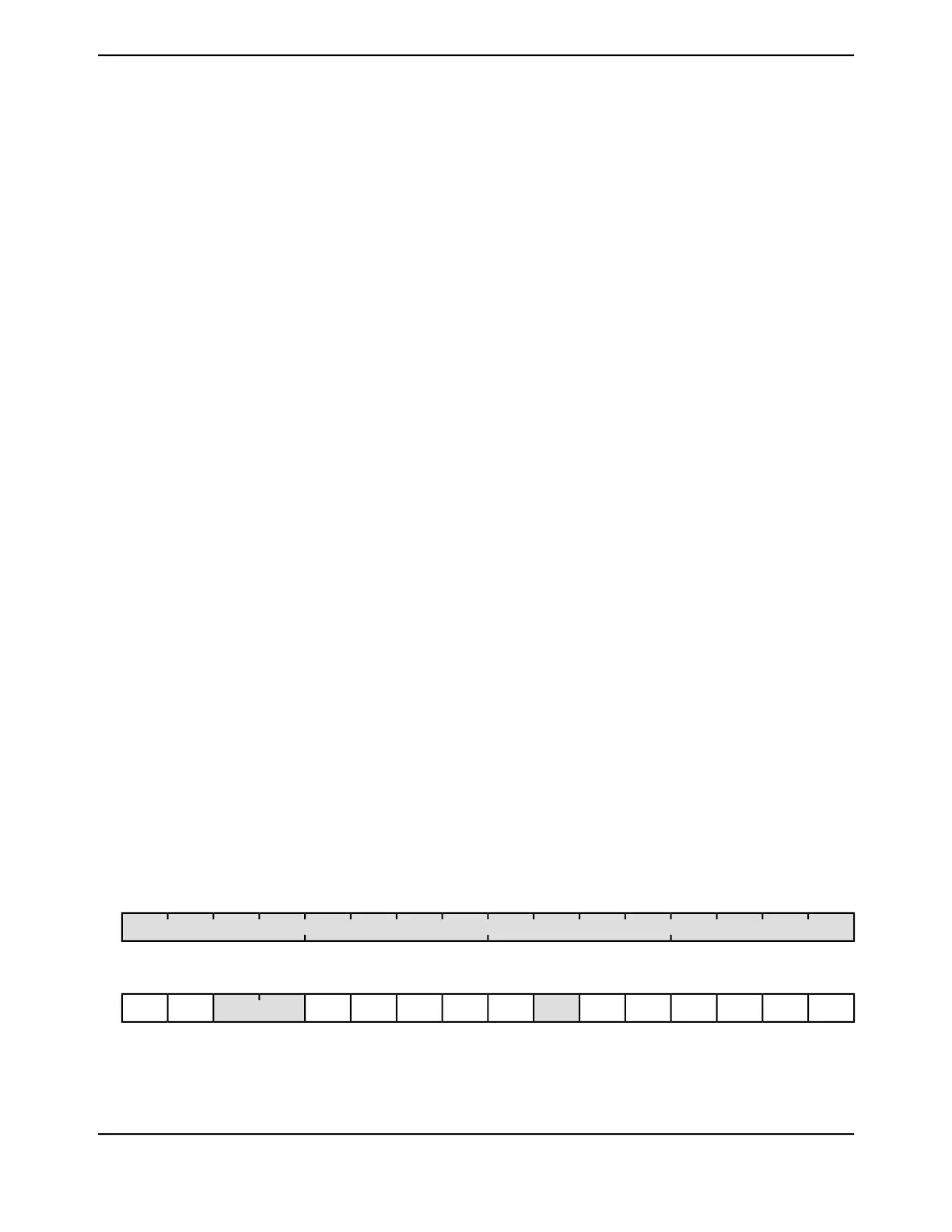

UART Control (UARTCTL)

UART0 base: 0x4000.C000

UART1 base: 0x4000.D000

UART2 base: 0x4000.E000

UART3 base: 0x4000.F000

UART4 base: 0x4001.0000

UART5 base: 0x4001.1000

UART6 base: 0x4001.2000

UART7 base: 0x4001.3000

Offset 0x030

Type RW, reset 0x0000.0300

16171819202122232425262728293031

reserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

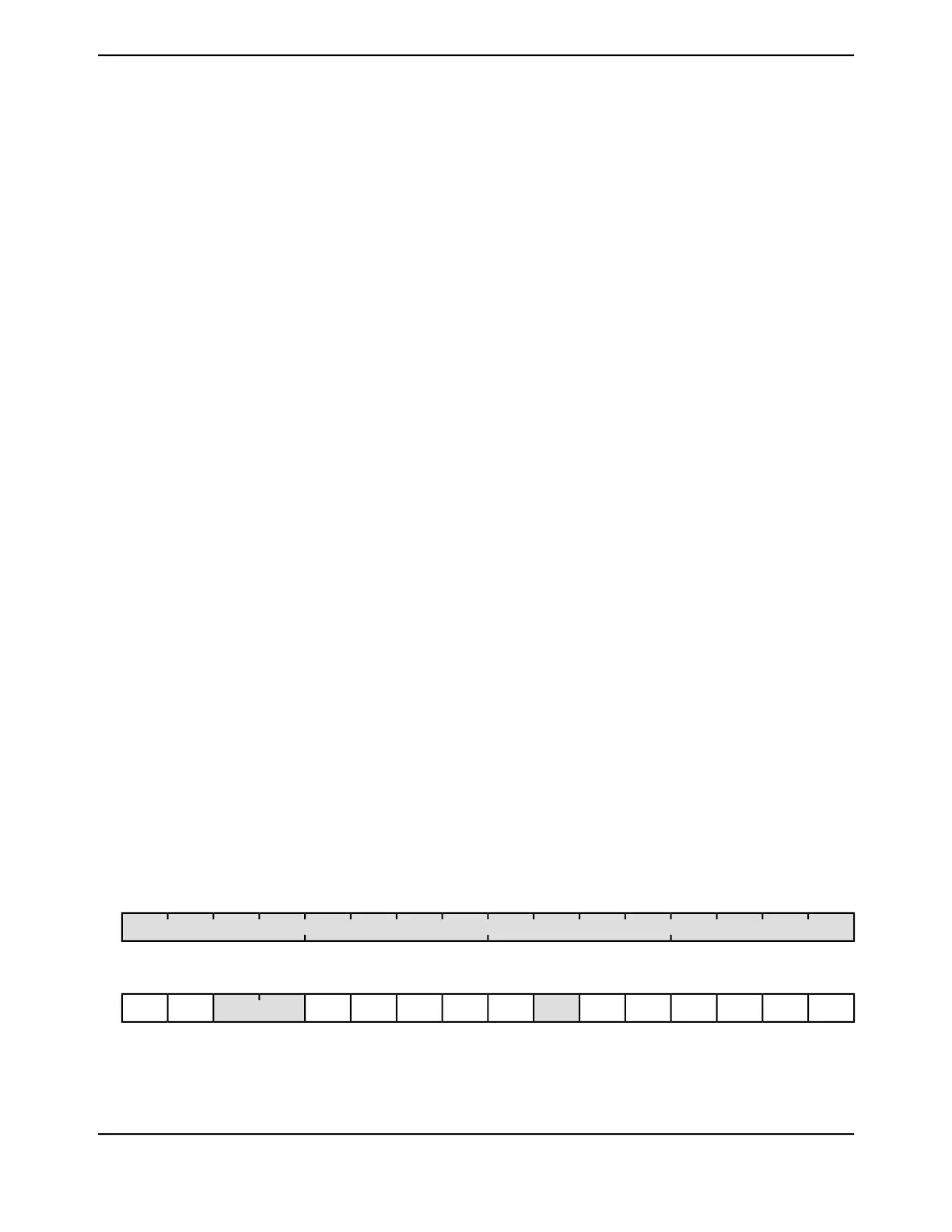

0123456789101112131415

UARTENSIRENSIRLPSMARTEOTHSEreservedLBETXERXEDTRRTSreservedRTSENCTSEN

RWRWRWRWRWRWRORWRWRWRWRWRORORWRWType

0000000011000000Reset

June 18, 20141188

Texas Instruments-Production Data

Universal Asynchronous Receivers/Transmitters (UARTs)

Loading...

Loading...