Register 35: GPIO Peripheral Identification 7 (GPIOPeriphID7), offset 0xFDC

The GPIOPeriphID4, GPIOPeriphID5, GPIOPeriphID6, and GPIOPeriphID7 registers can

conceptually be treated as one 32-bit register; each register contains eight bits of the 32-bit register,

used by software to identify the peripheral.

GPIO Peripheral Identification 7 (GPIOPeriphID7)

GPIO Port A (AHB) base: 0x4005.8000

GPIO Port B (AHB) base: 0x4005.9000

GPIO Port C (AHB) base: 0x4005.A000

GPIO Port D (AHB) base: 0x4005.B000

GPIO Port E (AHB) base: 0x4005.C000

GPIO Port F (AHB) base: 0x4005.D000

GPIO Port G (AHB) base: 0x4005.E000

GPIO Port H (AHB) base: 0x4005.F000

GPIO Port J (AHB) base: 0x4006.0000

GPIO Port K (AHB) base: 0x4006.1000

GPIO Port L (AHB) base: 0x4006.2000

GPIO Port M (AHB) base: 0x4006.3000

GPIO Port N (AHB) base: 0x4006.4000

GPIO Port P (AHB) base: 0x4006.5000

GPIO Port Q (AHB) base: 0x4006.6000

Offset 0xFDC

Type RO, reset 0x0000.0000

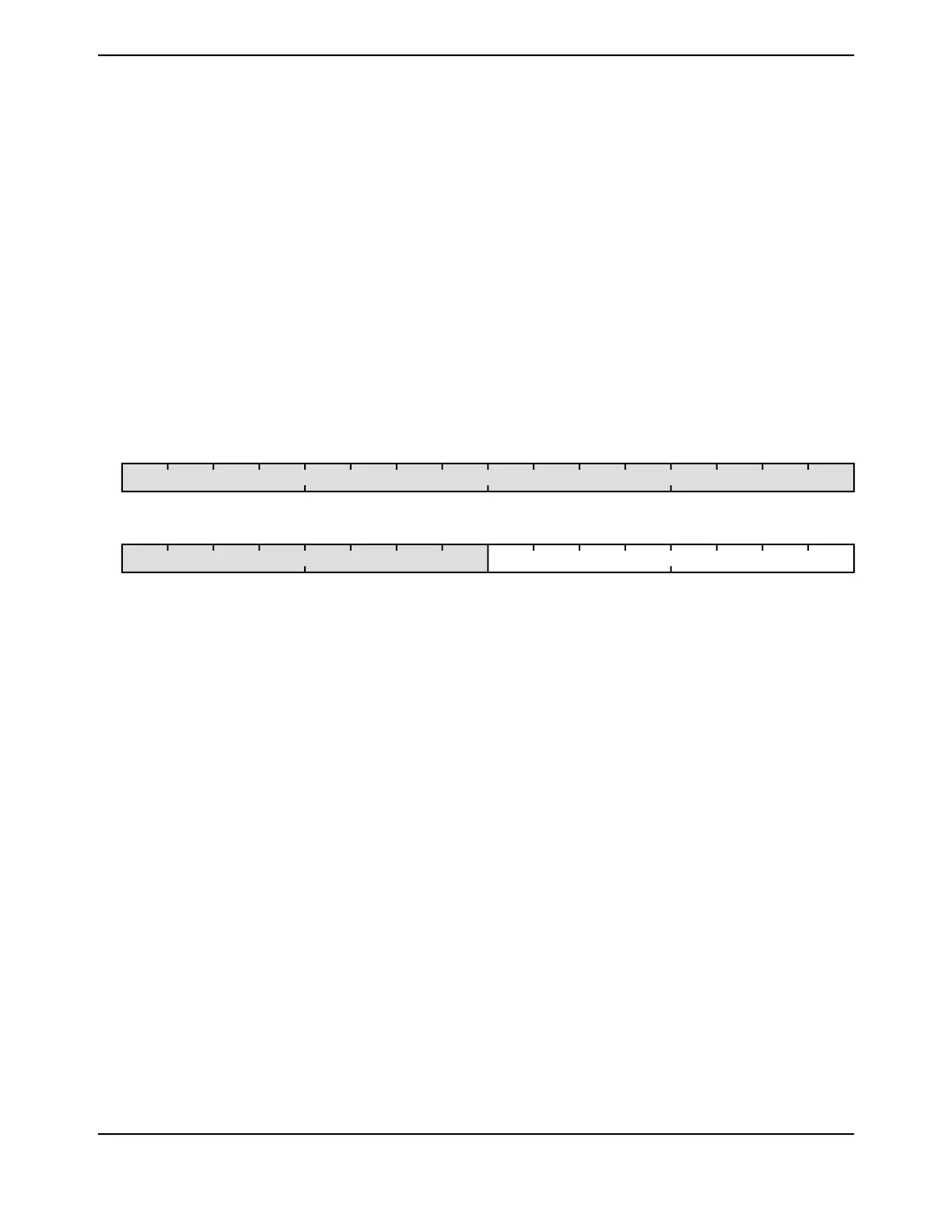

16171819202122232425262728293031

reserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

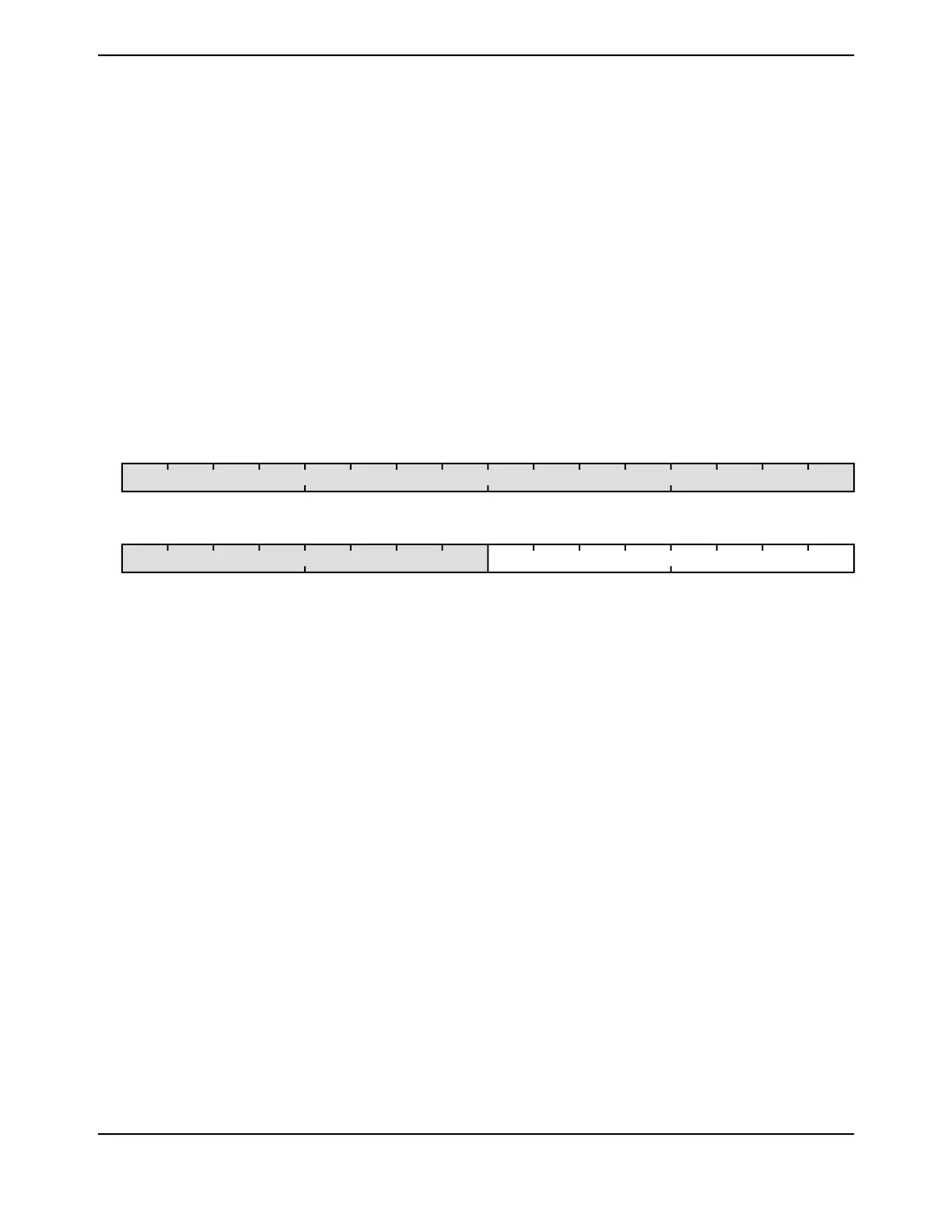

0123456789101112131415

PID7reserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0000.00ROreserved31:8

GPIO Peripheral ID Register [31:24]0x00ROPID77:0

June 18, 2014806

Texas Instruments-Production Data

General-Purpose Input/Outputs (GPIOs)

Loading...

Loading...