Register 10: DMA Channel Useburst Set (DMAUSEBURSTSET), offset 0x018

Each bit of the DMAUSEBURSTSET register represents the corresponding μDMA channel. Setting

a bit disables the channel's single request input from generating requests, configuring the channel

to only accept burst requests. Reading the register returns the status of USEBURST.

If the amount of data to transfer is a multiple of the arbitration (burst) size, the corresponding SET[n]

bit is cleared after completing the final transfer. If there are fewer items remaining to transfer than

the arbitration (burst) size, the μDMA controller automatically clears the corresponding SET[n] bit,

allowing the remaining items to transfer using single requests. In order to resume transfers using

burst requests, the corresponding bit must be set again. A bit should not be set if the corresponding

peripheral does not support the burst request model.

Refer to “Request Types” on page 682 for more details about request types.

DMA Channel Useburst Set (DMAUSEBURSTSET)

Base 0x400F.F000

Offset 0x018

Type RW, reset 0x0000.0000

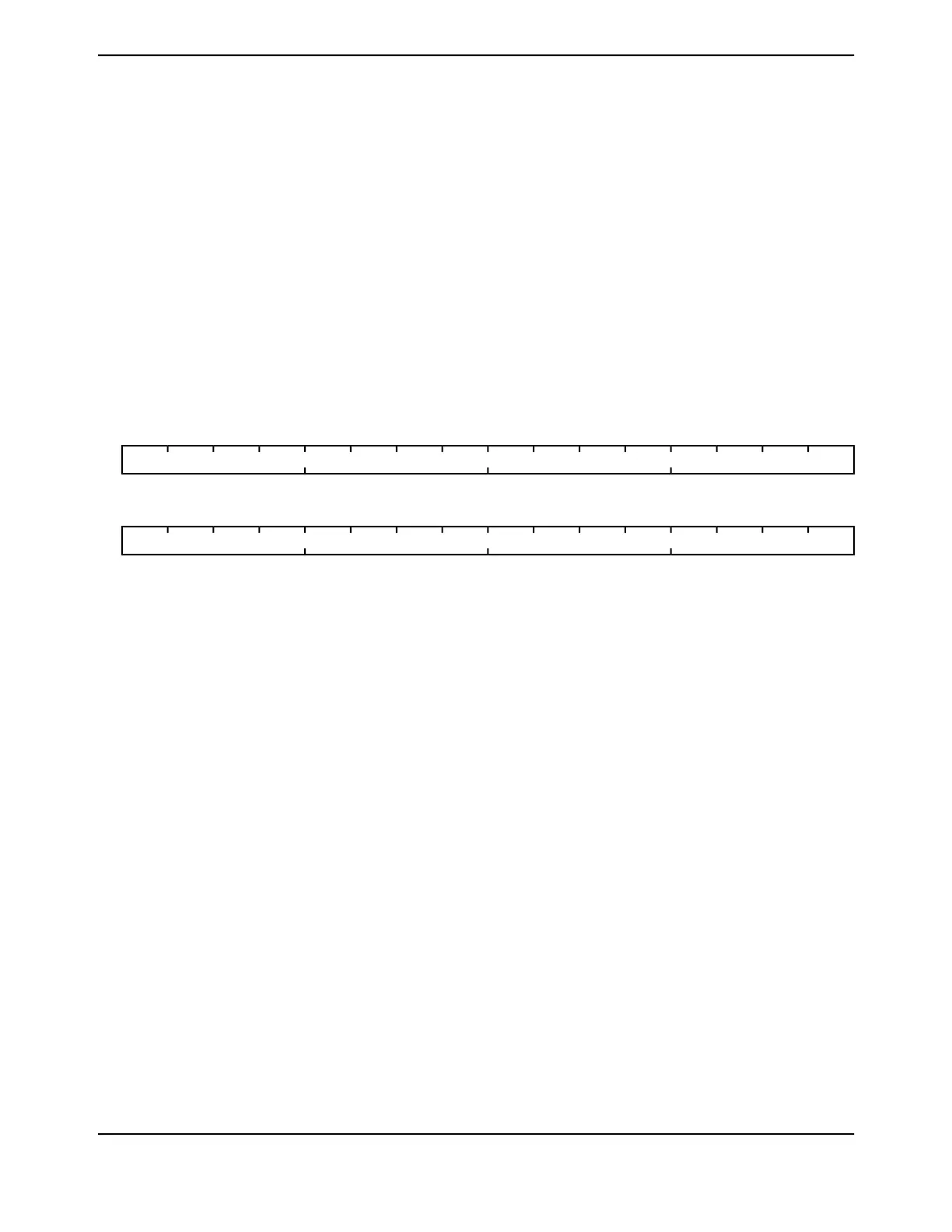

16171819202122232425262728293031

SET[n]

RWRWRWRWRWRWRWRWRWRWRWRWRWRWRWRWType

0000000000000000Reset

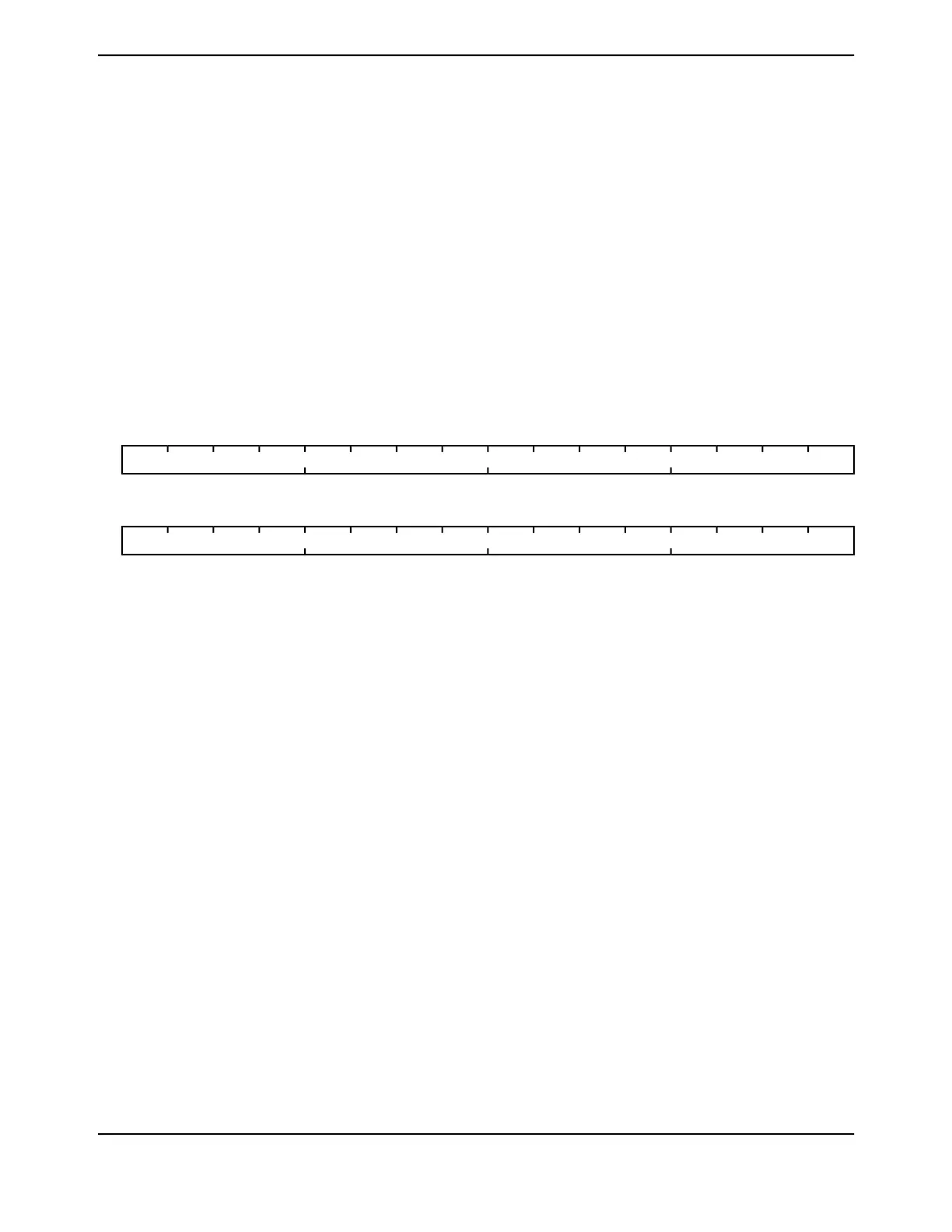

0123456789101112131415

SET[n]

RWRWRWRWRWRWRWRWRWRWRWRWRWRWRWRWType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

Channel [n] Useburst Set

DescriptionValue

μDMA channel [n] responds to single or burst requests.0

μDMA channel [n] responds only to burst requests.1

Bit 0 corresponds to channel 0. This bit is automatically cleared as

described above. A bit can also be manually cleared by setting the

corresponding CLR[n] bit in the DMAUSEBURSTCLR register.

0x0000.0000RWSET[n]31:0

717June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...