Register 4: CAN Bit Timing (CANBIT), offset 0x00C

This register is used to program the bit width and bit quantum. Values are programmed to the system

clock frequency. This register is write-enabled by setting the CCE and INIT bits in the CANCTL

register. See “Bit Time and Bit Rate” on page 1370 for more information.

CAN Bit Timing (CANBIT)

CAN0 base: 0x4004.0000

CAN1 base: 0x4004.1000

Offset 0x00C

Type RW, reset 0x0000.2301

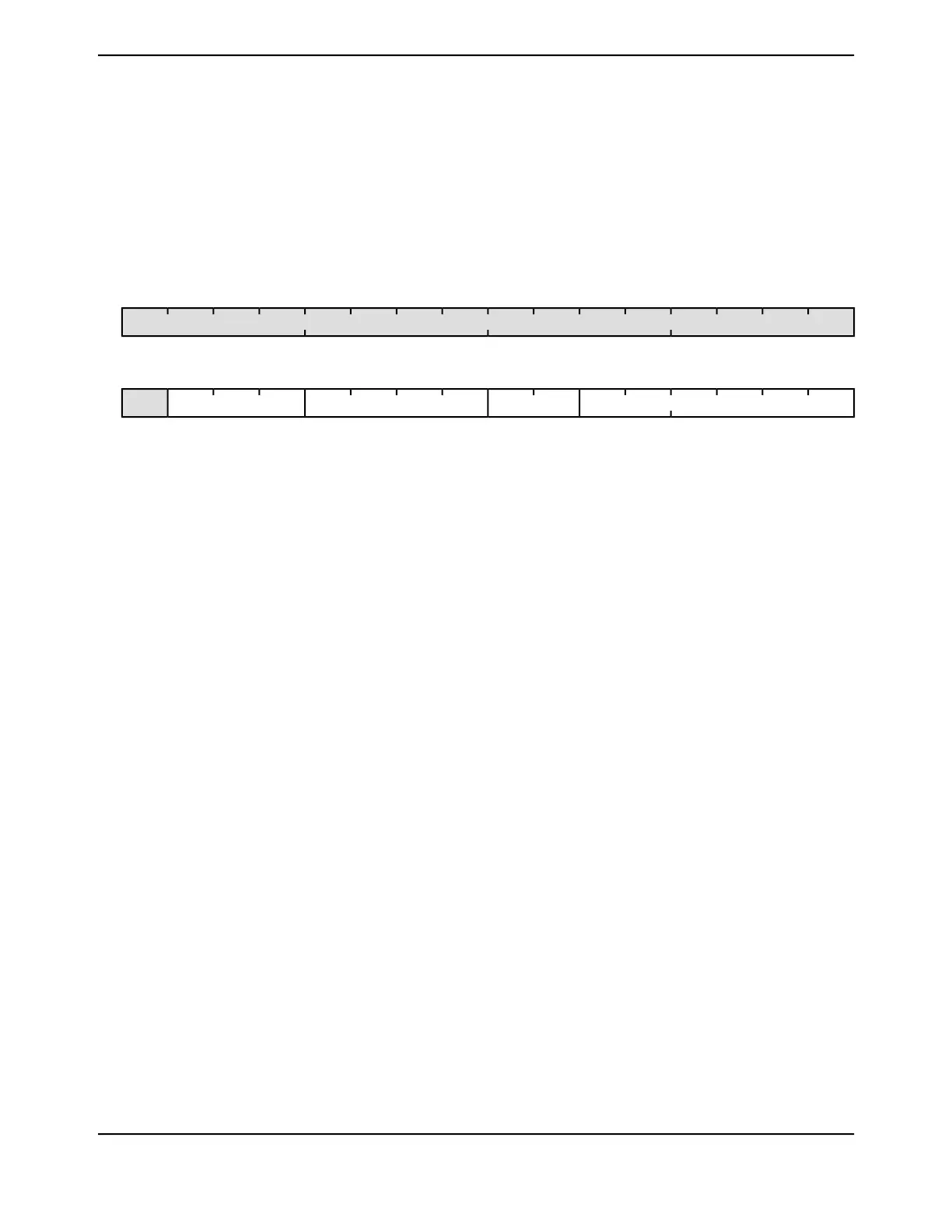

16171819202122232425262728293031

reserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

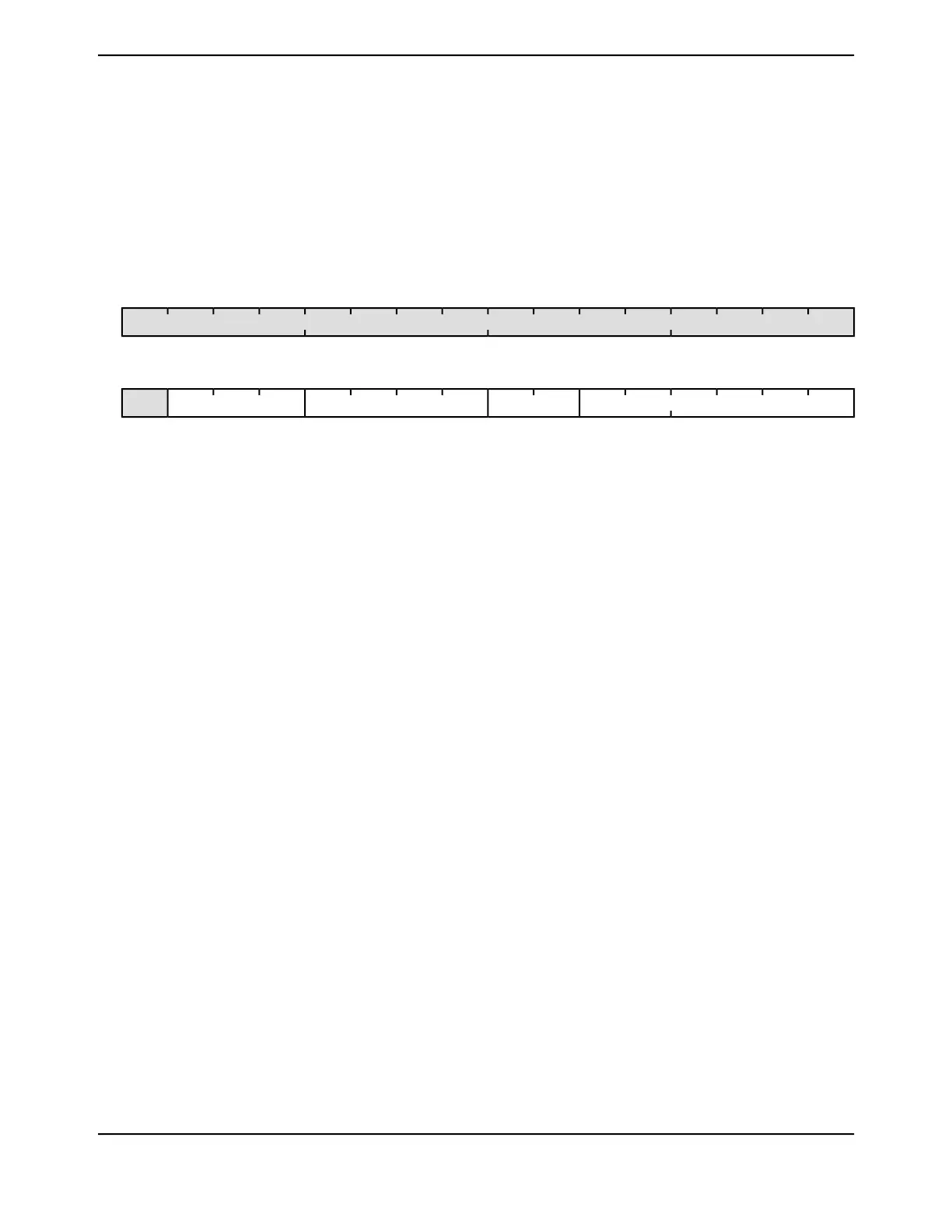

0123456789101112131415

BRPSJWTSEG1TSEG2reserved

RWRWRWRWRWRWRWRWRWRWRWRWRWRWRWROType

1000000011000100Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0000ROreserved31:15

Time Segment after Sample Point

0x00-0x07: The actual interpretation by the hardware of this value is

such that one more than the value programmed here is used.

So, for example, the reset value of 0x2 means that 3 (2+1) bit time

quanta are defined for Phase2 (see Figure 19-4 on page 1371). The bit

time quanta is defined by the BRP field.

0x2RWTSEG214:12

Time Segment Before Sample Point

0x00-0x0F: The actual interpretation by the hardware of this value is

such that one more than the value programmed here is used.

So, for example, the reset value of 0x3 means that 4 (3+1) bit time

quanta are defined for Phase1 (see Figure 19-4 on page 1371). The bit

time quanta is defined by the BRP field.

0x3RWTSEG111:8

(Re)Synchronization Jump Width

0x00-0x03: The actual interpretation by the hardware of this value is

such that one more than the value programmed here is used.

During the start of frame (SOF), if the CAN controller detects a phase

error (misalignment), it can adjust the length of TSEG2 or TSEG1 by the

value in SJW. So the reset value of 0 adjusts the length by 1 bit time

quanta.

0x0RWSJW7:6

Baud Rate Prescaler

The value by which the oscillator frequency is divided for generating the

bit time quanta. The bit time is built up from a multiple of this quantum.

0x00-0x03F: The actual interpretation by the hardware of this value is

such that one more than the value programmed here is used.

BRP defines the number of CAN clock periods that make up 1 bit time

quanta, so the reset value is 2 bit time quanta (1+1).

The CANBRPE register can be used to further divide the bit time.

0x1RWBRP5:0

June 18, 20141384

Texas Instruments-Production Data

Controller Area Network (CAN) Module

Loading...

Loading...