Register 14: Deep Sleep Clock Configuration Register (DSCLKCFG), offset

0x144

The DSCLKCFG register specifies the behavior of the clock system while in deep sleep.

Note that the MOSCDPD bit not only affects deep-sleep mode, but all other modes as well depending

on the value of the bit. Please refer to the following table when programming this bit:

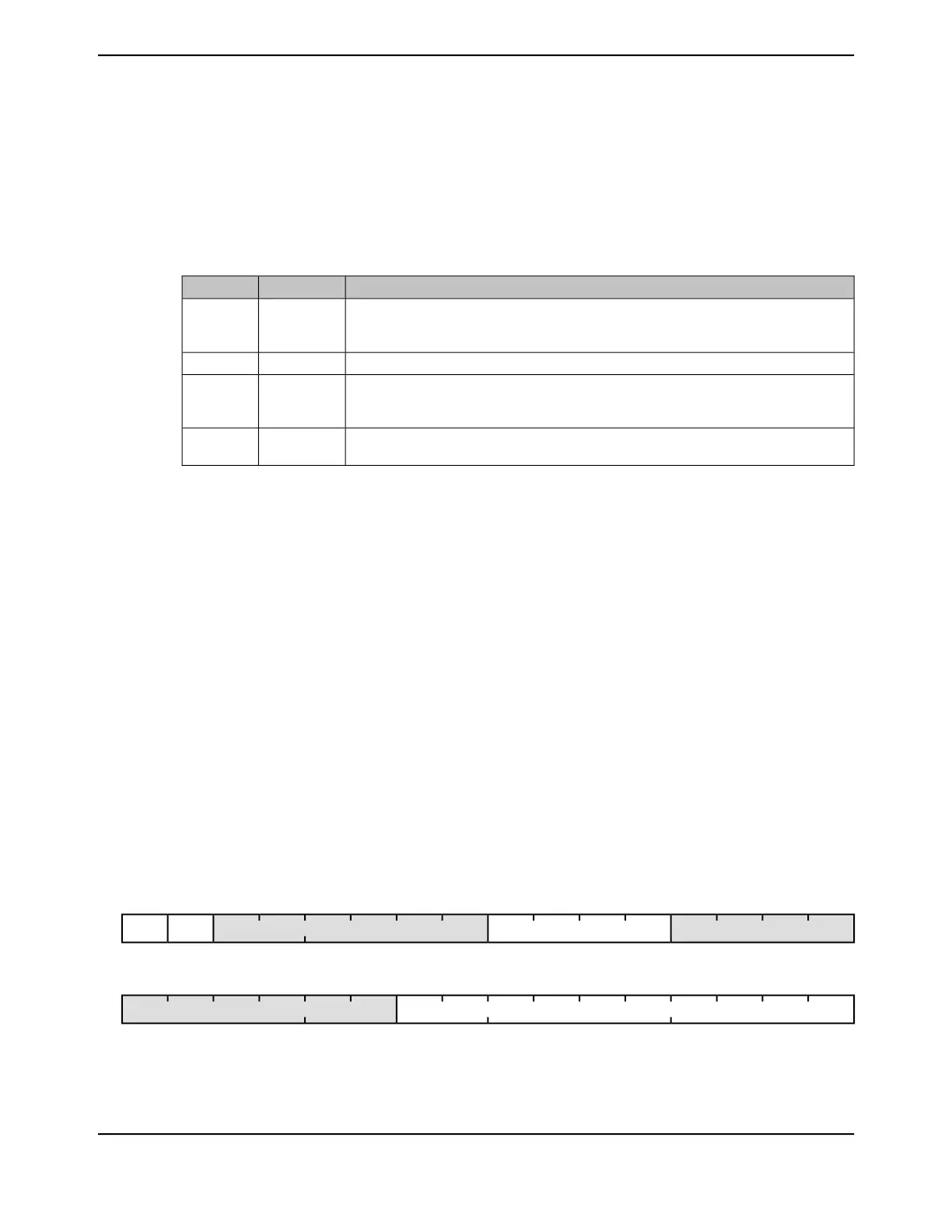

Table 5-13. MOSC Configurations

ResultMOSCDPD fieldPWRDN bit

MOSC is powered ON in run and sleep modes, but is disabled in accidental power down,

when the PWRDN bit is set in the MOSCCTL register, or in deep-sleep mode only if it is not

the deep-sleep clock source (DSOSCSRC !==0x3).

00

MOSC is powered and running in run, sleep and deep-sleep modes.10

MOSC is powered off, and does not run in any mode. Please note, that in this configuration,

when the MOSC is disabled, the MOSC must not be chosen as a clock source or indeterminate

results occur.

01

MOSC runs and does not disable itself in run, sleep, and deep-sleep modes regardless of

the fact that the PWRDN bit is set.

11

Note: The MOSCDPD bit has an effect in all modes of operation

Note: If the MOSC is chosen as the Deep-Sleep clock source in the DSCLKCFG register, the

MOSC must also be configured as the Run and Sleep clock source in the RSCLKCFG

register prior to entering Deep Sleep. If the PIOSC, LFIOSC, or Hibernation RTC Module

Oscillator (HIBLFIOSC or 32-kHz crystal) is configured as the Run and Sleep clock source

in the RSCLKFCFG register, and the MOSC is configured as the Deep-Sleep clock source

in the DSCLKCFG register, then two outcomes are possible:

■ If the PIOSC is still powered in Deep Sleep (using the PIOSCPD bit in the DSCLKCFG

register) then the PIOSC is utilized as the clock source when entering Deep Sleep and

the device enters and exits the Deep-Sleep state normally. The MOSC is not used as

the clock source in Deep Sleep.

■ If the PIOSC has been configured to be powered down in Deep Sleep, then the device

can enter the Deep-Sleep state, but cannot exit properly. This situation can be avoided

by programming the MOSC as the Run and Sleep clock source in the RSCLKCFG

register prior to entering Deep Sleep.

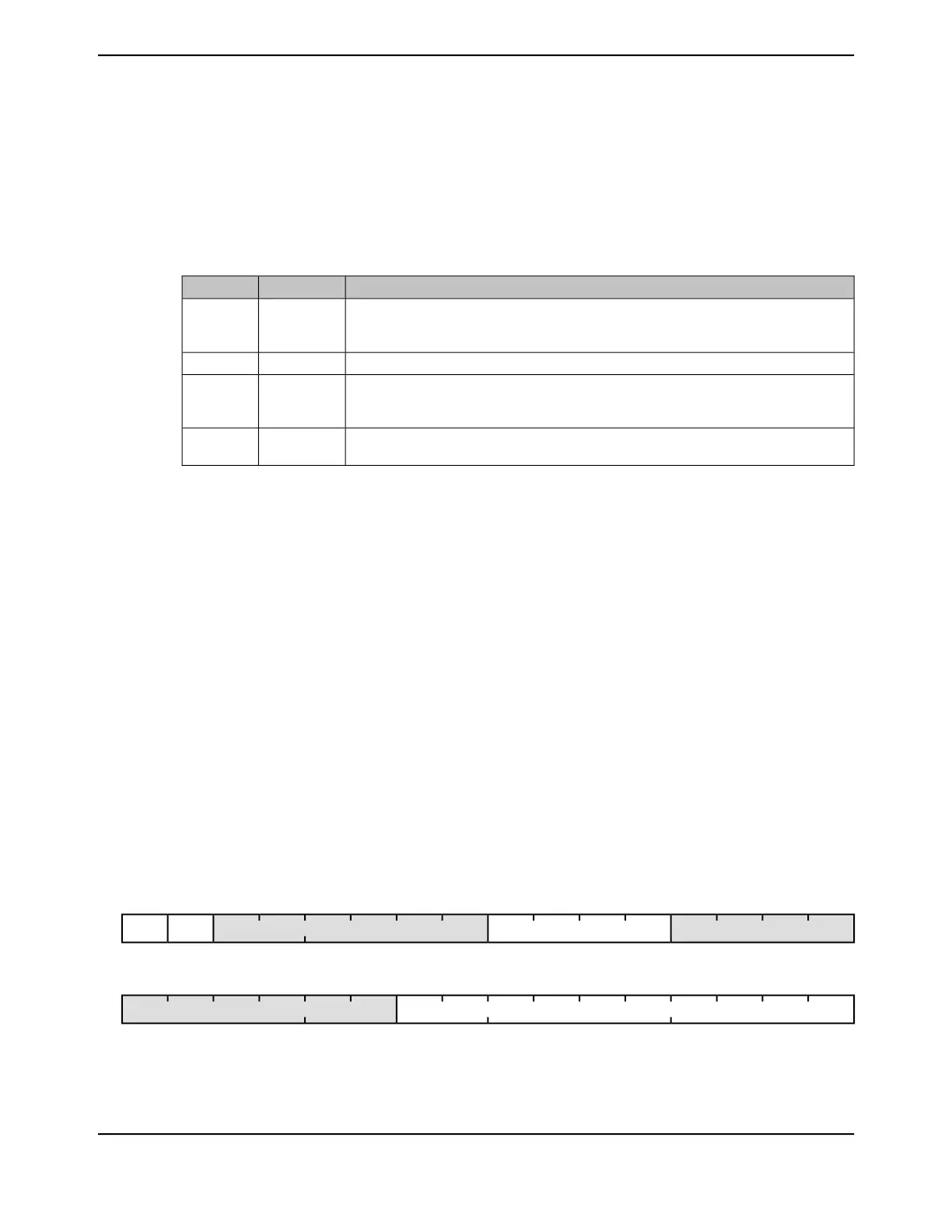

Deep Sleep Clock Configuration Register (DSCLKCFG)

Base 0x400F.E000

Offset 0x144

Type RW, reset 0x0000.0000

16171819202122232425262728293031

reservedDSOSCSRCreservedMOSCDPDPIOSCPD

RORORORORWRWRWRWRORORORORORORWRWType

0000000000000000Reset

0123456789101112131415

DSSYSDIVreserved

RWRWRWRWRWRWRWRWRWRWROROROROROROType

0000000000000000Reset

281June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...