Register 25: I

2

C FIFO Status (I2CFIFOSTATUS), offset 0xF08

This register contains the real-time status of the RX and TX FIFOs.

I2C FIFO Status (I2CFIFOSTATUS)

I2C 0 base: 0x4002.0000

I2C 1 base: 0x4002.1000

I2C 2 base: 0x4002.2000

I2C 3 base: 0x4002.3000

I2C 4 base: 0x400C.0000

I2C 5 base: 0x400C.1000

I2C 6 base: 0x400C.2000

I2C 7 base: 0x400C.3000

I2C 8 base: 0x400B.8000

I2C 9 base: 0x400B.9000

Offset 0xF08

Type RO, reset 0x0001.0005

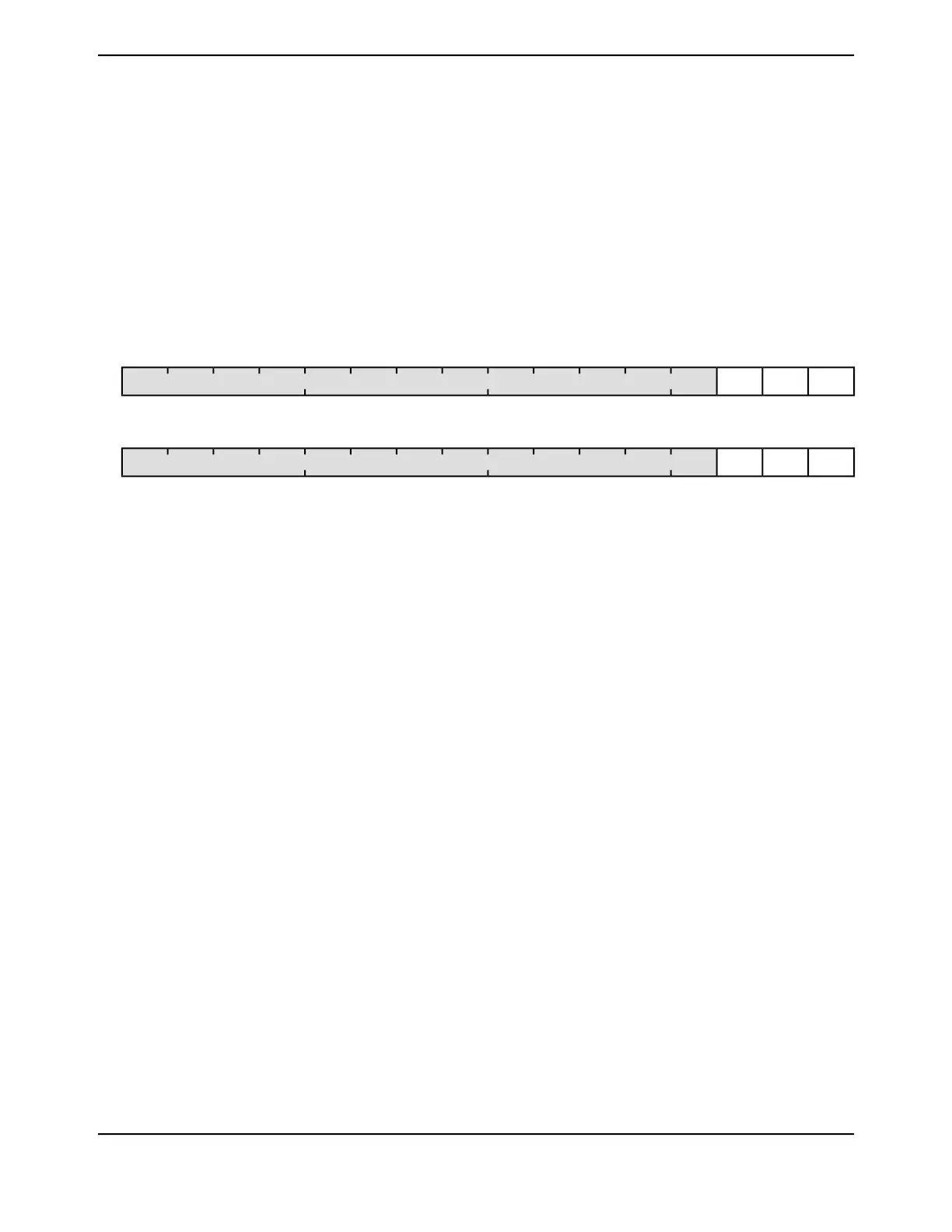

16171819202122232425262728293031

RXFERXFF

RXABVTRIG

reserved

ROROROROROROROROROROROROROROROROType

1000000000000000Reset

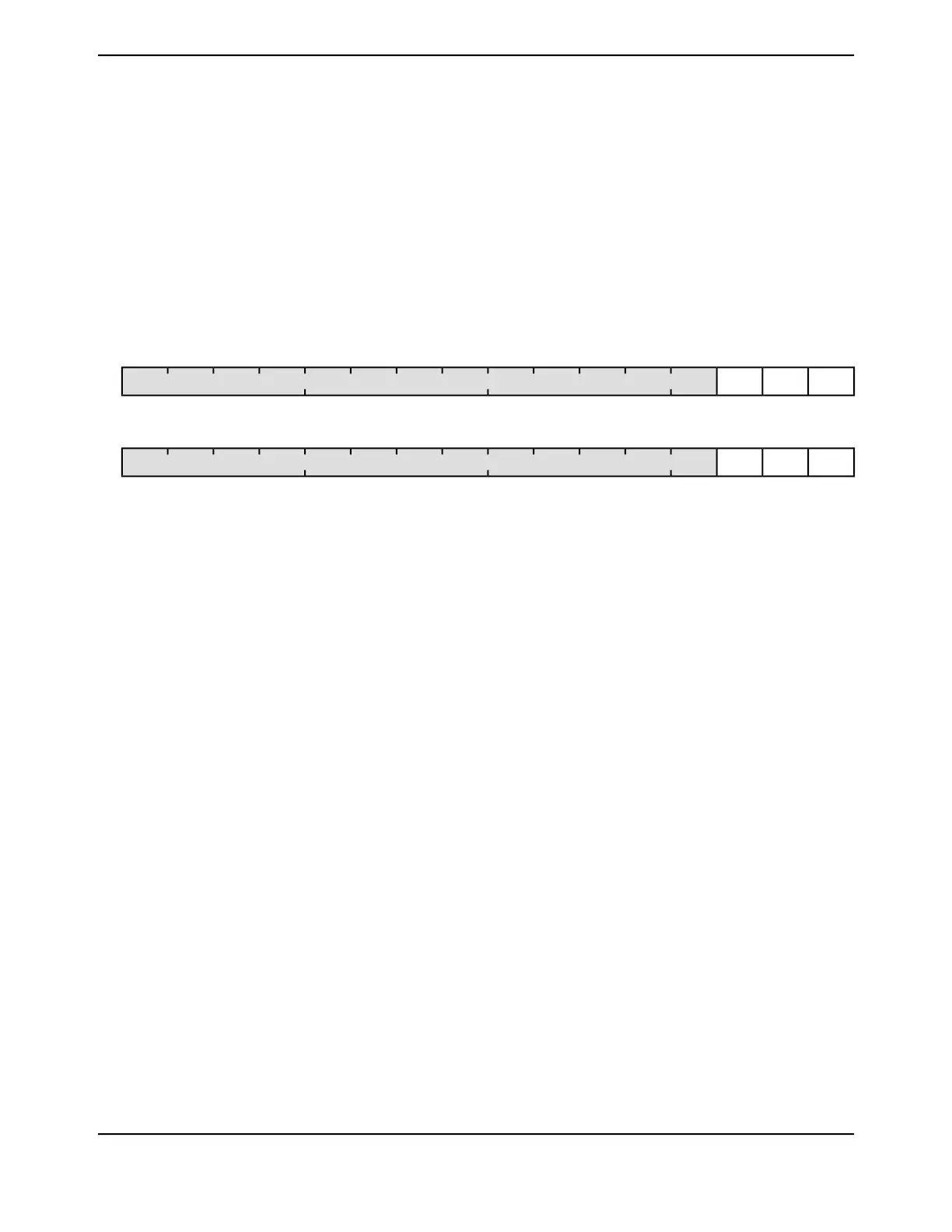

0123456789101112131415

TXFETXFF

TXBLWTRIG

reserved

ROROROROROROROROROROROROROROROROType

1010000000000000Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x000ROreserved31:19

RX FIFO Above Trigger Level

DescriptionValue

The number of bytes in RX FIFO is below the trigger level

programmed by the RXTRIG bit in the I2CFIFOCTL register

0

The number of bytes in the RX FIFO is above the trigger level

programmed by the RXTRIG bit in the I2CFIFOCTL register

1

0RORXABVTRIG18

RX FIFO Full

DescriptionValue

The RX FIFO is not full.0

The RX FIFO is full.1

0RORXFF17

RX FIFO Empty

DescriptionValue

The RX FIFO is not empty.0

The RX FIFO is empty.1

1RORXFE16

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x000ROreserved15:3

June 18, 20141352

Texas Instruments-Production Data

Inter-Integrated Circuit (I

2

C) Interface

Loading...

Loading...