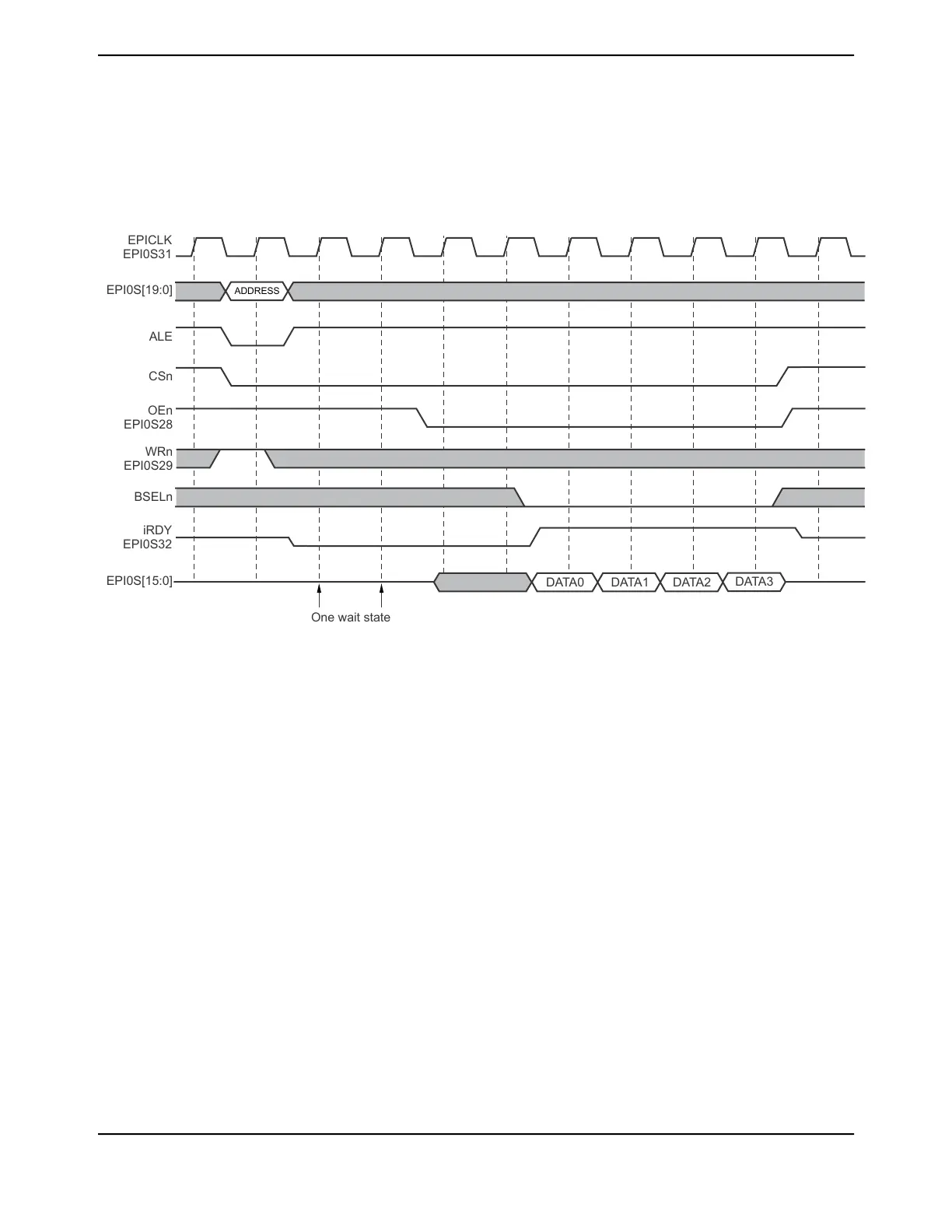

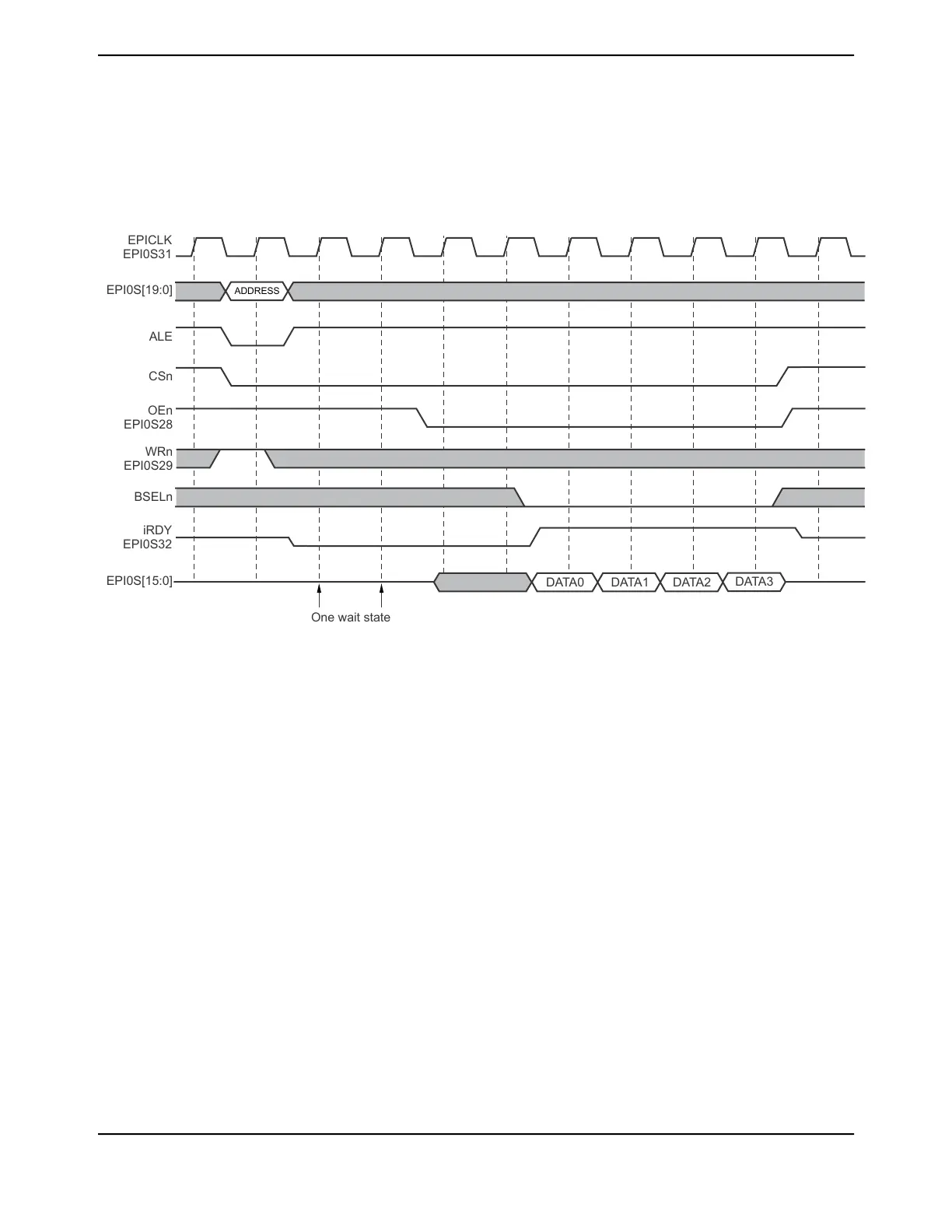

Note that if a read or write transfer attempts to begin during a refresh event, the transfer is held off

by the assertion of the iRDY pin by the memory to the EPI module. Figure 11-9 on page 840 and

Figure 11-10 on page 841 depict the delay in data transfer during a refresh collision.

Figure 11-9. Read Delay During Refresh Event

DATA0 DATA1 DATA2

DATA3

ADDRESS

BSELn

EPICLK

EPI0S31

EPI0S[19:0]

ALE

CSn

OEn

EPI0S28

WRn

EPI0S29

iRDY

EPI0S32

EPI0S[15:0]

One wait state

June 18, 2014840

Texas Instruments-Production Data

External Peripheral Interface (EPI)

Loading...

Loading...