2.3.5 Exceptions and Interrupts

The Cortex-M4F processor supports interrupts and system exceptions. The processor and the

Nested Vectored Interrupt Controller (NVIC) prioritize and handle all exceptions. An exception

changes the normal flow of software control. The processor uses Handler mode to handle all

exceptions except for reset. See “Exception Entry and Return” on page 120 for more information.

The NVIC registers control interrupt handling. See “Nested Vectored Interrupt Controller

(NVIC)” on page 136 for more information.

2.3.6 Data Types

The Cortex-M4F supports 32-bit words, 16-bit halfwords, and 8-bit bytes. The processor also supports

64-bit data transfer instructions. All instruction and data memory accesses are little endian. See

“Memory Regions, Types and Attributes” on page 106 for more information.

2.4 Memory Model

This section describes the processor memory map, the behavior of memory accesses, and the

bit-banding features. The processor has a fixed memory map that provides up to 4 GB of addressable

memory.

The memory map for the TM4C1294NCPDT controller is provided in Table 2-4 on page 103. In this

manual, register addresses are given as a hexadecimal increment, relative to the module's base

address as shown in the memory map.

The regions for SRAM and peripherals include bit-band regions. Bit-banding provides atomic

operations to bit data (see “Bit-Banding” on page 109).

The processor reserves regions of the Private peripheral bus (PPB) address range for core peripheral

registers (see “Cortex-M4 Peripherals” on page 134).

Note: Within the memory map, attempts to read or write addresses in reserved spaces result in

a bus fault. In addition, attempts to write addresses in the flash range also result in a bus

fault.

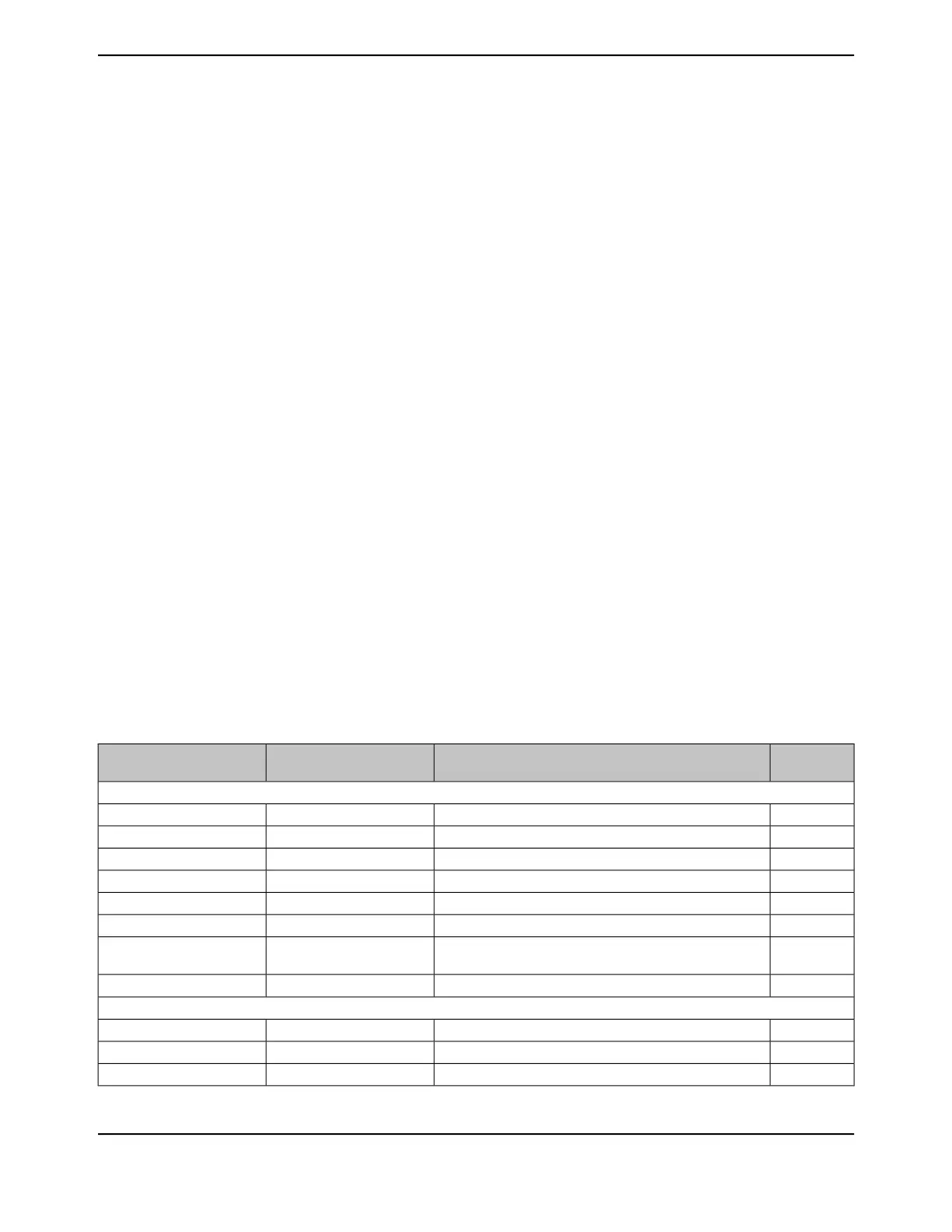

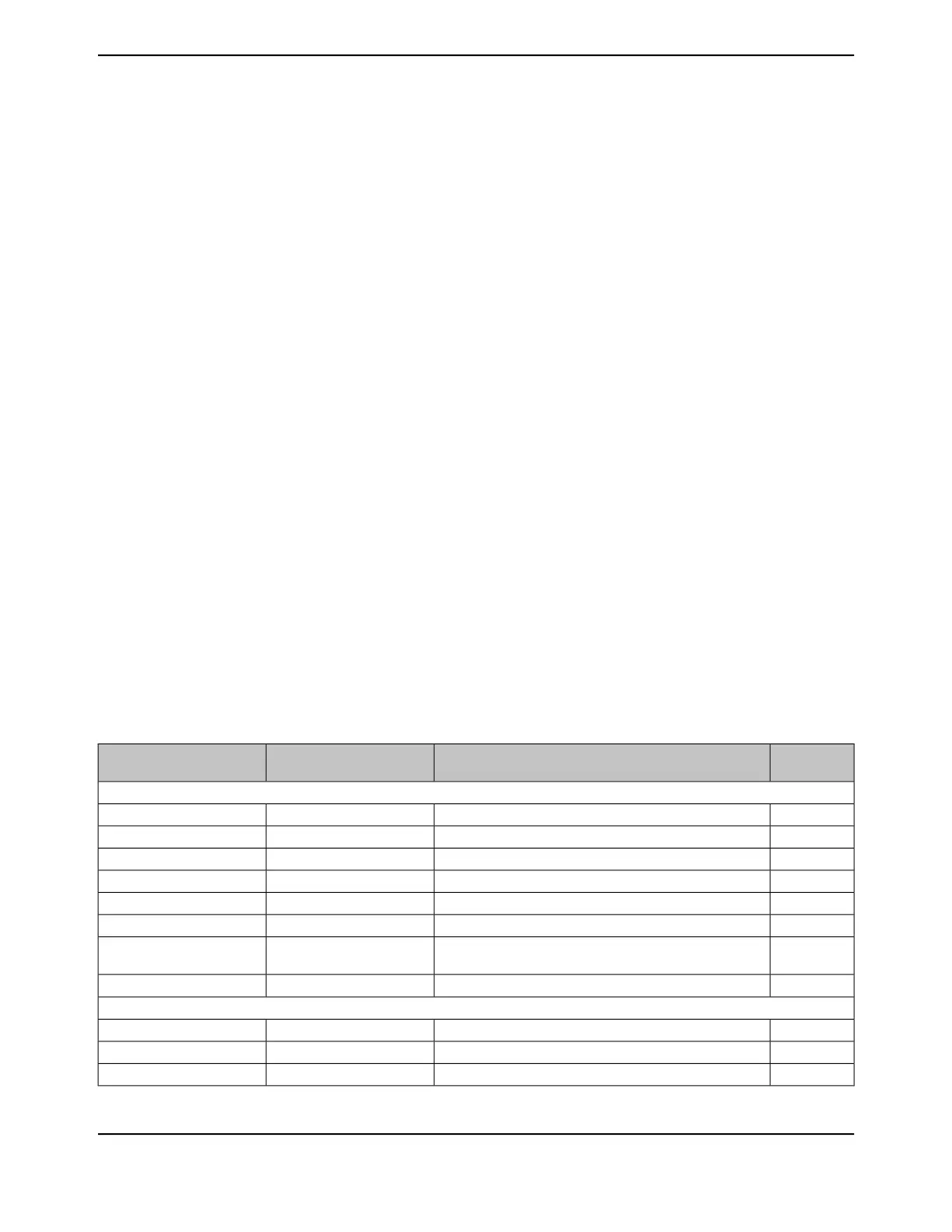

Table 2-4. Memory Map

For details,

see page ...

DescriptionEndStart

Memory

621On-chip Flash0x000F.FFFF0x0000.0000

-Reserved0x01FF.FFFF0x0010.0000

602On-chip ROM (16 MB)0x02FF.FFFF0x0200.0000

-Reserved0x1FFF.FFFF0x0300.0000

602Bit-banded on-chip SRAM0x2006.FFFF0x2000.0000

-Reserved0x21FF.FFFF0x2007.0000

602Bit-band alias of bit-banded on-chip SRAM starting at

0x2000.0000

0x2234.FFFF0x2200.0000

-

Reserved0x3FFF.FFFF0x2235.0000

Peripherals

1030Watchdog timer 00x4000.0FFF0x4000.0000

1030Watchdog timer 10x4000.1FFF0x4000.1000

-Reserved0x4000.3FFF0x4000.2000

103June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...