3. Read the PRETRY and ERETRY bits in the EEPROM Support Control and Status (EESUPP)

register. If either of the bits are set, return an error, else continue.

4. Reset the EEPROM module using the EEPROM Software Reset (SREEPROM) register at

offset 0x558 in the System Control register space.

5. Insert delay (6 cycles plus function call overhead).

6. Poll the WORKING bit in the EEPROM Done Status (EEDONE) register to determine when it is

clear. When WORKING=0, continue.

7. Read the PRETRY and ERETRY bits in the EESUPP register. If either of the bits are set, return

an error, else the EEPROM initialization is complete and software may use the peripheral as

normal.

Important: Failure to perform these initialization steps after a reset may lead to incorrect operation

or permanent data loss if the EEPROM is later written.

If the PRETRY or ERETRY bits are set in the ESUPP register, the EEPROM was unable

to recover its state. If power is stable when this occurs, this indicates a fatal error and

is likely an indication that the EEPROM memory has exceeded its specified lifetime

write/erase specification. If the supply voltage is unstable when this return code is

observed, retrying the operation once the voltage is stabilized may clear the error.

The EEPROM initialization function code is named EEPROMinit( ) in TivaWare, which can be

downloaded from http://www.ti.com/tivaware.

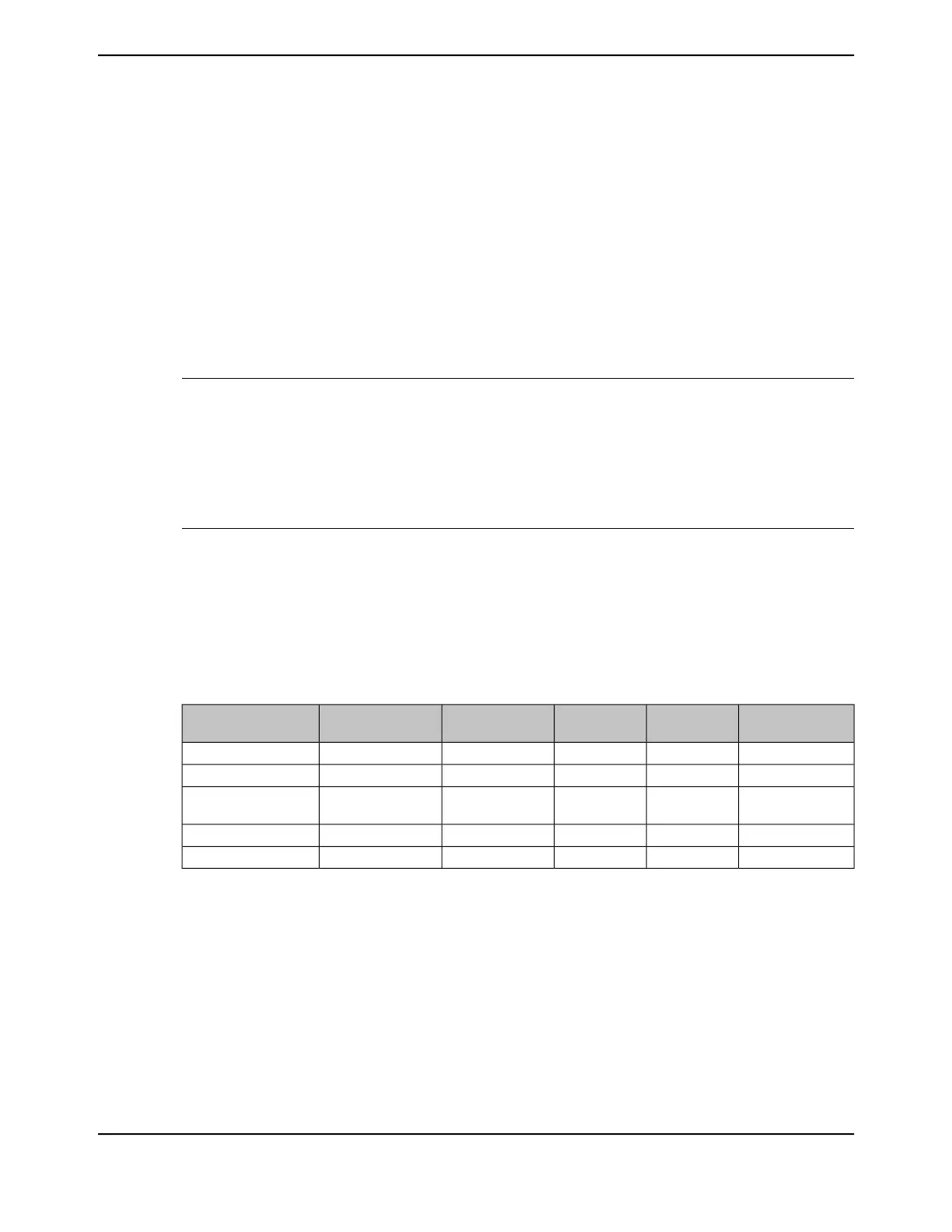

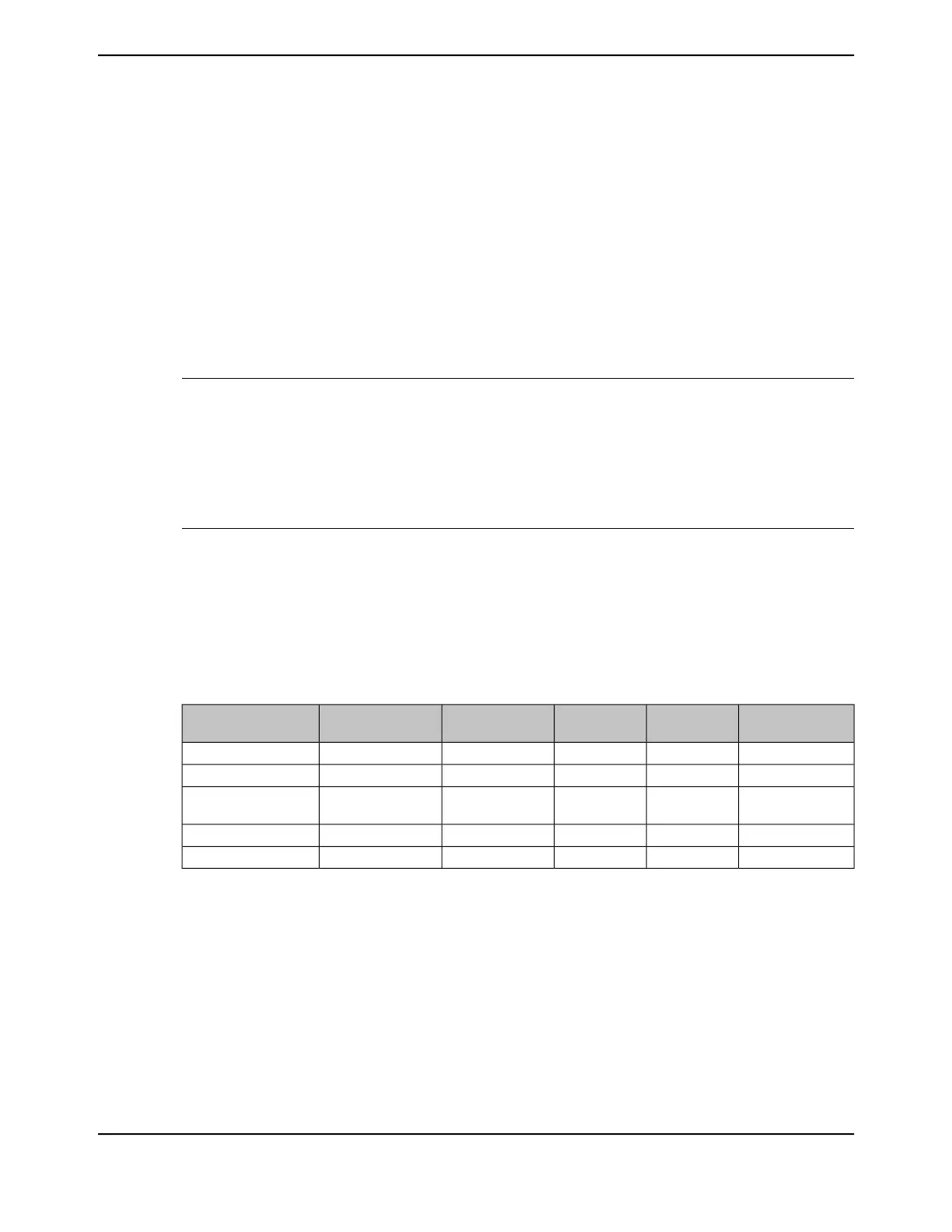

8.2.5 Bus Matrix Memory Accesses

The following table identifies the Bus Masters and their access to the various memories on the bus

matrix.

Table 8-5. Master Memory Access Availability

External Memory

Access (via EPI)

EEPROM

Access

SRAM AccessROM AccessFlash AccessMaster

YesYesYesYes (read-only)YesCPU Instruction Bus

YesYes-Yes (read-only)YesCPU Data Bus

YesYesYes-Yes (read-only,

Run-Mode-only)

µDMA

--Yes--Ethernet Module

--Yes--USB

8.3 Register Map

Table 8-6 on page 622 lists the ROM Controller register and the Flash memory control registers. The

offset listed is a hexadecimal increment to the register's address. The Flash memory register offsets

are relative to the Flash memory control base address of 0x400F.D000. The EEPROM registers

are relative to the EEPROM base address of 0x400A.F000. The ROM control and Flash memory

protection register offsets are relative to the System Control base address of 0x400F.E000.

621June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...