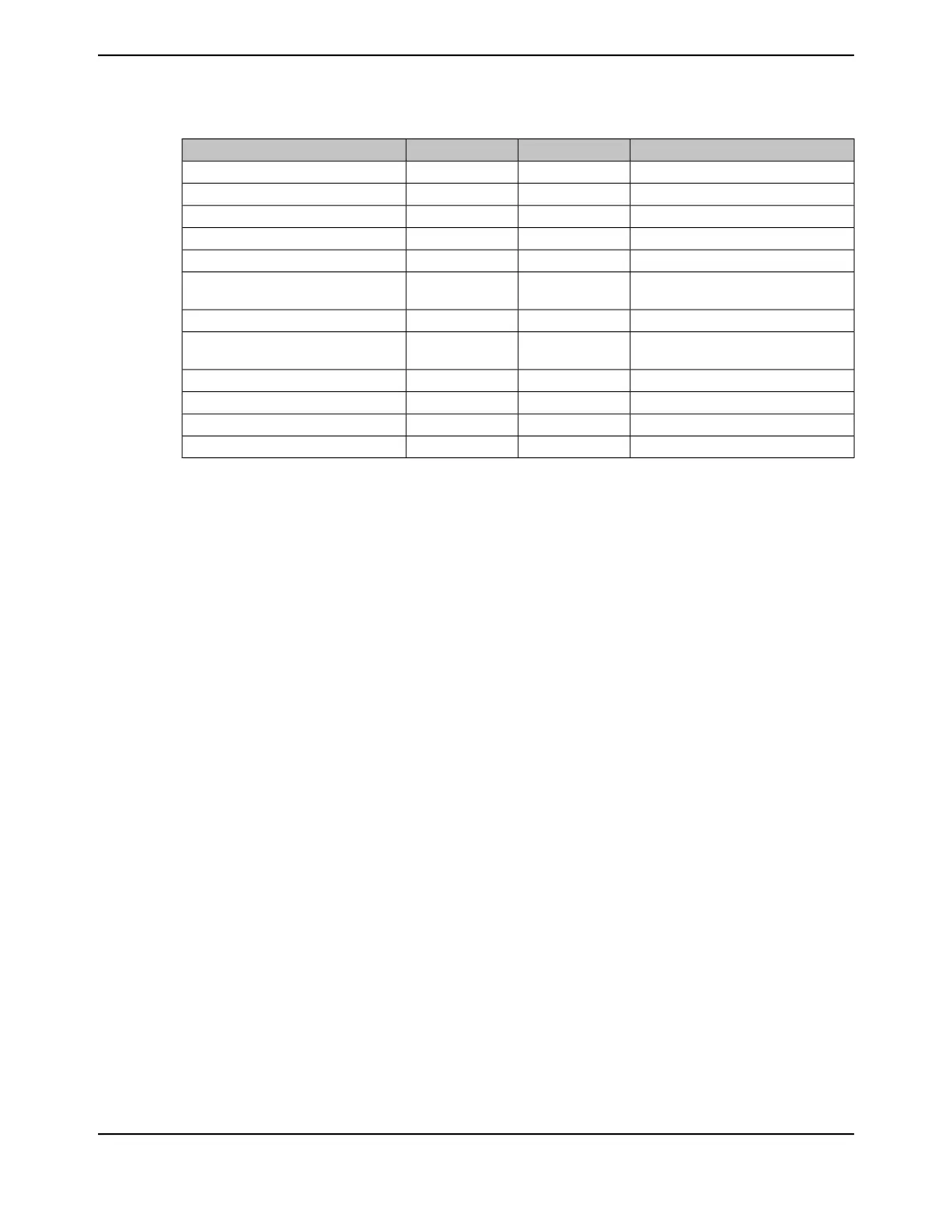

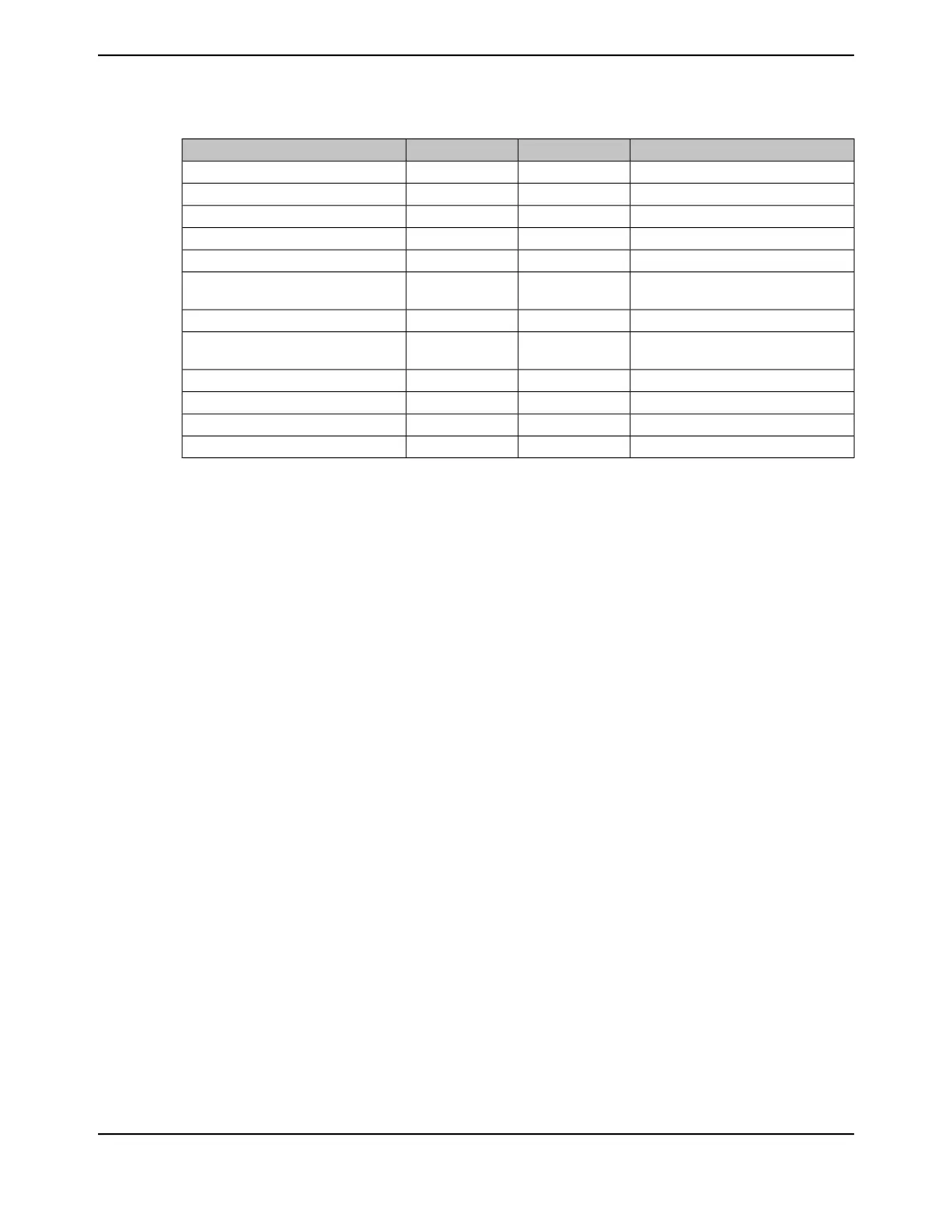

Table 9-8. Channel Control Word Configuration for Memory Transfer Example

DescriptionValueBitsField in DMACHCTL

32-bit destination address increment231:30DSTINC

32-bit destination data size229:28DSTSIZE

32-bit source address increment227:26SRCINC

32-bit source data size225:24SRCSIZE

Reserved023:22reserved

Privileged access protection for

destination data writes

021DSTPROT0

Reserved020:19reserved

Privileged access protection for source

data reads

018SRCPROT0

Arbitrates after 8 transfers317:14ARBSIZE

Transfer 256 items25513:4XFERSIZE

N/A for this transfer type03NXTUSEBURST

Use Auto-request transfer mode22:0XFERMODE

Configure Peripheral Interrupts

For memory-to-memory transfers, the peripheral involved must be configured to generate an interrupt

when the µDMA has completed its transfer. Upon completion, the µDMA will send a dma_done

signal to the peripheral.

9.3.2.3 Start the Transfer

Now the channel is configured and is ready to start.

1. Enable the channel by setting bit 30 of the DMA Channel Enable Set (DMAENASET) register.

2. Issue a transfer request by setting bit 30 of the DMA Channel Software Request (DMASWREQ)

register.

The μDMA transfer begins. If the interrupt is enabled, then the processor is notified by interrupt

when the transfer is complete. If needed, the status can be checked by reading bit 30 of the

DMAENASET register. This bit is automatically cleared when the transfer is complete. The status

can also be checked by reading the XFERMODE field of the channel control word at offset 0x1E8.

This field is automatically cleared at the end of the transfer.

9.3.3 Configuring a Peripheral for Simple Transmit

This example configures the μDMA controller to transmit a buffer of data to a peripheral. The

peripheral has a transmit FIFO with a trigger level of 4. The example peripheral uses μDMA channel

7.

9.3.3.1 Configure the Channel Attributes

First, configure the channel attributes:

1. Configure bit 7 of the DMA Channel Priority Set (DMAPRIOSET) or DMA Channel Priority

Clear (DMAPRIOCLR) registers to set the channel to High priority or Default priority.

2. Set bit 7 of the DMA Channel Primary Alternate Clear (DMAALTCLR) register to select the

primary channel control structure for this transfer.

June 18, 2014696

Texas Instruments-Production Data

Micro Direct Memory Access (μDMA)

Loading...

Loading...