Register 33: EPI Error and Interrupt Status and Clear (EPIEISC), offset 0x21C

This register is used to clear a pending error interrupt. Clearing any defined bit in the EPIEISC has

no effect; setting a bit clears the error source and the raw error returns to 0. When any of bits[2:0]

of this register are read as set, it indicates that the ERRRIS bit in the EPIRIS register is set and an

EPI controller error is sent to the interrupt controller if the ERIM bit in the EPIIM register is set. If

any of bits [2:0] are written as 1, the register bit being written to, as well as the ERRIS bit in the

EPIRIS register and the ERIM bit in the EPIIM register are cleared.If the DMAWRIC or DMARDIC bit

in this register is set, then the corresponding bit in the EPIRIS and EPIMIS register is cleared. Note

that writing to this register and reading back immediately (pipelined by the processor) returns the

old register contents. One cycle is needed between write and read.

EPI Error and Interrupt Status and Clear (EPIEISC)

Base 0x400D.0000

Offset 0x21C

Type RW1C, reset 0x0000.0000

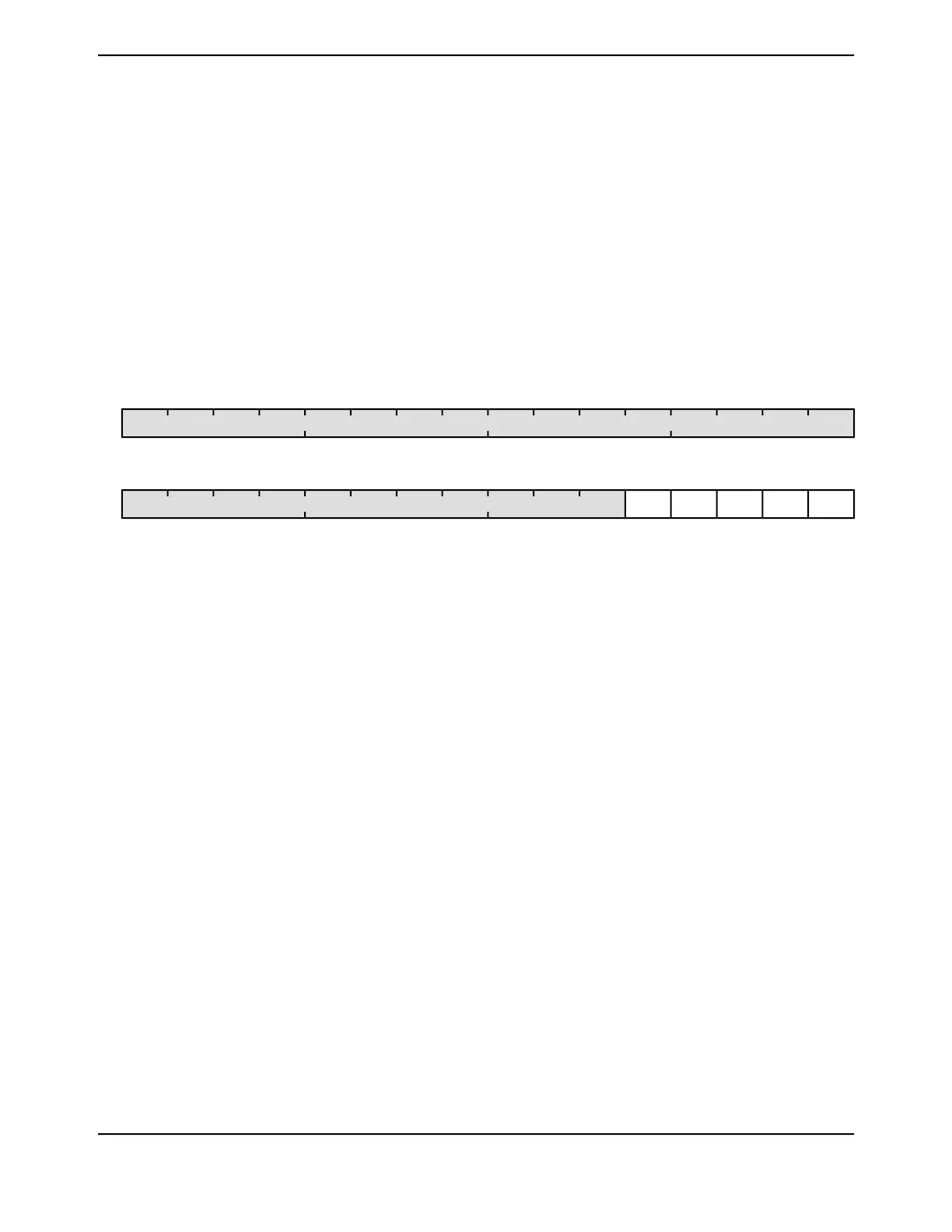

16171819202122232425262728293031

reserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

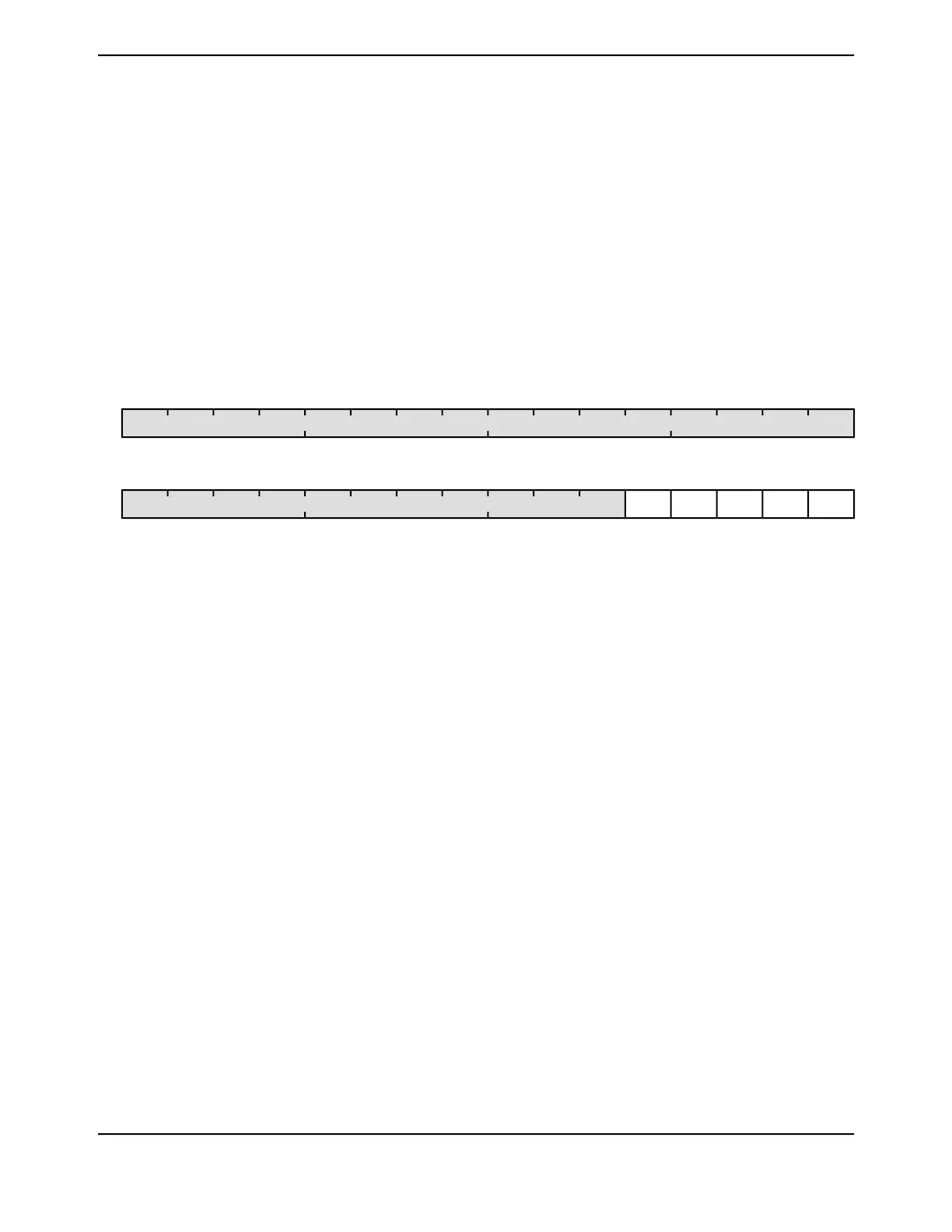

0123456789101112131415

TOUTRSTALLWTFULLDMARDICDMAWRICreserved

RW1CRW1CRW1CW1CW1CROROROROROROROROROROROType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x000ROreserved31:5

Write uDMA Interrupt Clear

Writing a 1 to this bit clears the DMAWRRIS bit in the EPIRIS register

and the DMAWRMIS bit in the EPIMIS register.

0W1CDMAWRIC4

Read uDMA Interrupt Clear

Writing a 1 to this bit clears the DMARDRIS bit in the EPIRIS register

and the DMARDMIS bit in the EPIMIS register.

0W1CDMARDIC3

Write FIFO Full Error

DescriptionValue

The WFERR bit is not enabled or no writes are stalled.0

The WFERR bit is enabled and a write is stalled due to the WFIFO

being full.

1

Writing a 1 to this bit clears it, as well as the ERRRIS and ERIM bits.

0RW1CWTFULL2

Read Stalled Error

DescriptionValue

The RSERR bit is not enabled or no pending reads are stalled.0

The RSERR bit is enabled and a pending read is stalled due to

writes in the WFIFO.

1

Writing a 1 to this bit clears it, as well as the ERRRIS and ERIM bits.

0RW1CRSTALL1

913June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...