Control (CPAC) register. The below example code sequence enables the FPU in both privileged

and user modes.

; CPACR is located at address 0xE000ED88

LDR.W R0, =0xE000ED88

; Read CPACR

LDR R1, [R0]

; Set bits 20-23 to enable CP10 and CP11 coprocessors

ORR R1, R1, #(0xF << 20)

; Write back the modified value to the CPACR

STR R1, [R0]; wait for store to complete

DSB

;reset pipeline now the FPU is enabled

ISB

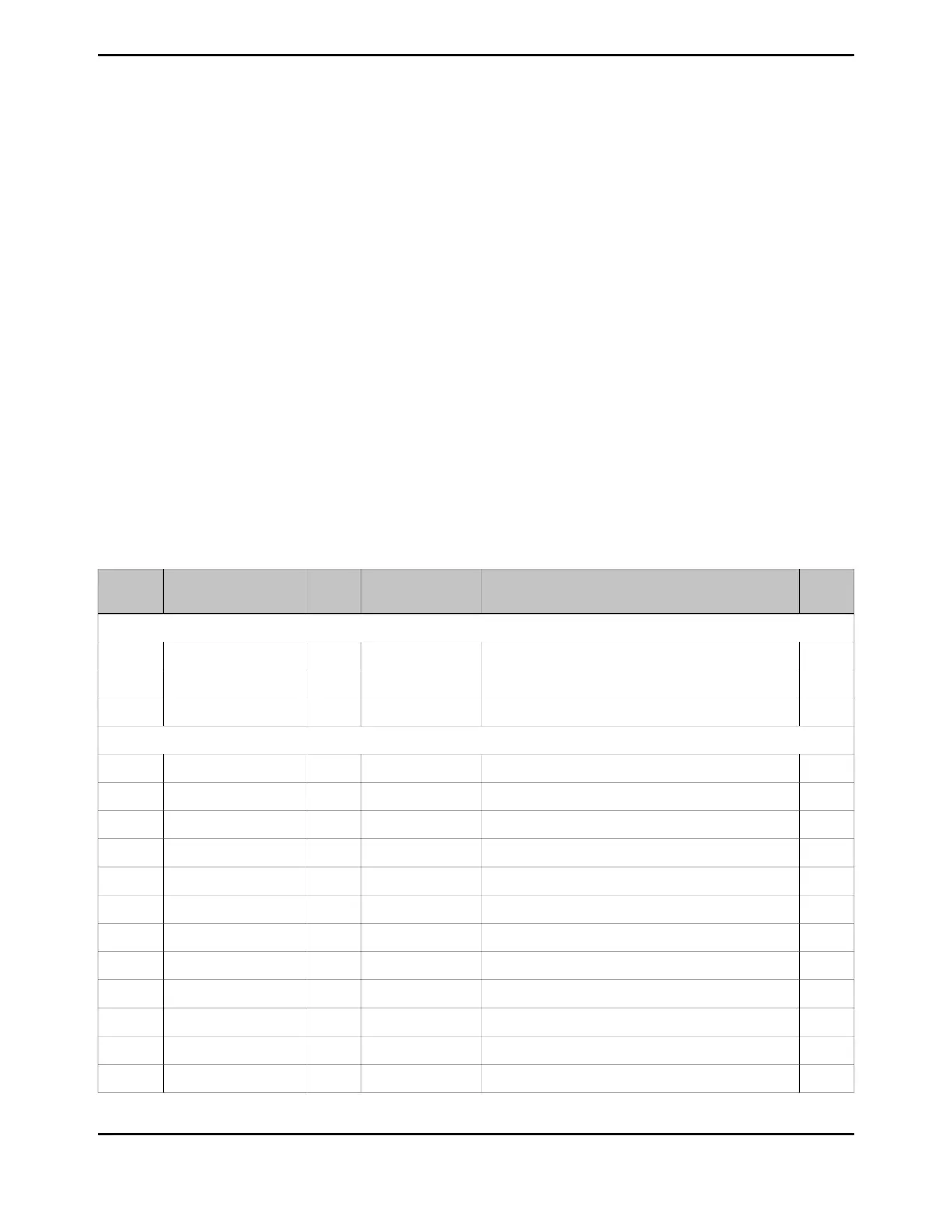

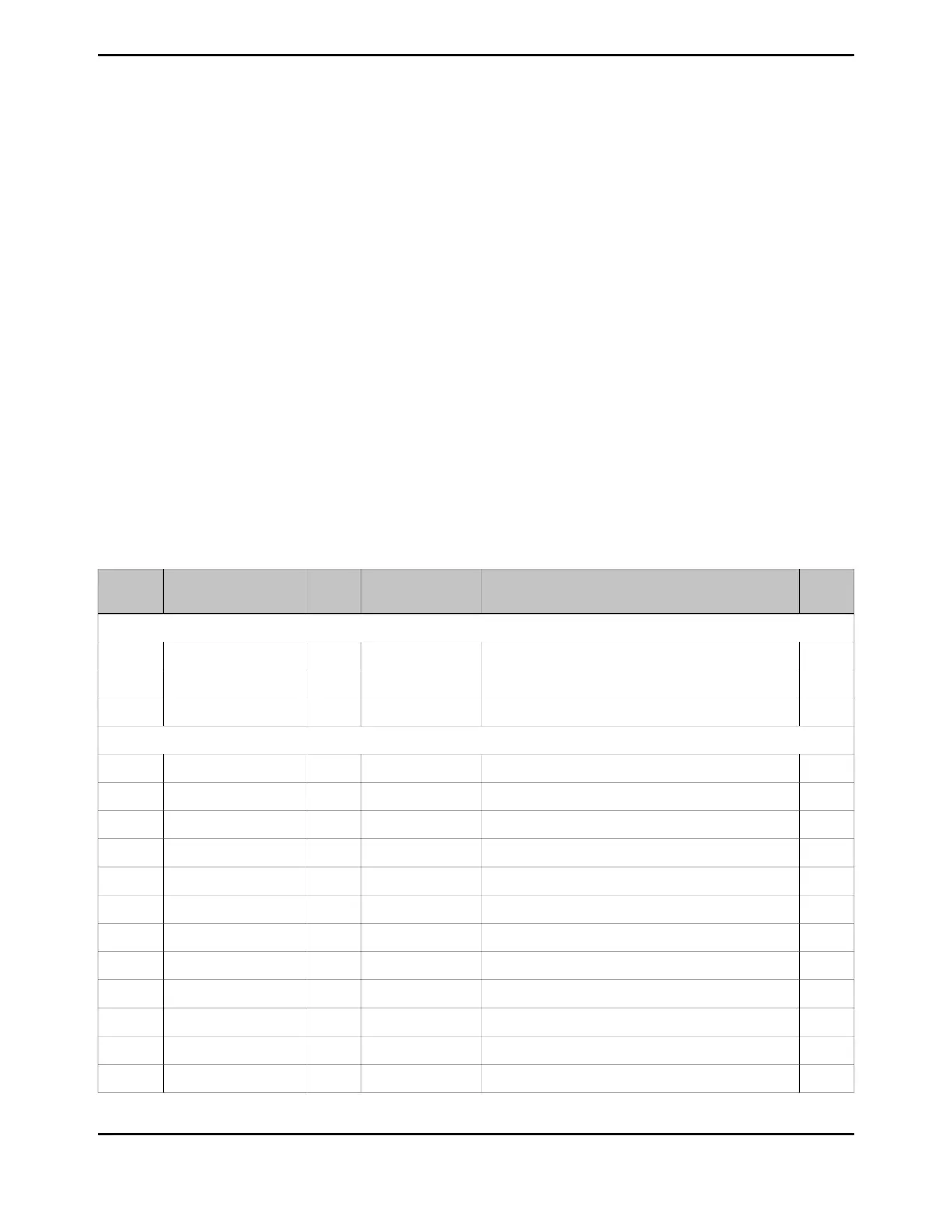

3.2 Register Map

Table 3-8 on page 146 lists the Cortex-M4 Peripheral SysTick, NVIC, MPU, FPU and SCB registers.

The offset listed is a hexadecimal increment to the register's address, relative to the Core Peripherals

base address of 0xE000.E000.

Note: Register spaces that are not used are reserved for future or internal use. Software should

not modify any reserved memory address.

Table 3-8. Peripherals Register Map

See

page

DescriptionResetTypeNameOffset

System Timer (SysTick) Registers

150SysTick Control and Status Register0x0000.0000RWSTCTRL0x010

152SysTick Reload Value Register-RWSTRELOAD0x014

153SysTick Current Value Register-RWCSTCURRENT0x018

Nested Vectored Interrupt Controller (NVIC) Registers

154Interrupt 0-31 Set Enable0x0000.0000RWEN00x100

154Interrupt 32-63 Set Enable0x0000.0000RWEN10x104

154Interrupt 64-95 Set Enable0x0000.0000RWEN20x108

154Interrupt 96-113 Set Enable0x0000.0000RWEN30x10C

155Interrupt 0-31 Clear Enable0x0000.0000RWDIS00x180

155Interrupt 32-63 Clear Enable0x0000.0000RWDIS10x184

155Interrupt 64-95 Clear Enable0x0000.0000RWDIS20x188

155Interrupt 96-113 Clear Enable0x0000.0000RWDIS30x18C

156Interrupt 0-31 Set Pending0x0000.0000RWPEND00x200

156Interrupt 32-63 Set Pending0x0000.0000RWPEND10x204

156Interrupt 64-95 Set Pending0x0000.0000RWPEND20x208

156Interrupt 96-113 Set Pending0x0000.0000RWPEND30x20C

June 18, 2014146

Texas Instruments-Production Data

Cortex-M4 Peripherals

Loading...

Loading...