Register 28: LDO Deep-Sleep Power Calibration (LDODPCAL), offset 0x1C0

This register provides factory determined values that are recommended for the VLDO field in the

LDODPCTL register while in Deep-Sleep mode. The reset value of this register cannot be determined

until the product has been characterized.

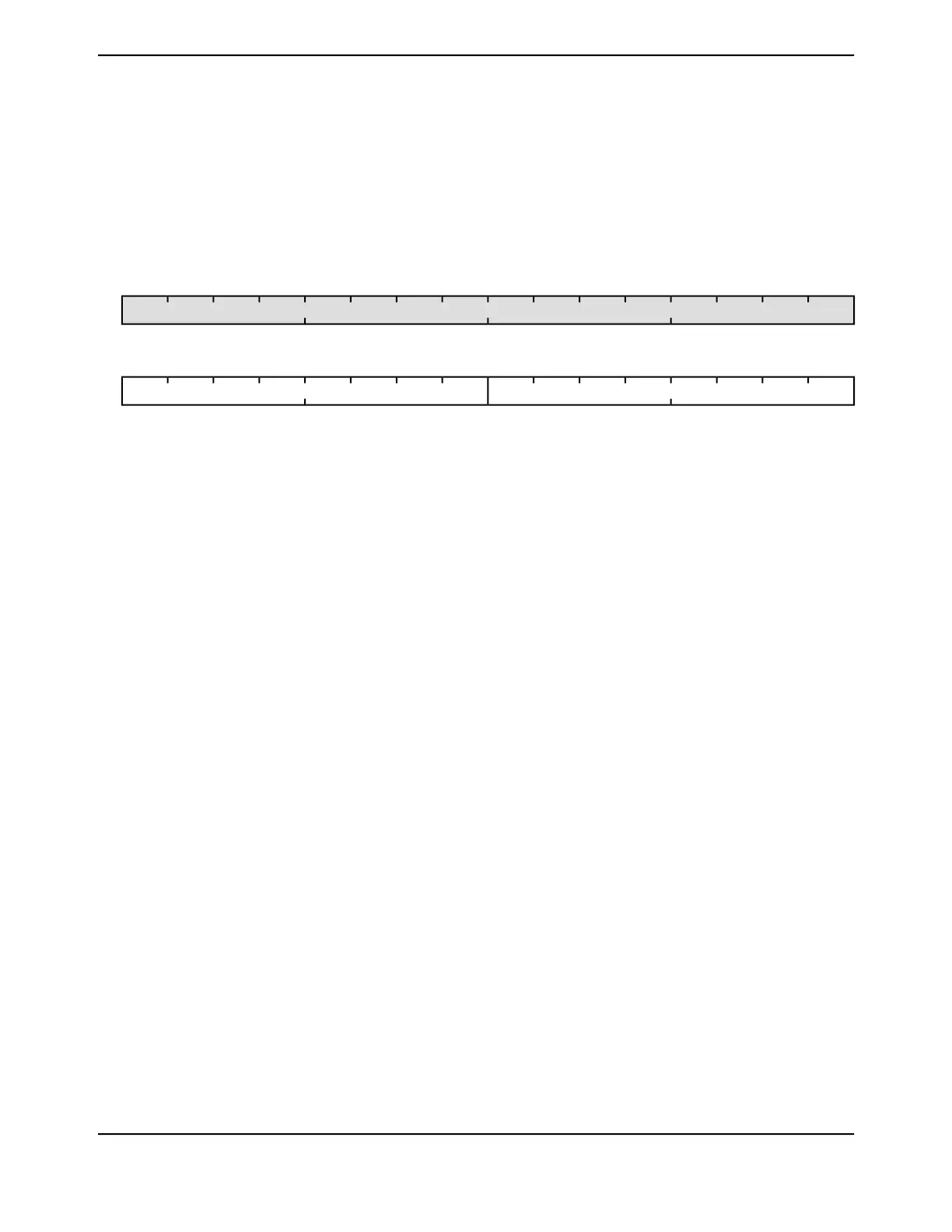

LDO Deep-Sleep Power Calibration (LDODPCAL)

Base 0x400F.E000

Offset 0x1C0

Type RO, reset 0x0000.1212

16171819202122232425262728293031

reserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

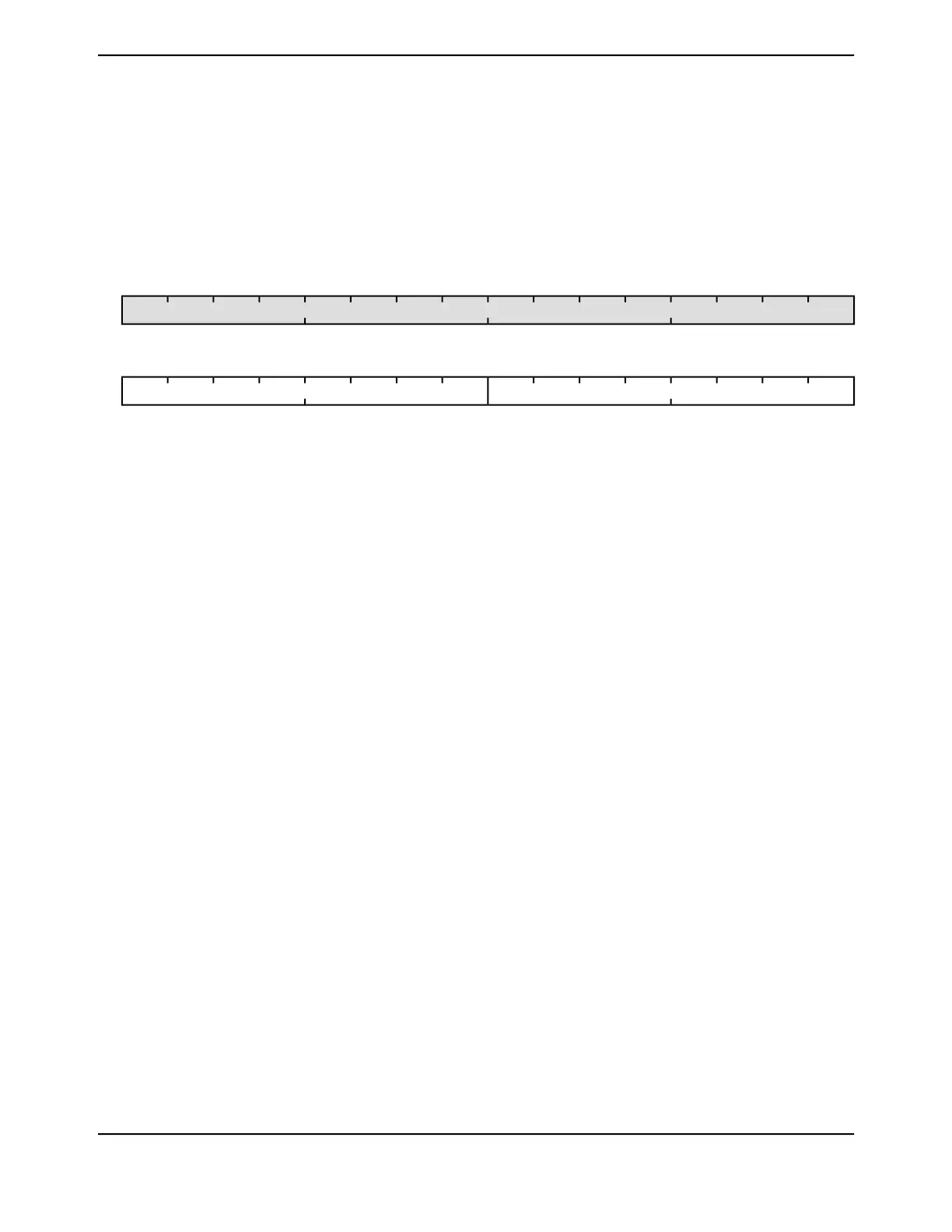

0123456789101112131415

30KHZNOPLL

ROROROROROROROROROROROROROROROROType

0100100001001000Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0ROreserved31:16

Deep-Sleep without PLL

The value in this field is the suggested value for the VLDO field in the

LDODPCTL register when not using the PLL. This value provides the

lowest recommended LDO output voltage for use with the system clock.

0x12RONOPLL15:8

Deep-Sleep with IOSC

The value in this field is the suggested value for the VLDO field in the

LDODPCTL register when not using the PLL. This value provides the

lowest recommended LDO output voltage for use with the low-frequency

internal oscillator.

0x12RO30KHZ7:0

305June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...