field in the EPIHB8CFGn register and on the chip select configuration selected by the CSCFG and

CSCFGEXT field in the EPIHB8CFG2 register.

Although the EPI0S31 signal can be configured for the EPI clock signal in Host-Bus mode, it is not

required and should be configured as a GPIO to reduce EMI in the system. Any unused EPI controller

signals can be used as GPIOs or another alternate function.

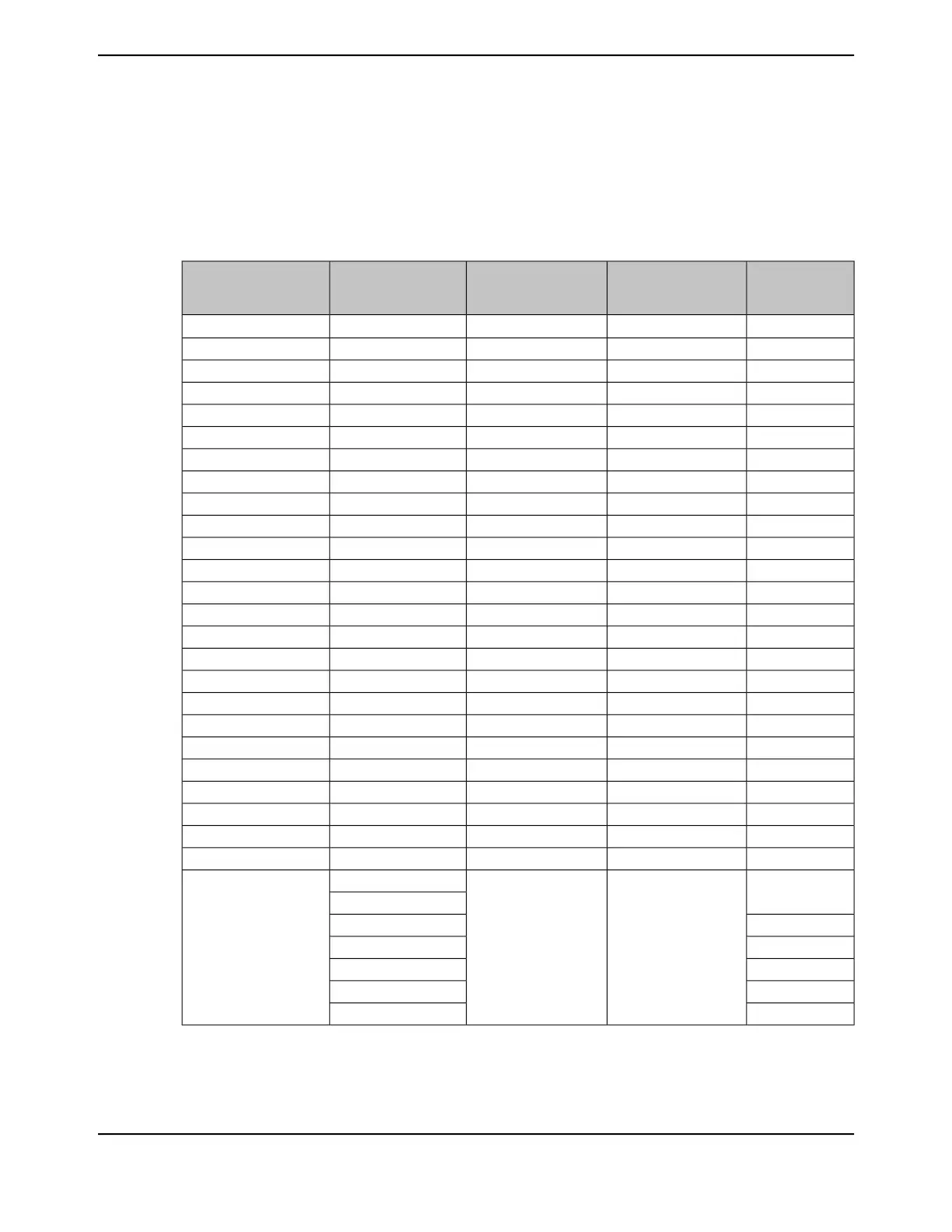

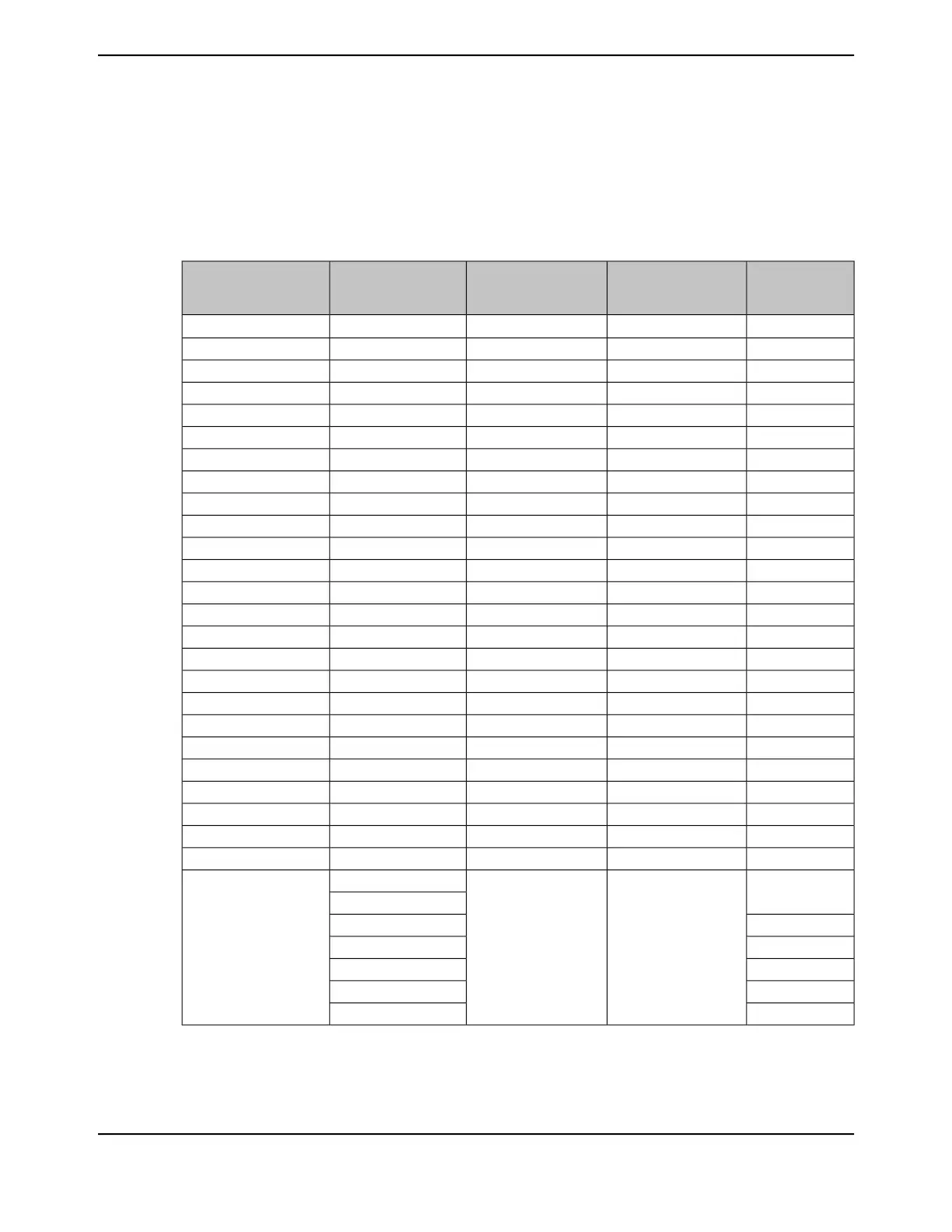

Table 11-8. EPI Host-Bus 8 Signal Connections

HB8 Signal (MODE

=XFIFO)

HB8 Signal (MODE

=ADNOMUX (Cont.

Read))

HB8 Signal (MODE

=ADMUX)

CSCFGEPI Signal

D0D0AD0X

a

EPI0S0

D1D1AD1XEPI0S1

D2D2AD2XEPI0S2

D3D3AD3XEPI0S3

D4D4AD4XEPI0S4

D5D5AD5XEPI0S5

D6D6AD6XEPI0S6

D7D7AD7XEPI0S7

-A0A8XEPI0S8

-A1A9XEPI0S9

-A2A10XEPI0S10

-A3A11XEPI0S11

-A4A12XEPI0S12

-A5A13XEPI0S13

-A6A14XEPI0S14

-A7A15XEPI0S15

-A8A16XEPI0S16

-A9A17XEPI0S17

-A10A18XEPI0S18

-A11A19XEPI0S19

-A12A20XEPI0S20

-A13A21XEPI0S21

-A14A22XEPI0S22

-A15A23XEPI0S23

-A16A24XEPI0S24

-

A17

A25

b

0x0

EPI0S25

0x1

CS1n0x2

-0x3

-0x4

-0x5

-0x6

831June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...