Register 13: Hibernation Calendar Control (HIBCALCTL), offset 0x300

The Hibernate calendar is enabled by setting the CALEN bit in the HIBCALCTL register. If the BCD

bit is set, the fields are reported in BCD format.

Hibernation Calendar Control (HIBCALCTL)

Base 0x400F.C000

Offset 0x300

Type RW, reset 0x0000.0000

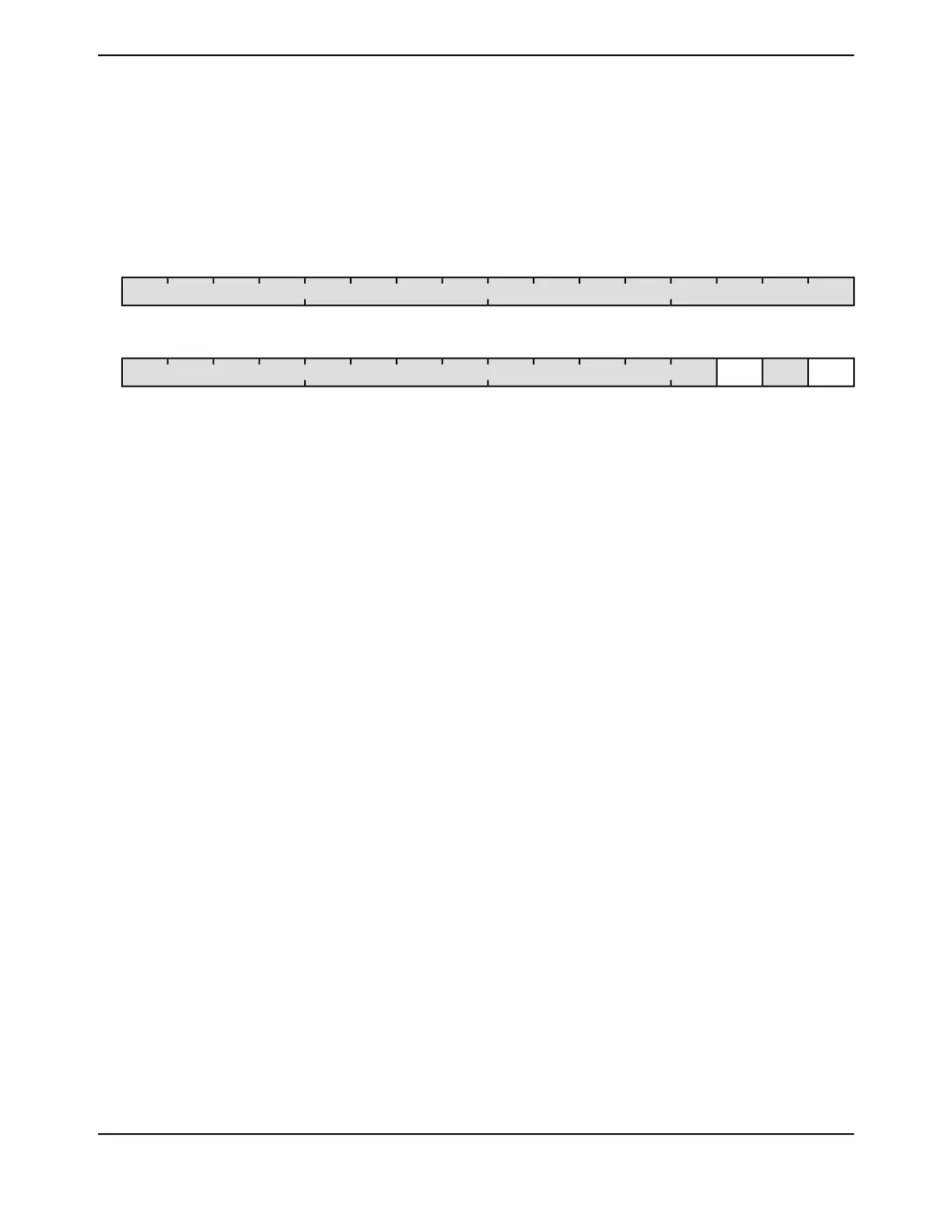

16171819202122232425262728293031

reserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

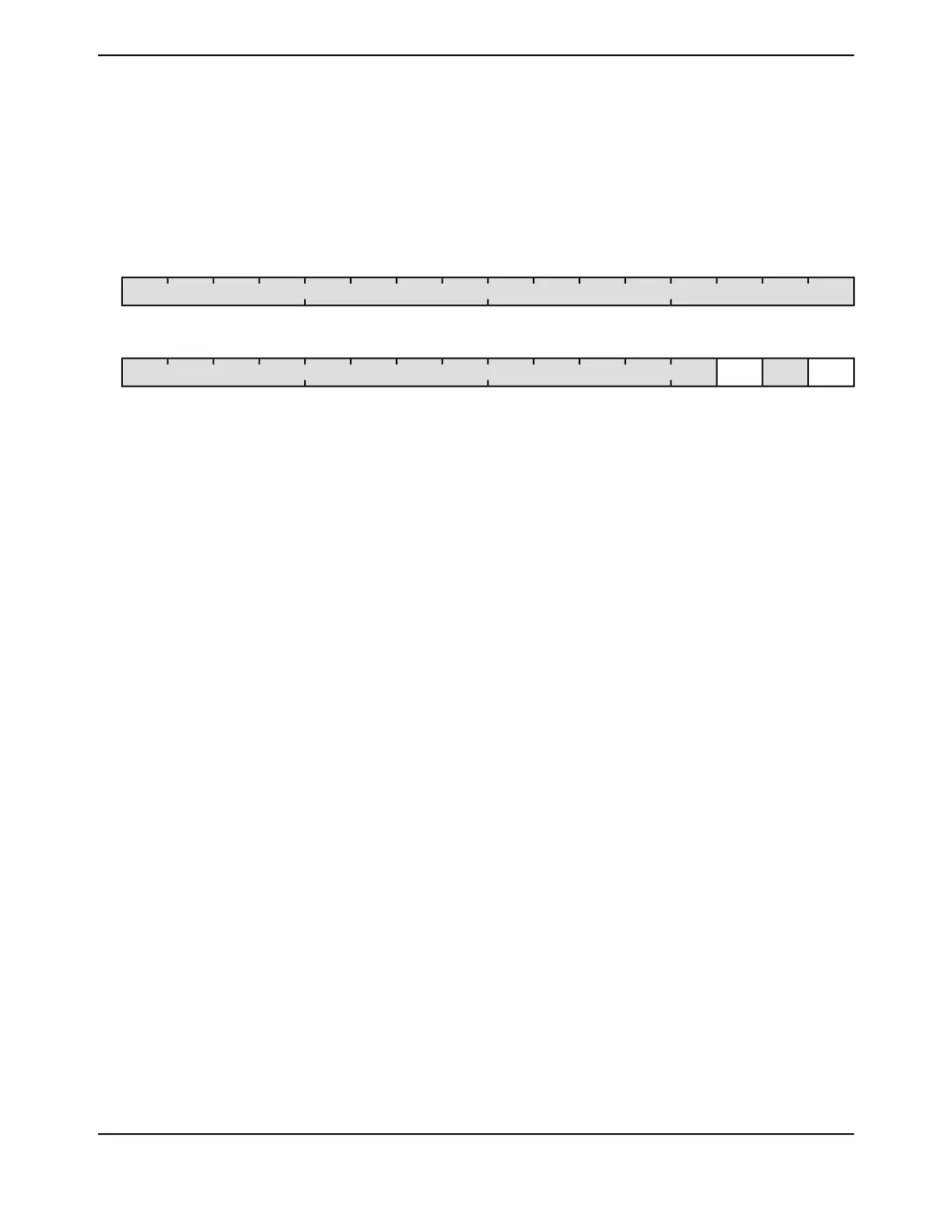

0123456789101112131415

CALENreservedCAL24reserved

RWRORWROROROROROROROROROROROROROType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0ROreserved31:3

Calendar Mode

DescriptionValue

12 hour, AM/PM Mode0

24 hour mode1

0RWCAL242

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0ROreserved1

RTC Calendar/Counter Mode Select

Note that the RTC must be enabled by setting the RTCEN bit in the

HIBCTL register to use this mode select.

DescriptionValue

RTC Counter mode enabled.0

Calendar mode enabled1

0RWCALEN0

575June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...