Register 30: Reset Behavior Control Register (RESBEHAVCTL), offset 0x1D8

The Reset Behavior Control Register contains system management controls.

The RESBEHAVCTL register effect occurs immediately when the register is changed. The next

power-on reset sequence returns the reset value.

If any bit field below is set to 0x3 when a reset occurs, a simulated POR will be generated and the

appropriate reset cause will be set in the Reset Cause (RESC) register. During a simulated POR,

registers are reloaded and the bootloader is executed. If a full POR is initiated the POR bit in the

RESC register will be set and all other bits will be cleared.

Reset Behavior Control Register (RESBEHAVCTL)

Base 0x400F.E000

Offset 0x1D8

Type RW, reset 0xFFFF.FFFF

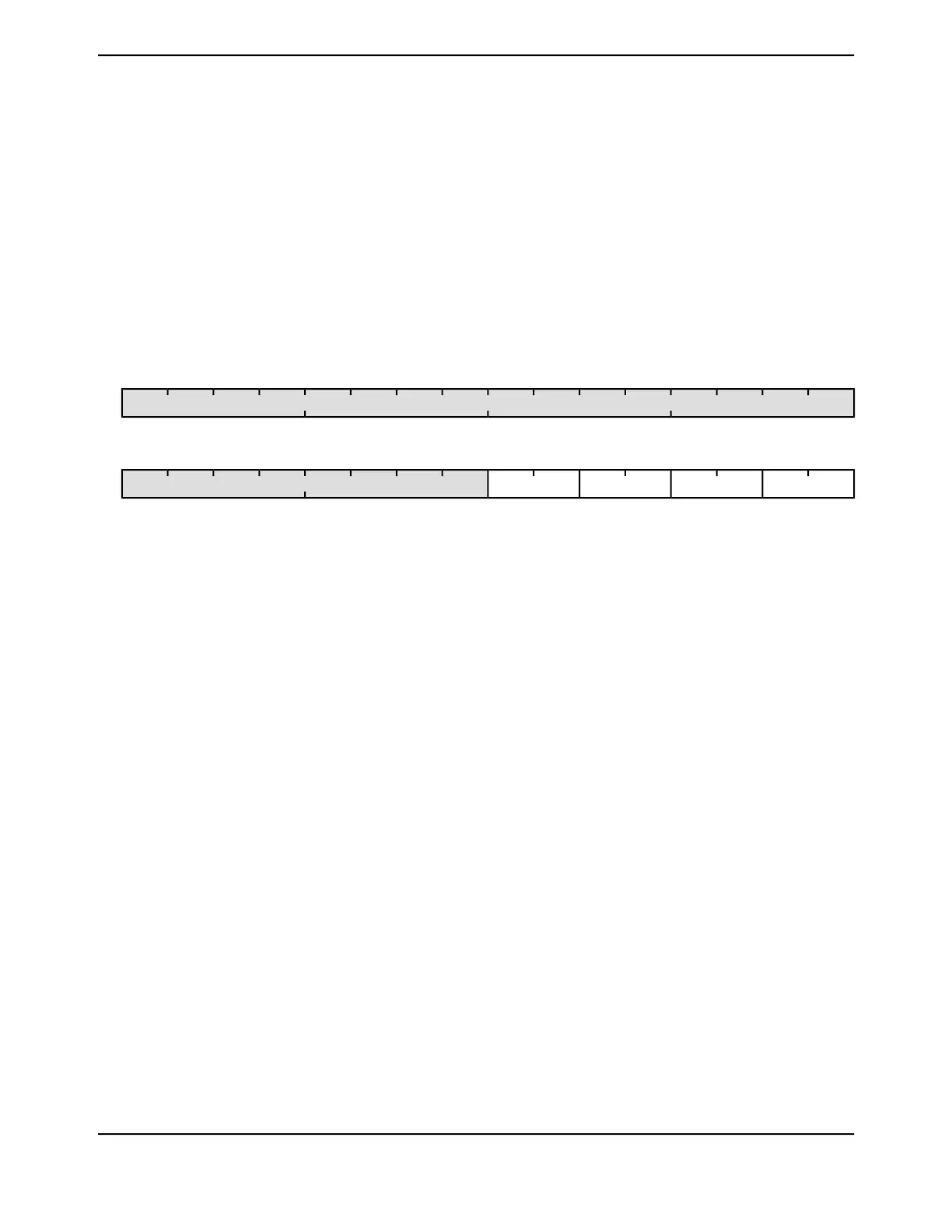

16171819202122232425262728293031

reserved

ROROROROROROROROROROROROROROROROType

1111111111111111Reset

0123456789101112131415

EXTRESBORWDOG0WDOG1reserved

RWRWRWRWRWRWRWRWROROROROROROROROType

1111111111111111Reset

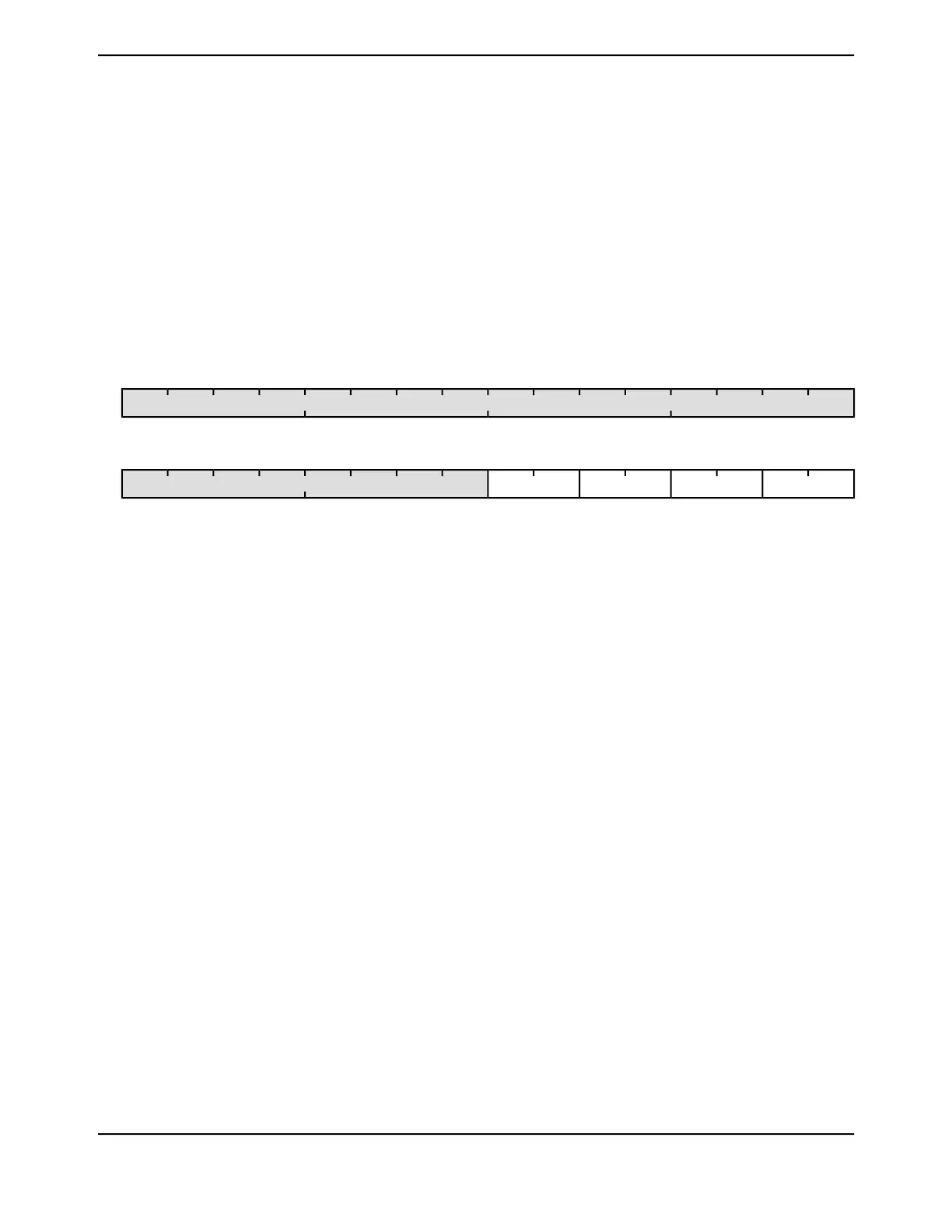

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0xFFFF.FFROreserved31:8

Watchdog 1 Reset Operation

DescriptionValue

Reserved. Default operation is performed.0x0 - 0x1

Watchdog 1 issues a system reset.0x2

Watchdog 1 issues a simulated POR sequence (default).0x3

0x3RWWDOG17:6

Watchdog 0 Reset Operation

DescriptionValue

Reserved. Default operation is performed.0x0 - 0x1

Watchdog 0 issues a system reset.0x2

Watchdog 0 issues a simulated POR sequence (default).0x3

0x3RWWDOG05:4

309June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...