Register 3: GPTM Timer B Mode (GPTMTBMR), offset 0x008

This register configures the GPTM based on the configuration selected in the GPTMCFG register.

When in PWM mode, set the TBAMS bit, clear the TBCMR bit, and configure the TBMR field to 0x1 or

0x2.

This register controls the modes for Timer B when it is used individually. When Timer A and Timer

B are concatenated, this register is ignored and GPTMTAMR controls the modes for both Timer A

and Timer B.

Important: Except for the TCACT bit field, all other bits in this register should only be changed when

the TBEN bit in the GPTMCTL register is cleared.

GPTM Timer B Mode (GPTMTBMR)

16/32-bit Timer 0 base: 0x4003.0000

16/32-bit Timer 1 base: 0x4003.1000

16/32-bit Timer 2 base: 0x4003.2000

16/32-bit Timer 3 base: 0x4003.3000

16/32-bit Timer 4 base: 0x4003.4000

16/32-bit Timer 5 base: 0x4003.5000

16/32-bit Timer 6 base: 0x400E.0000

16/32-bit Timer 7 base: 0x400E.1000

Offset 0x008

Type RW, reset 0x0000.0000

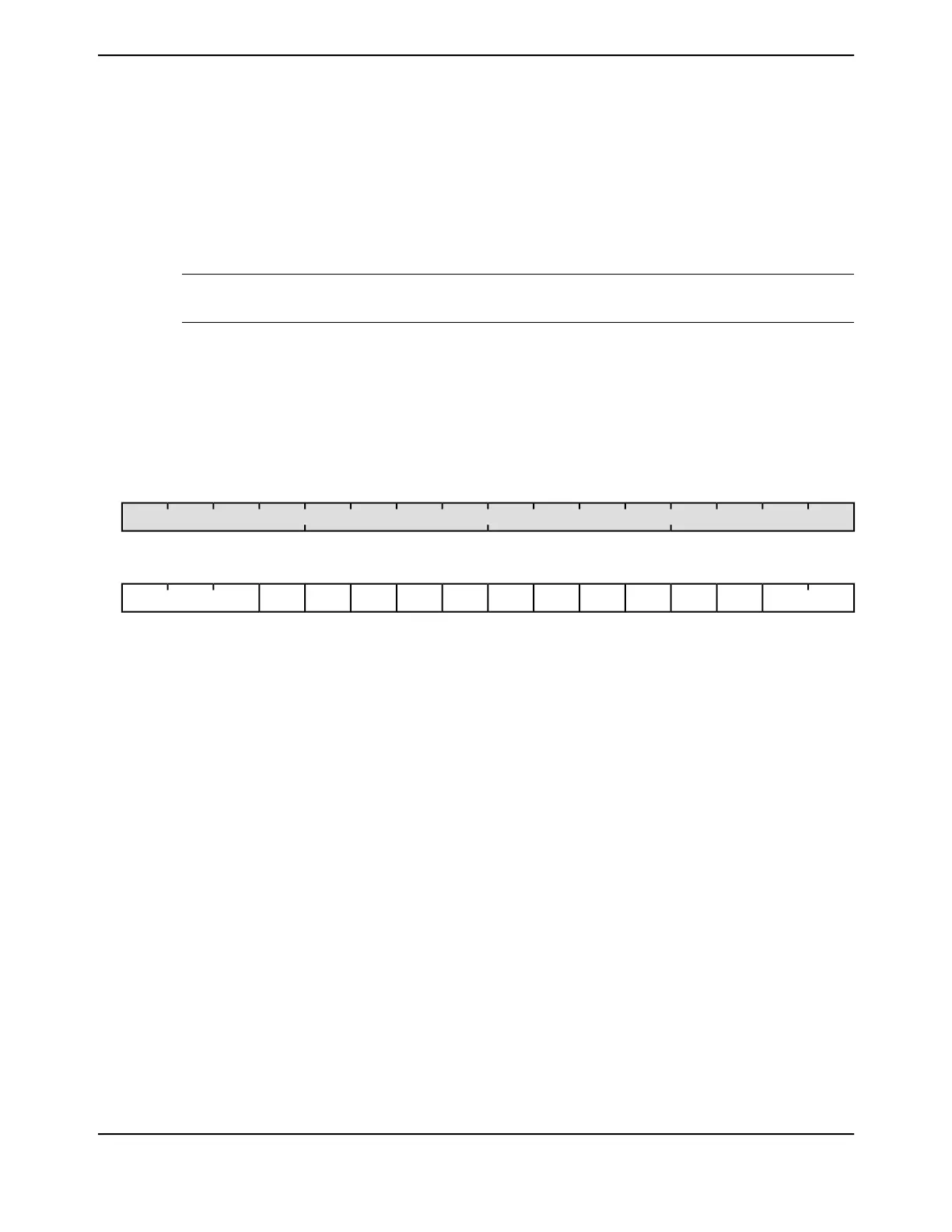

16171819202122232425262728293031

reserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

0123456789101112131415

TBMRTBCMRTBAMSTBCDIRTBMIETBWOTTBSNAPSTBILDTBPWMIETBMRSUTBPLOTBCINTDTCACT

RWRWRWRWRWRWRWRWRWRWRWRWRWRWRWRWType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0000.00ROreserved31:16

Timer Compare Action Select

DescriptionValue

Disable compare operations0x0

Toggle State on Time-Out0x1

Clear CCP on Time-Out0x2

Set CCP on Time-Out0x3

Set CCP immediately and toggle on Time-Out0x4

Clear CCP immediately and toggle on Time-Out0x5

Set CCP immediately and clear on Time-Out0x6

Clear CCP immediately and set on Time-Out0x7

0x0RWTCACT15:13

June 18, 2014982

Texas Instruments-Production Data

General-Purpose Timers

Loading...

Loading...