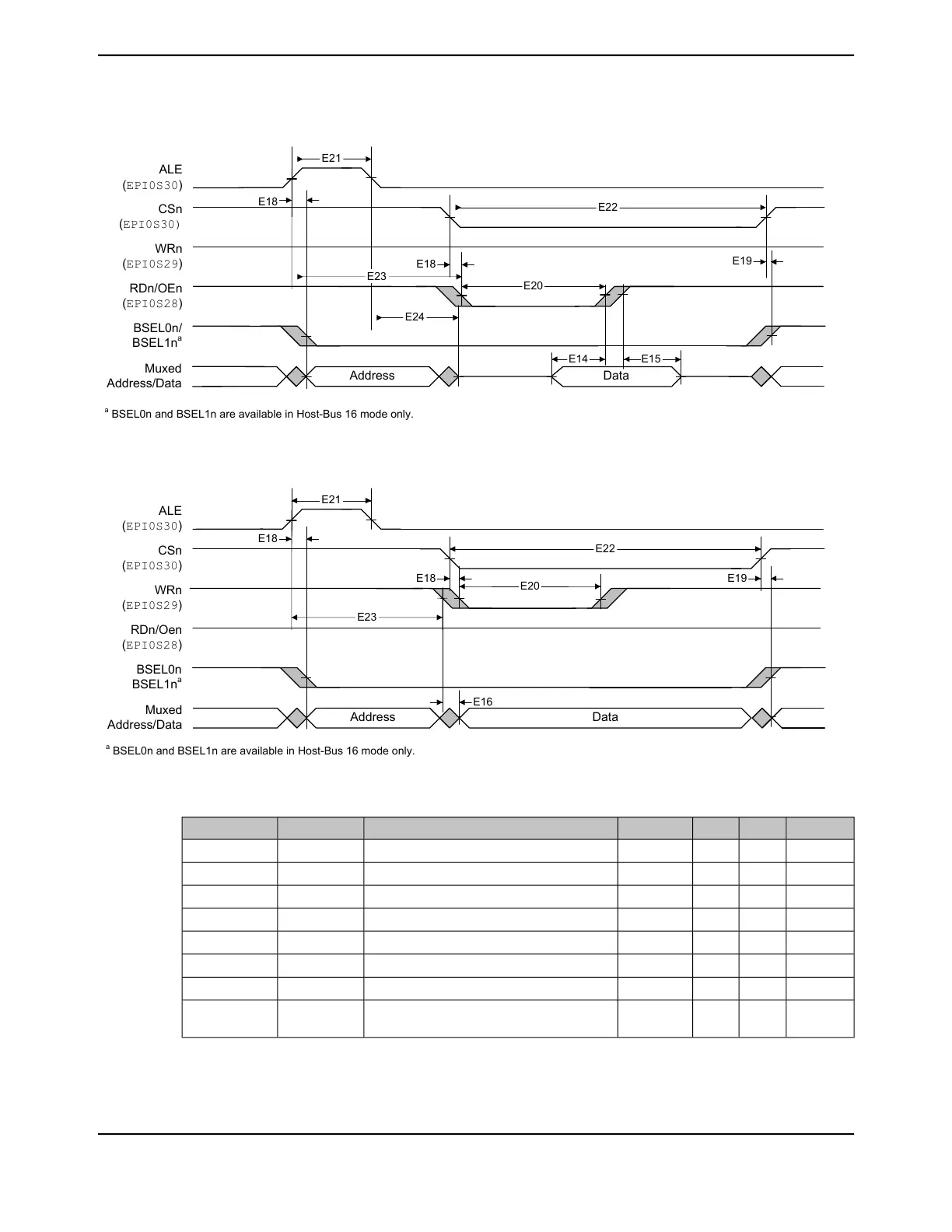

Figure 27-23. Host-Bus 8/16 Mode Asynchronous Muxed Read Timing

Address

Data

ALE

(EPI0S30)

CSn

(EPI0S30)

WRn

(EPI0S29)

RDn/OEn

(EPI0S28)

E15

E18

E18

E14

E19

E20

E21

E22

BSEL0n/

BSEL1n

a

Muxed

Address/Data

E24

E23

a

BSEL0n and BSEL1n are available in Host-Bus 16 mode only.

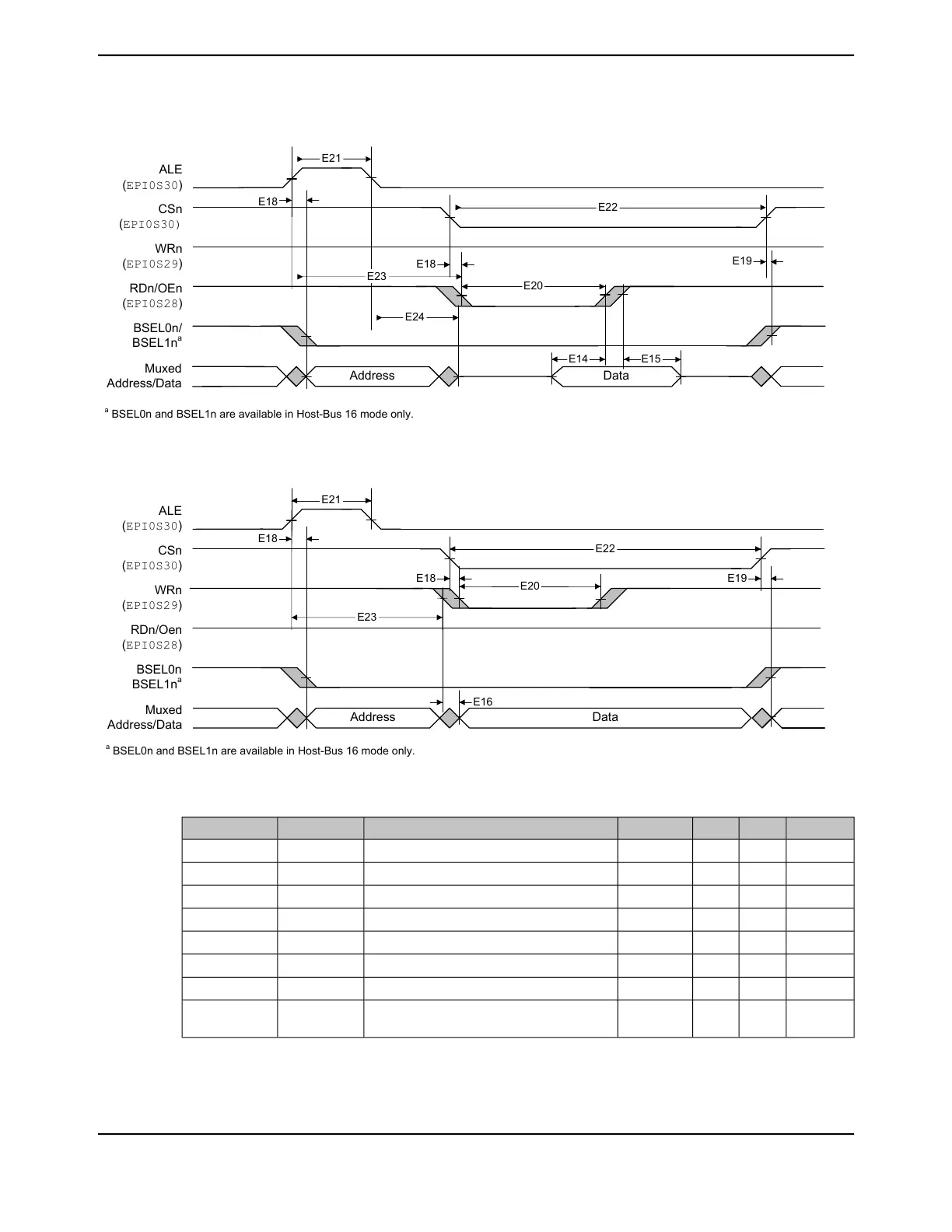

Figure 27-24. Host-Bus 8/16 Mode Asynchronous Muxed Write Timing

ALE

(EPI0S30)

CSn

(EPI0S30)

WRn

(EPI0S29)

RDn/Oen

(EPI0S28)

E18

E18

E16

E20

E19

E21

E22

E23

BSEL0n

BSEL1n

a

Data

Muxed

Address/Data

Address

a

BSEL0n and BSEL1n are available in Host-Bus 16 mode only.

Table 27-42. EPI General-Purpose Interface Characteristics

UnitMaxNomMinParameter NameParameterParameter No

ns--16.67General-Purpose Clock periodT

CK

E25

ns--8.33General-Purpose Clock high timeT

CH

E26

ns--8.33General-Purpose Clock low timeT

CL

E27

ns--8.50Input signal set up time to rising clock edgeT

ISU

E28

ns--0Input signal hold time from rising clock edgeT

IH

E29

ns4--Falling clock edge to output validT

DV

E30

ns4--Falling clock edge to output invalidT

DI

E31

ns--8.5iRDY assertion or deassertion set up time to

falling clock edge

T

RDYSU

E32

1857June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...