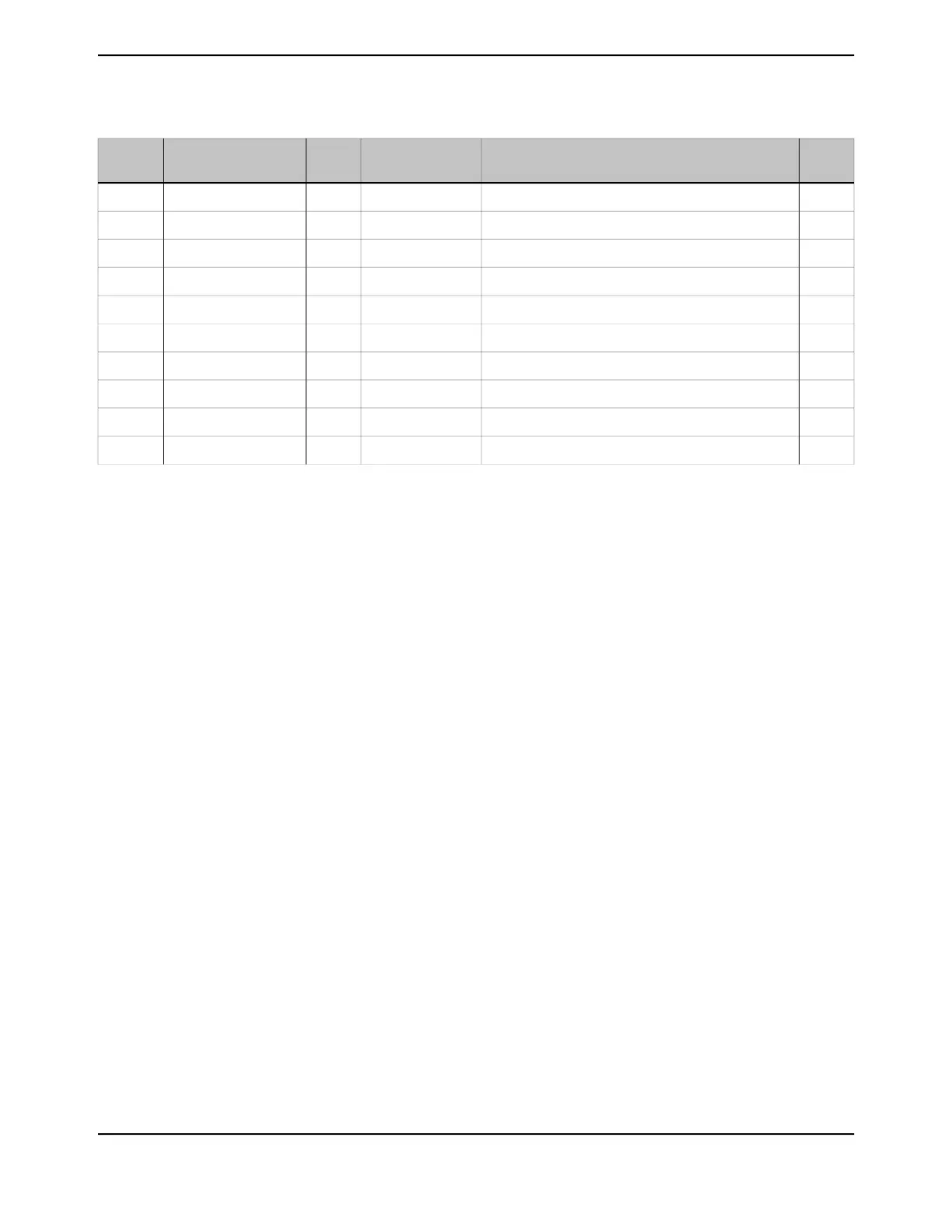

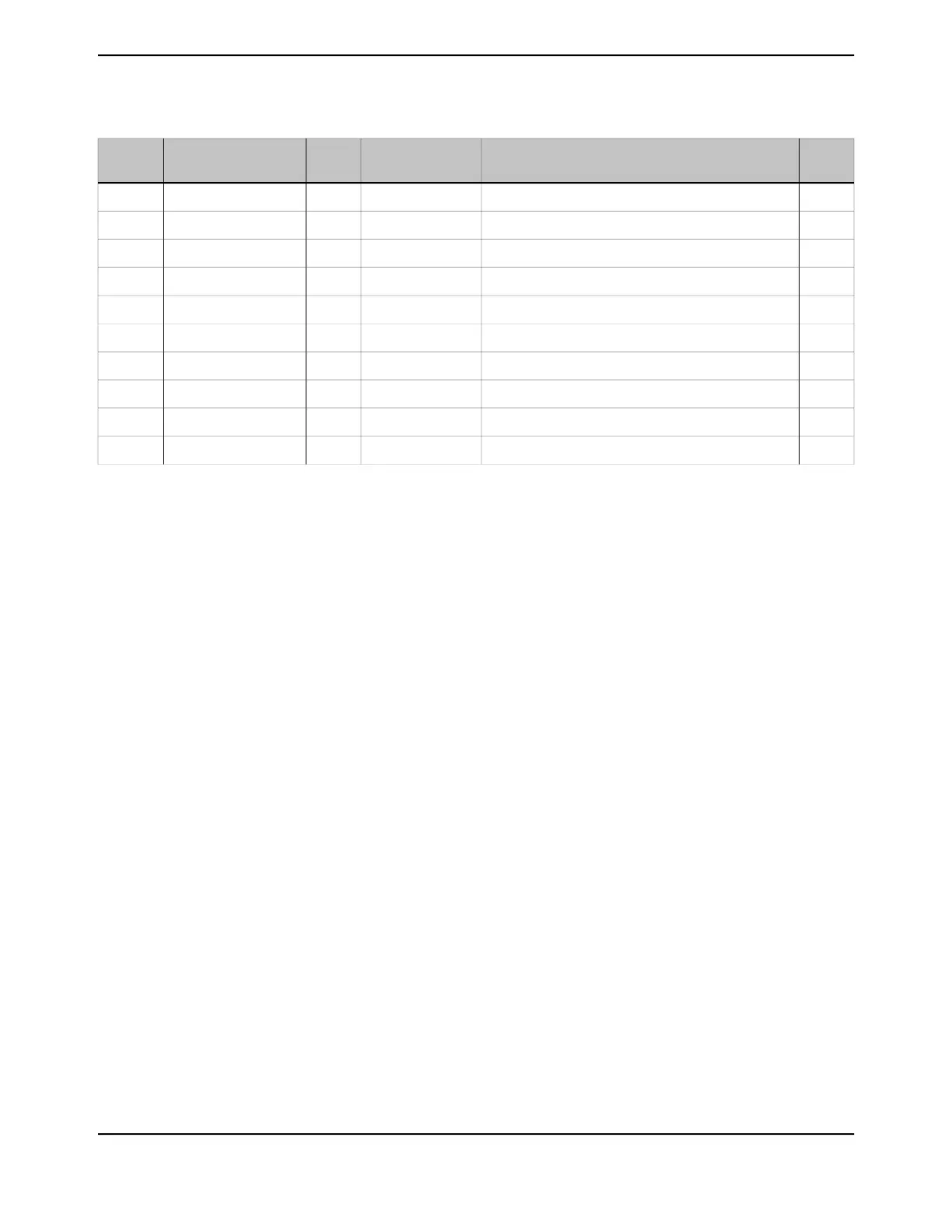

Table 2-2. Processor Register Map (continued)

See

page

DescriptionResetTypeNameOffset

88Cortex General-Purpose Register 12-RWR12-

89Stack Pointer-RWSP-

90Link Register0xFFFF.FFFFRWLR-

91Program Counter-RWPC-

92Program Status Register0x0100.0000RWPSR-

96Priority Mask Register0x0000.0000RWPRIMASK-

97Fault Mask Register0x0000.0000RWFAULTMASK-

98Base Priority Mask Register0x0000.0000RWBASEPRI-

99Control Register0x0000.0000RWCONTROL-

101Floating-Point Status Control-RWFPSC-

2.3.4 Register Descriptions

This section lists and describes the Cortex-M4F registers, in the order shown in Figure

2-3 on page 86. The core registers are not memory mapped and are accessed by register name

rather than offset.

Note: The register type shown in the register descriptions refers to type during program execution

in Thread mode and Handler mode. Debug access can differ.

87June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...