register, the CSCFG field and the CSCFGEXT bit in the EPIHBnCFGn register, and the BSEL bit in

the EPIHB16CFG register. The CSCFGEXT bit extends the chip select configuration possibilities by

providing the most significant bit of the CSCFG field. Refer to Table 11-4 on page 827 for the possible

ALE and chip select options that can be programmed by the combination of the CSCFGEXT and

CSCFG bits. Note that CSCFGEXT is the most significant bit.

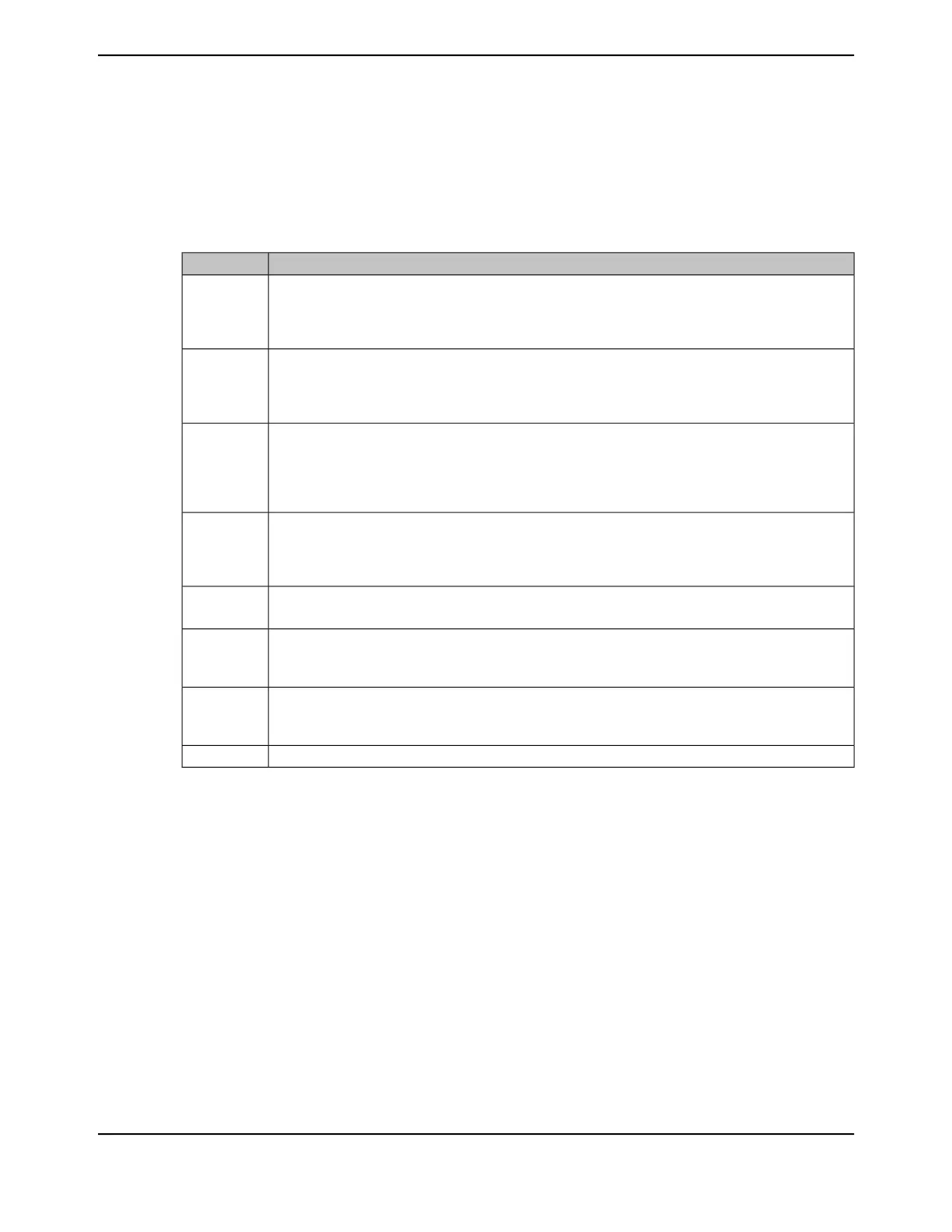

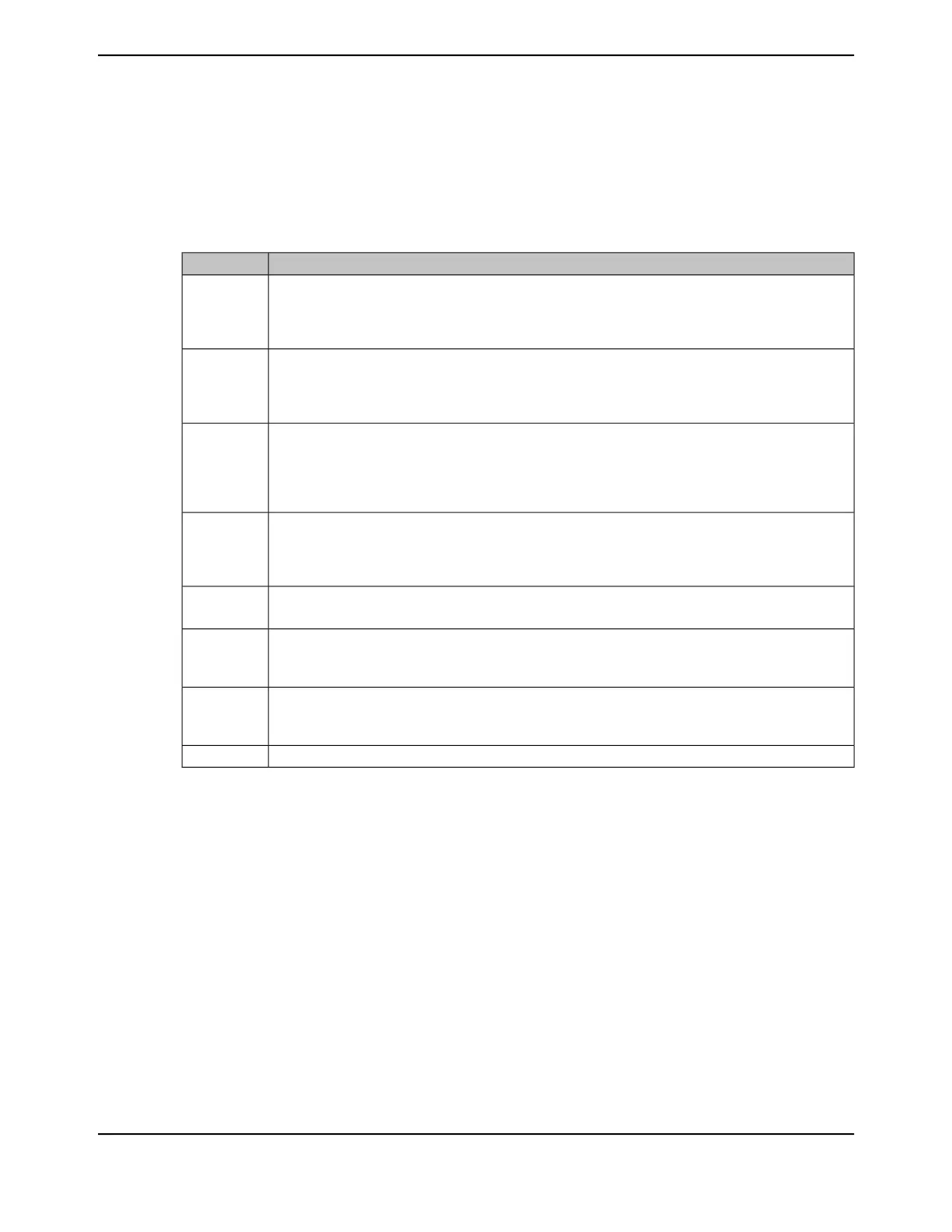

Table 11-4. CSCFGEXT + CSCFG Encodings

DescriptionValue

ALE Configuration

EPI0S30 is used as an address latch (ALE). The ALE signal is generally used when the address and data

are muxed (MODE field in the EPIHB8CFG register is 0x0). The ALE signal is used by an external latch to

hold the address through the bus cycle.

0x0

CSn Configuration

EPI0S30 is used as a Chip Select (CSn). When using this mode, the address and data are generally not

muxed (MODE field in the EPIHB8CFG register is 0x1). However, if address and data muxing is needed,

the WR signal (EPI0S29) and the RD signal (EPI0S28) can be used to latch the address when CSn is low.

0x1

Dual CSn Configuration

EPI0S30 is used as CS0n and EPI0S27 is used as CS1n. Whether CS0n or CS1n is asserted is determined

by the most significant address bit for a respective external address map. This configuration can be used

for a RAM bank split between 2 devices as well as when using both an external RAM and an external

peripheral.

0x2

ALE with Dual CSn Configuration

EPI0S30 is used as address latch (ALE), EPI0S27 is used as CS1n, and EPI0S26 is used as CS0n.

Whether CS0n or CS1n is asserted is determined by the most significant address bit for a respective external

address map.

0x3

ALE with Single CSn Configuration

EPI0S30 is used as address latch (ALE) and EPI0S27 is used as CSn.

0x4

Quad CSn Configuration

EPI0S30 is used as CS0n and EPI0S27 is used as CS1n. EPI0S34 is used as CS2n and EPI0S33 is used

as CS3n.

0x5

ALE with Quad CSn Configuration

EPI0S30 is ALE, EPI0S26 is CS0n and EPI0S27 is used as CS1n. EPI0S34 is used as CS2n and EPI0S33

is used as CS3n.

0x6

Reserved0x7

If one of the Dual-Chip-Select modes is selected (CSCFGEXT is 0x0 and CSCFG is 0x2 or 0x3 in the

EPIHBnCFGn register), both chip selects can share the peripheral, code, or the memory space, or

one chip select can use the peripheral space and the other can use the memory or code space. In

the EPIADDRMAP register, if the EPADR field is not 0x0, the ECADR field is 0x0, and the ERADR

field is 0x0, then the address specified by EPADR is used for both chip selects, with CS0n being

asserted when the MSB of the address range is 0 and CS1n being asserted when the MSB of the

address range is 1. If the ERADR field is not 0x0, the ECADR field is 0x0, and the EPADR field is 0x0,

then the address specified by ERADR is used for both chip selects, with the MSB performing the

same delineation. If both the EPADR and the ERADR are not 0x0, and the ECADR field is 0x0 and the

EPI is configured for dual-chip selects, then CS0n is asserted for either address range defined by

EPADR and CS1n is asserted for either address range defined by ERADR. The two chip selects can

also be shared between the code space and memory or peripheral space. If the ECADR field is 0x1,

ERADR field is 0x0, and the EPADR field is not 0x0, then CS0n is asserted for the address range

defined by ECADR and CS1n is asserted for either address range defined by EPADR. If the ECADR

field is 0x1, EPADR field is 0x0, and the ERADR field is not 0x0, then CS0n is asserted for the address

range defined by ECADR and CS1n is asserted for either address range defined by ERADR.

827June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...