Register 13: I

2

C Master Burst Count (I2CMBCNT), offset 0x034

When BURST is active, the value in the I2CMBLEN register is copied into this register and

decremented during the BURST transaction. This register can be used to determine the number of

transfers that occurred when a BURST terminates early (as a result of a data NACK). When a

BURST completes successfully, this register will contain 0.

I2C Master Burst Count (I2CMBCNT)

I2C 0 base: 0x4002.0000

I2C 1 base: 0x4002.1000

I2C 2 base: 0x4002.2000

I2C 3 base: 0x4002.3000

I2C 4 base: 0x400C.0000

I2C 5 base: 0x400C.1000

I2C 6 base: 0x400C.2000

I2C 7 base: 0x400C.3000

I2C 8 base: 0x400B.8000

I2C 9 base: 0x400B.9000

Offset 0x034

Type RO, reset 0x0000.0000

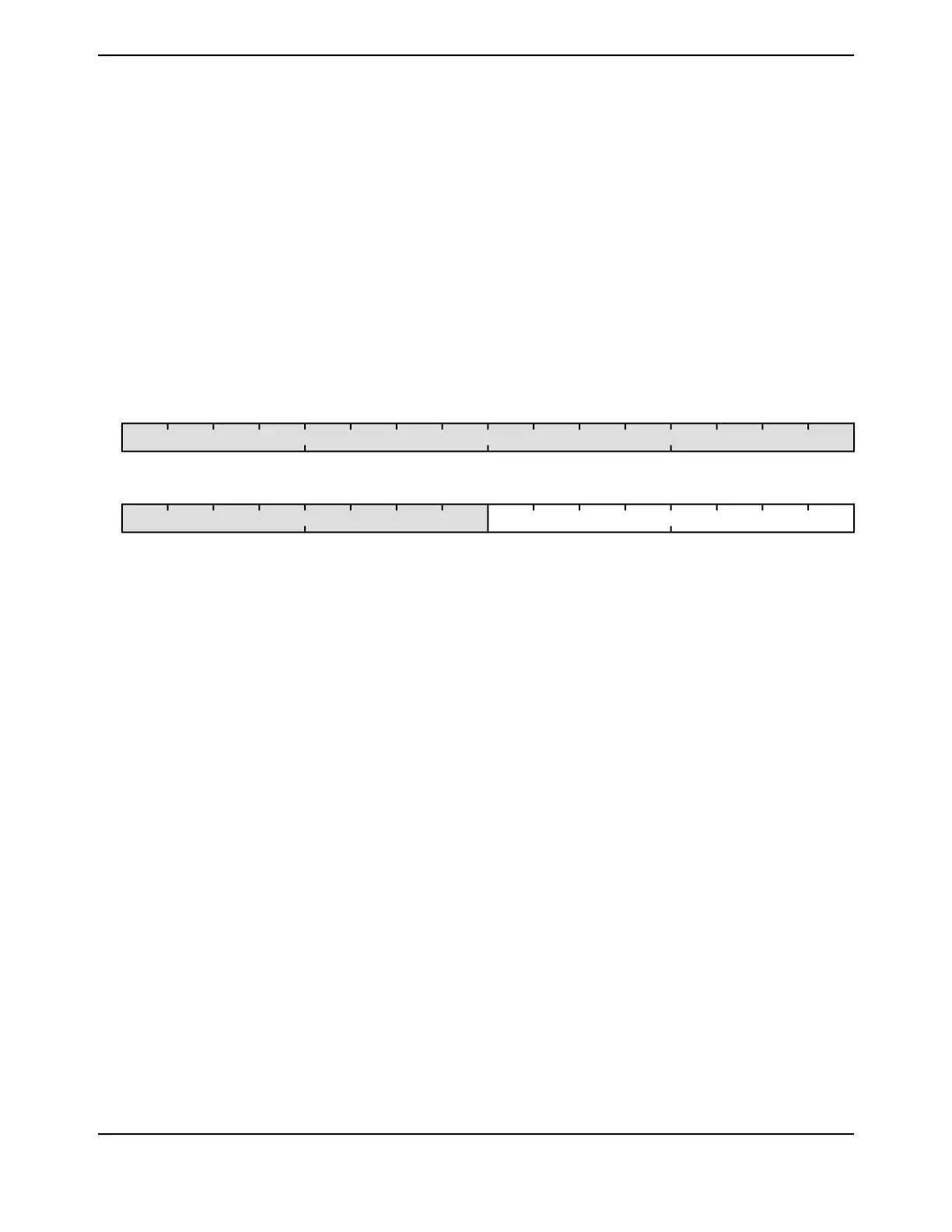

16171819202122232425262728293031

reserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

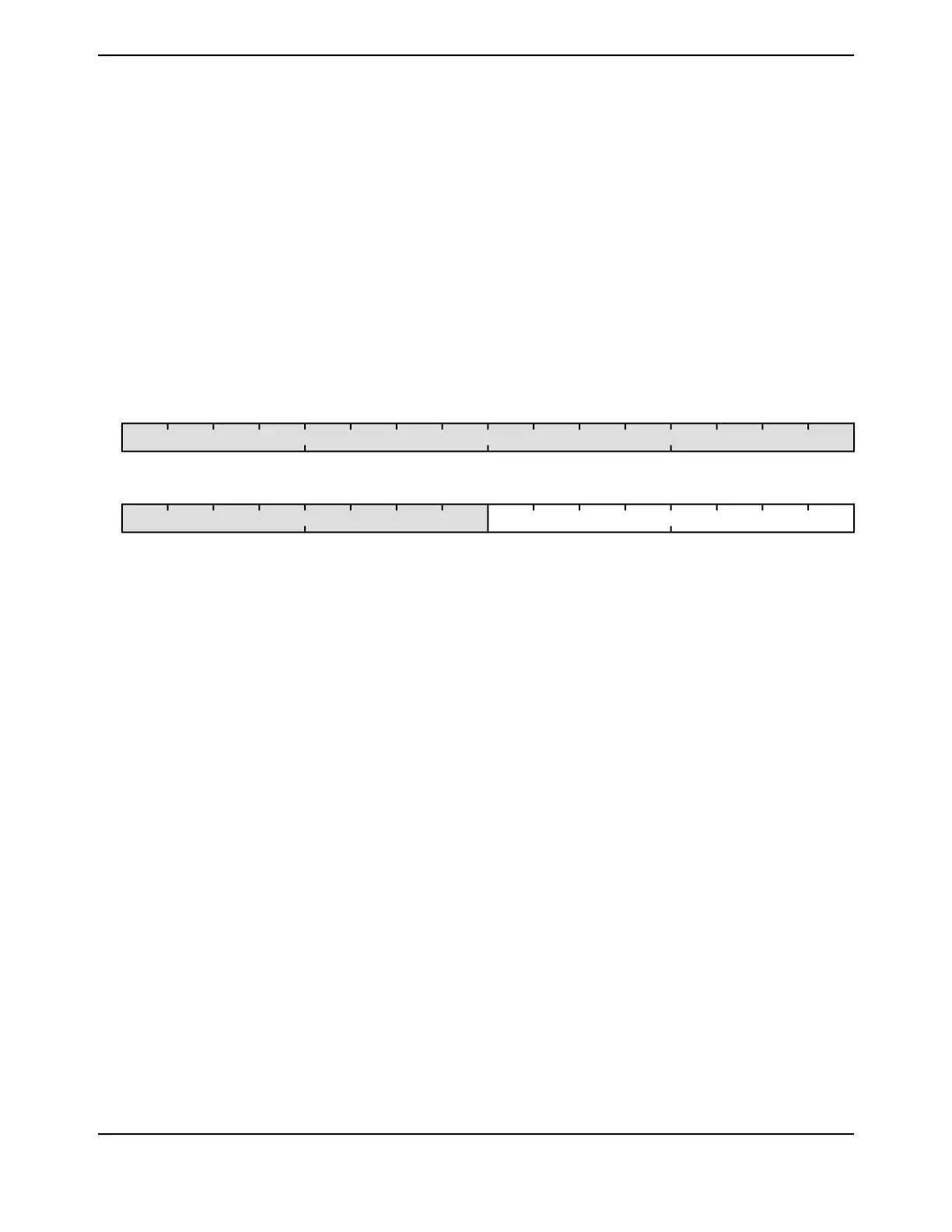

0123456789101112131415

CNTLreserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0000.00ROreserved31:8

I

2

C Master Burst Count

This field contains the current count-down value of the BURST

transaction.

0ROCNTL7:0

18.7 Register Descriptions (I

2

C Slave)

The remainder of this section lists and describes the I

2

C slave registers, in numerical order by

address offset.

June 18, 20141330

Texas Instruments-Production Data

Inter-Integrated Circuit (I

2

C) Interface

Loading...

Loading...