– Slave generates interrupts when data has been transferred or requested by a master or when

a START or STOP condition is detected

■ Master with arbitration and clock synchronization, multimaster support, and 7-bit addressing

mode

■ Efficient transfers using Micro Direct Memory Access Controller (µDMA)

– Separate channels for transmit and receive

– Ability to execute single data transfers or burst data transfers using the RX and TX FIFOs in

the I

2

C

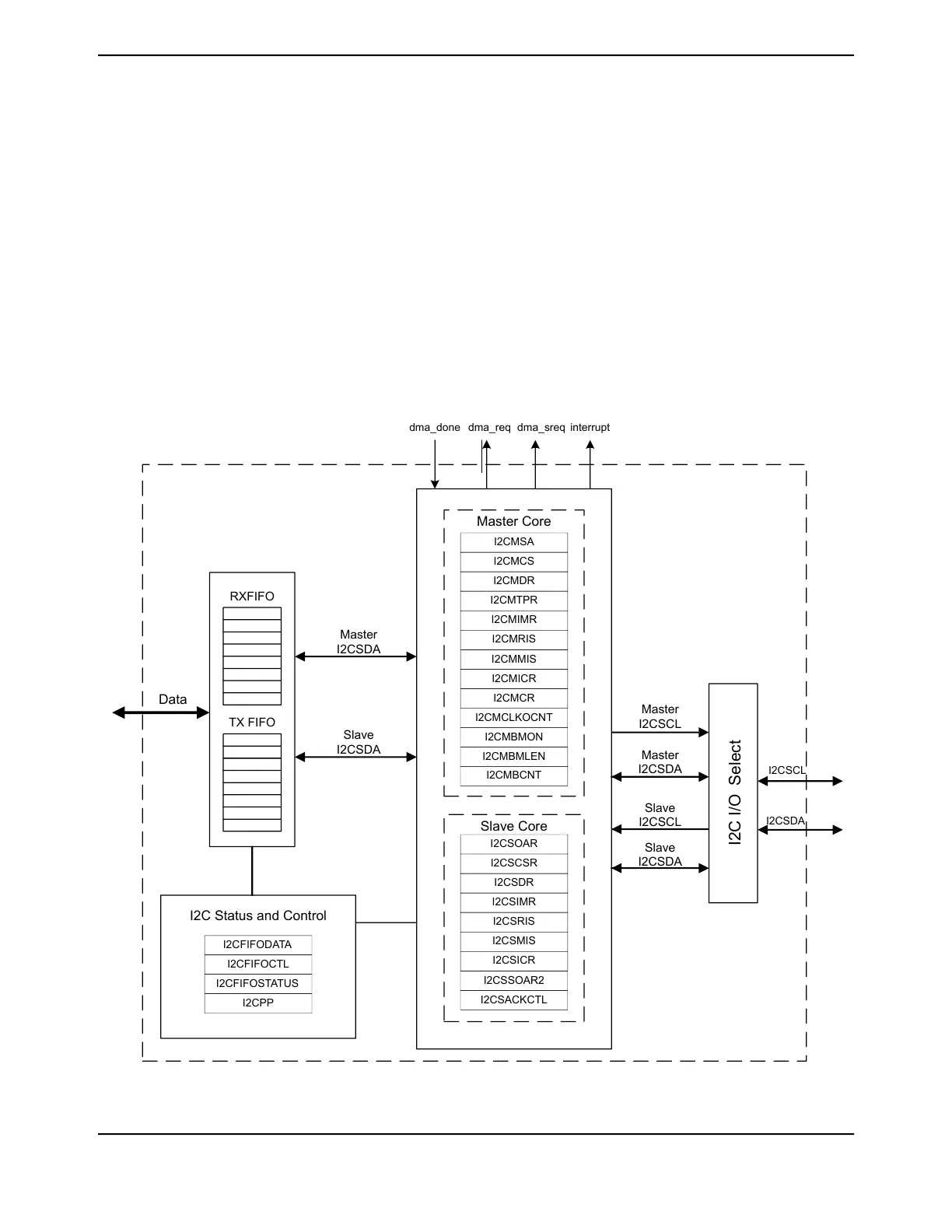

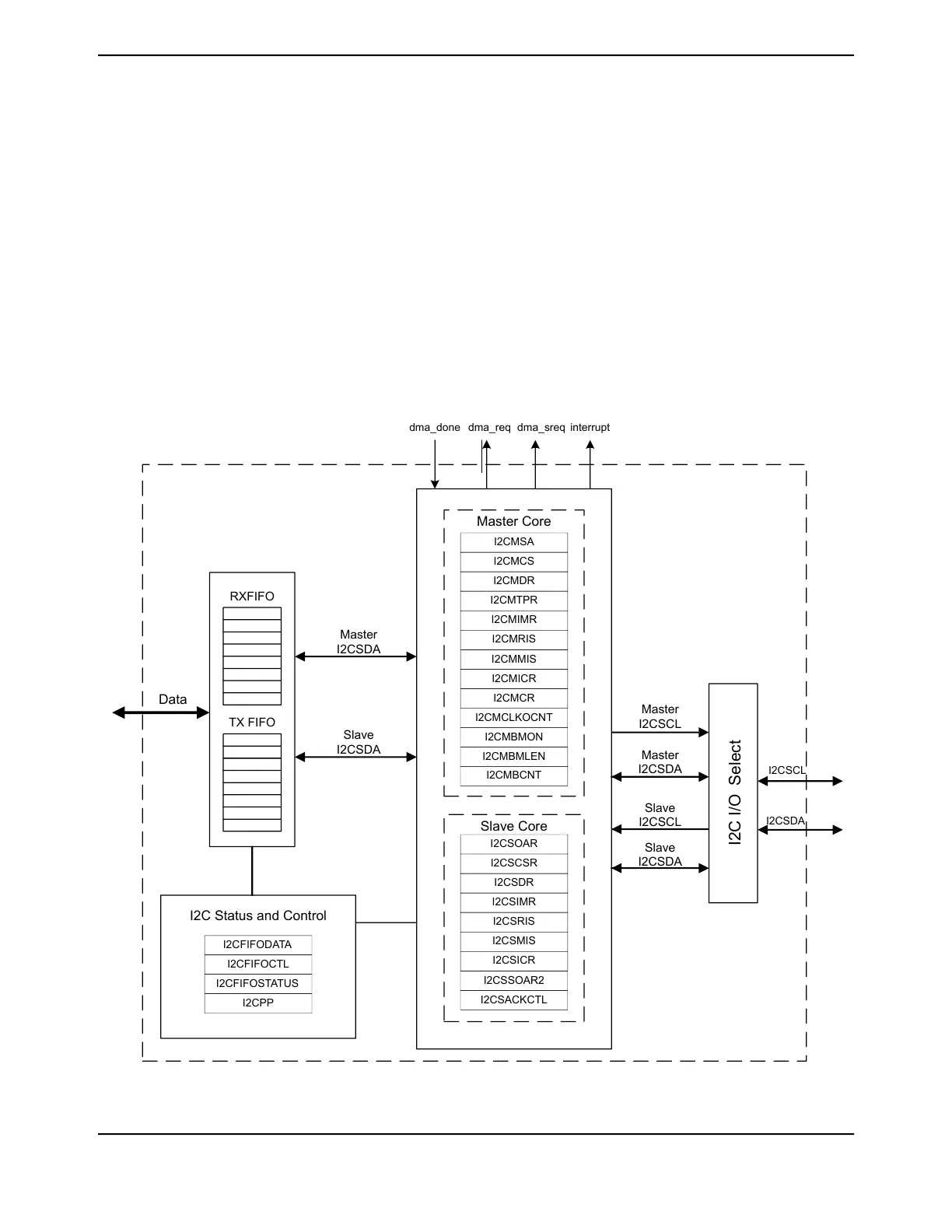

18.1 Block Diagram

Figure 18-1. I

2

C Block Diagram

I2CSDA

I2CSCL

I2CPP

I2CFIFOSTATUS

I2CFIFOCTL

I2CFIFODATA

I2CMSA

I2CMCS

I2CMDR

I2CMTPR

I2CMIMR

I2CMRIS

I2CMICR

I2CMCR

I2CMMIS

I2CMCLKOCNT

I2CMBMON

I2CMBMLEN

I2CMBCNT

Master Core

I2C Status and Control

TX FIFO

RXFIFO

I2C I/O Select

Master

I2CSCL

Master

I2CSDA

Slave

I2CSCL

Slave

I2CSDA

Master

I2CSDA

Slave

I2CSDA

Data

interruptdma_sreqdma_reqdma_done

I2CSOAR

I2CSCSR

I2CSDR

I2CSIMR

I2CSRIS

I2CSMIS

I2CSICR

I2CSSOAR2

I2CSACKCTL

Slave Core

June 18, 20141276

Texas Instruments-Production Data

Inter-Integrated Circuit (I

2

C) Interface

Loading...

Loading...