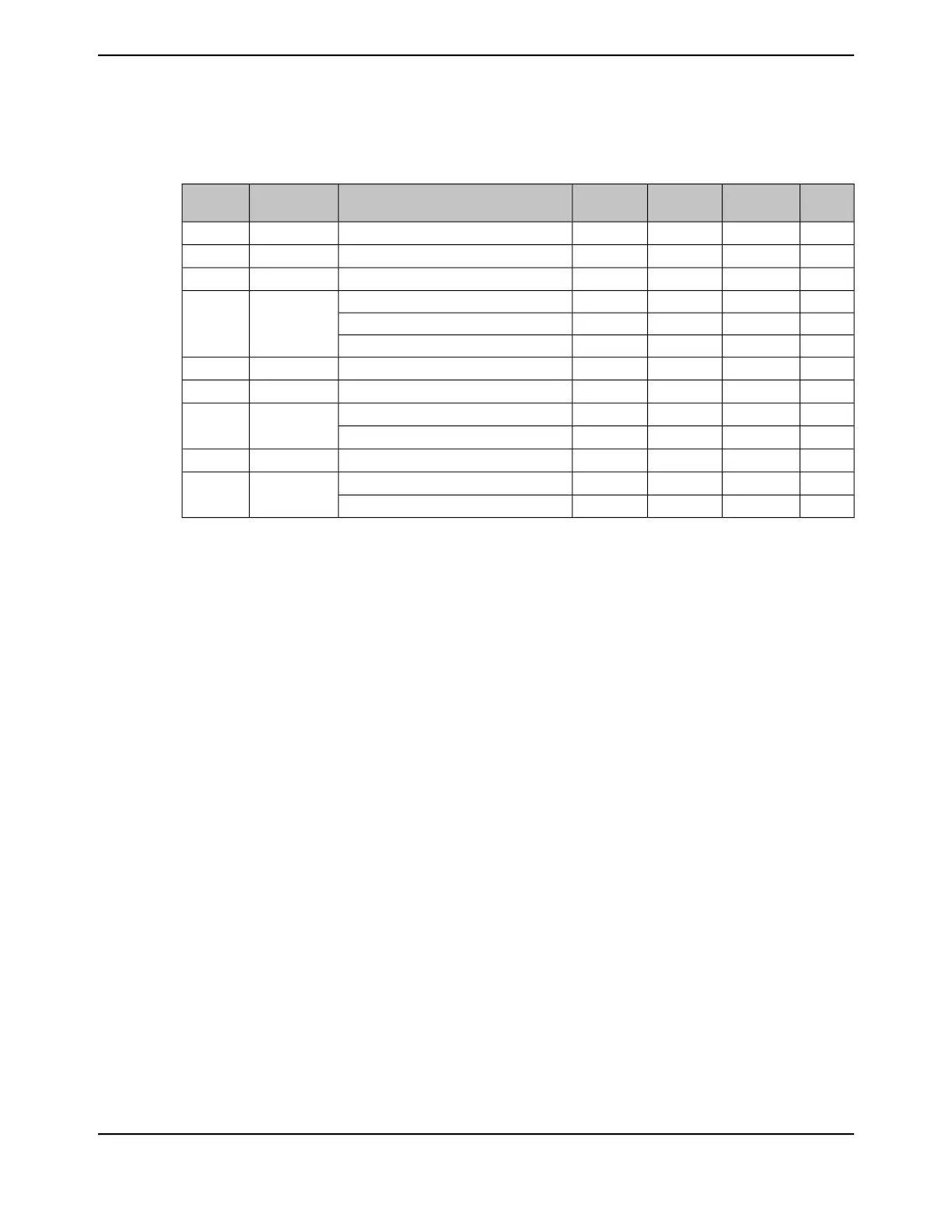

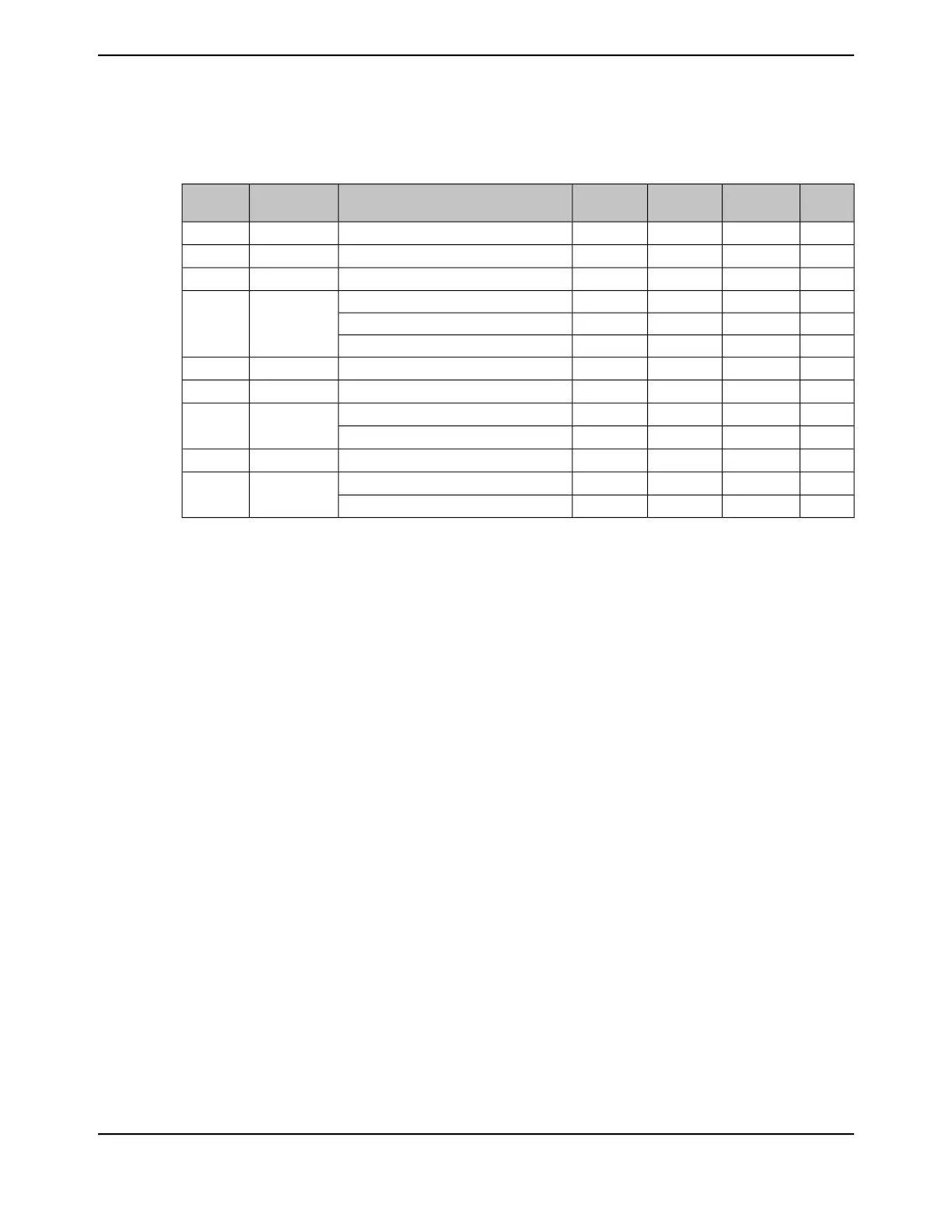

27.6 Power and Brown-Out

Table 27-13. Power and Brown-Out Levels

UnitMaxNomMinParameter NameParameterParameter

No.

µs∞--Analog Supply voltage (V

DDA

) rise timeT

VDDA_RISE

P1

µs∞--I/O Supply voltage (V

DD

) rise timeT

VDD_RISE

P2

µs150-10Core Supply Voltage (V

DDC

) rise timeT

VDDC_RISE

a

P3

V2.722.351.98Power-On Reset Threshold (Rising Edge)

V

POR

P4 V2.562.201.84Power-On Reset Threshold (Falling Edge)

V0.240.150.06Power-On Reset Hysteresis

V2.972.822.67V

DDA

Power-OK Threshold (Rising Edge)V

DDA_POK

P5

V2.892.802.71V

DDA

Brown-Out Reset ThresholdV

DDA_BOR0

P6

V2.902.802.65V

DD

Power-OK Threshold (Rising Edge)

V

DD_POK

P7

V2.852.762.67V

DD

Power-OK Threshold (Falling Edge)

V2.952.862.77V

DD

Brown-Out Reset ThresholdV

DD_BOR0

P8

V1.100.950.85V

DDC

Power-OK Threshold (Rising Edge)

V

DDC_POK

P9

V0.850.800.71V

DDC

Power-OK Threshold (Falling Edge)

a. The MIN and MAX values are based on an external filter capacitor load within the range of C

LDO

. Please refer to “On-Chip

Low Drop-Out (LDO) Regulator” on page 1834 for the C

LDO

value.

27.6.1 V

DDA

Levels

The V

DDA

supply has three monitors:

■ Power-On Reset (POR)

■ Power-OK (POK)

■ Brown Out Reset (BOR)

The POR monitor is used to keep the analog circuitry in reset until the V

DDA

supply has reached

the correct range for the analog circuitry to begin operating. The POK monitor is used to keep the

digital circuitry in reset until the V

DDA

power supply is at an acceptable operational level. The digital

reset is only released when the Power-On Reset has deasserted and all of the Power-OK monitors

for each of the supplies indicate that power levels are in operational ranges. The BOR monitor is

used to generate a reset to the device or assert an interrupt if the V

DDA

supply drops below its

operational range.

Note: V

DDA

BOR and V

DD

BOR events are a combined BOR to the system logic, such that if either

BOR event occurs, the following bits are affected:

■ BORRIS bit in the Raw Interrupt Status (RIS) register, System Control offset 0x050.

See page 261.

■ BORMIS bit in the Masked Interrupt Status and Clear (MISC) register, System Control

offset 0x058. This bit is set only if the BORIM bit in the Interrupt Mask Control (IMC)

register has been set. See page 263 and page 265.

June 18, 20141826

Texas Instruments-Production Data

Electrical Characteristics

Loading...

Loading...