■ BOR bit in the Reset Cause (RESC) register, System Control offset 0x05C. This bit is

set only if either of the BOR events have been configured to initiate a reset. See page 267.

In addition, the following bits control both BOR events:

■ BORIM bit in the Interrupt Mask Control (IMC) register, System Control offset 0x054.

■ VDDA_UBOR0 and VDD_UBOR0 bits in the Power-Temperature Cause (PWRTC) register.

Please refer to “System Control” on page 220 for more information on how to configure these

registers.

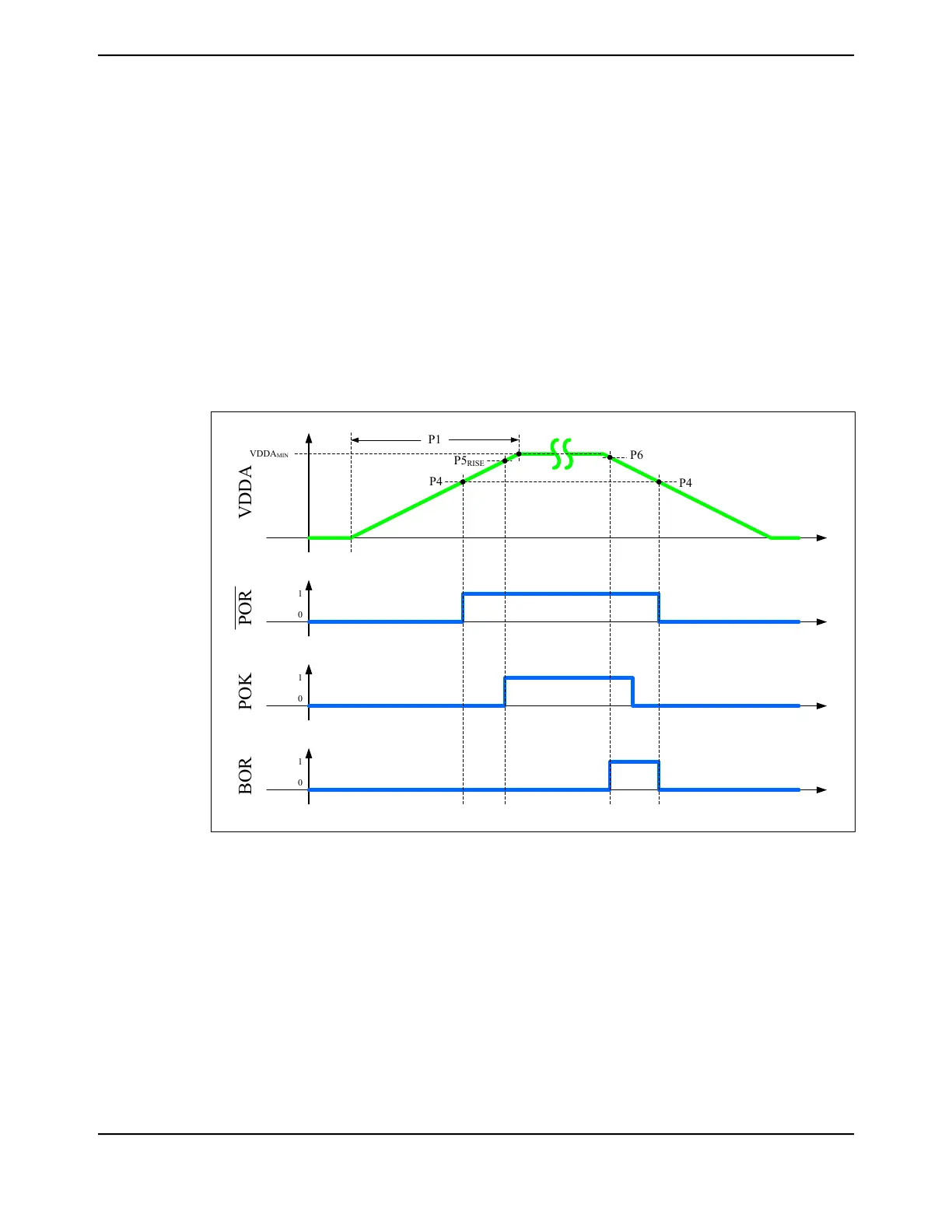

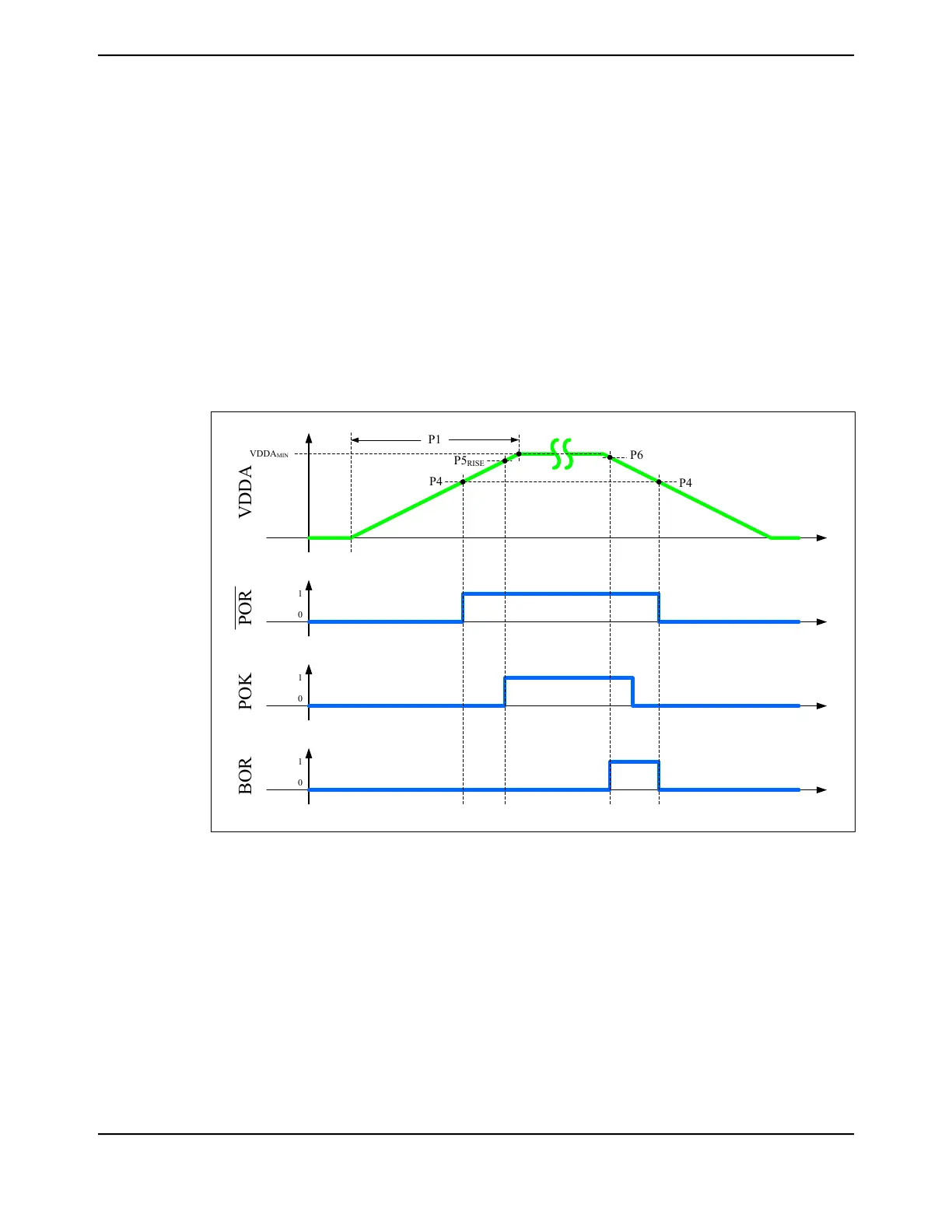

Figure 27-4 on page 1827 shows the relationship between V

DDA

, POK, POR and a BOR event.

Figure 27-4. Power and Brown-Out Assertions vs V

DDA

Levels

P1

VDDA

P5

RISE

P4

PORPOKBOR

P4

1

VDDA

MIN

1

1

0

0

0

P6

27.6.2 V

DD

Levels

The V

DD

supply has two monitors:

■ Power-OK (POK)

■ Brown Out Reset (BOR)

The POK monitor is used to keep the digital circuitry in reset until the V

DD

power supply is at an

acceptable operational level. The digital reset is only released when the Power-On Reset has

deasserted and all of the Power-OK monitors for each of the supplies indicate that power levels are

1827June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...