Register 3: Watchdog Control (WDTCTL), offset 0x008

This register is the watchdog control register. The watchdog timer can be configured to generate a

reset signal (on second time-out) or an interrupt on time-out.

When the watchdog interrupt has been enabled by setting the INTEN bit, all subsequent writes to

the INTEN bit are ignored. The only mechanisms that can re-enable writes to this bit are a hardware

reset or a software reset initiated by setting the appropriate bit in the Watchdog Timer Software

Reset (SRWD) register.

Important: Because the Watchdog Timer 1 module has an independent clocking domain, its

registers must be written with a timing gap between accesses. Software must guarantee

that this delay is inserted between back-to-back writes to WDT1 registers or between

a write followed by a read to the registers. The timing for back-to-back reads from the

WDT1 module has no restrictions. The WRC bit in the Watchdog Control (WDTCTL)

register for WDT1 indicates that the required timing gap has elapsed. This bit is cleared

on a write operation and set once the write completes, indicating to software that another

write or read may be started safely. Software should poll WDTCTL for WRC=1 prior to

accessing another register. Note that WDT0 does not have this restriction as it runs off

the system clock and therefore does not have a WRC bit.

Watchdog Control (WDTCTL)

WDT0 base: 0x4000.0000

WDT1 base: 0x4000.1000

Offset 0x008

Type RW, reset 0x0000.0000 (WDT0) and 0x8000.0000 (WDT1)

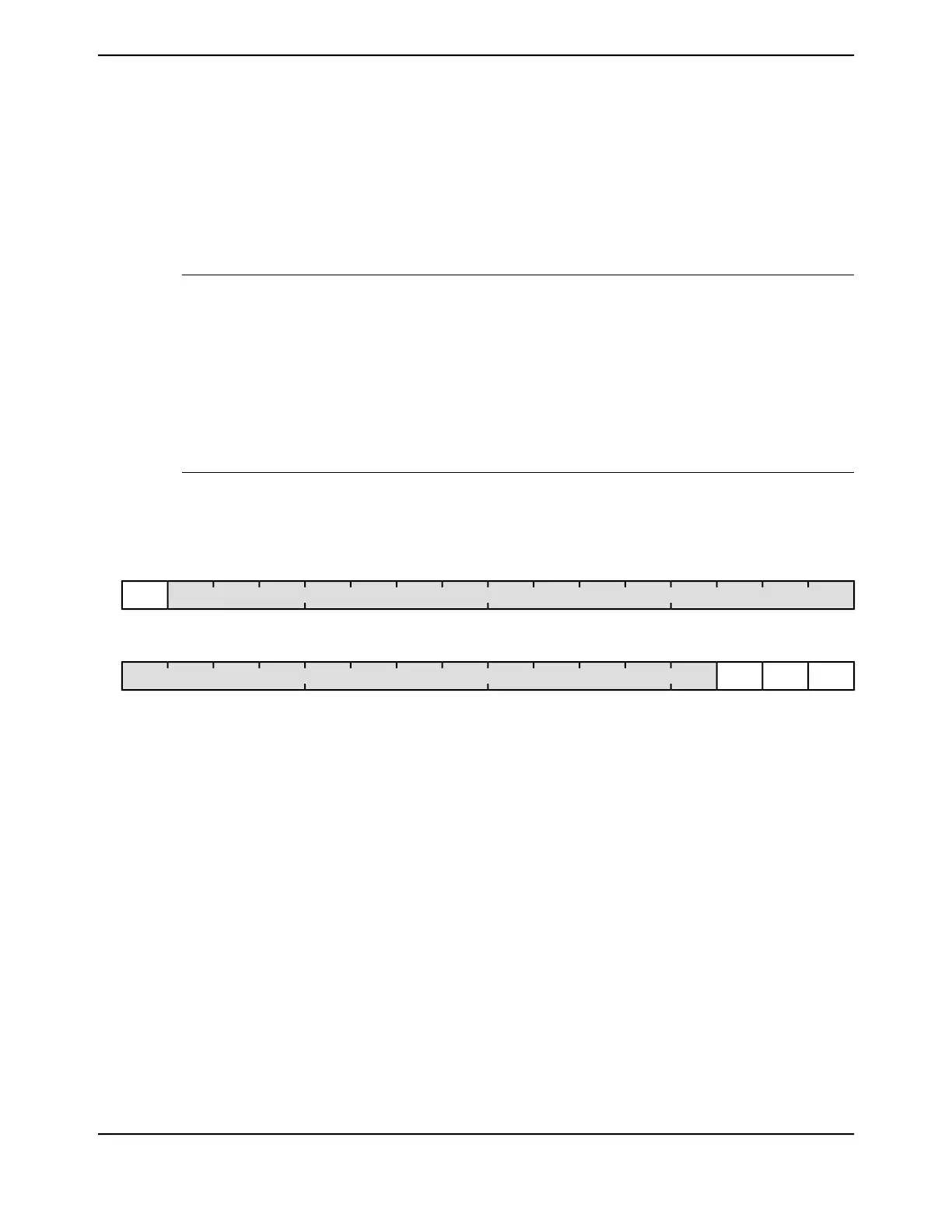

16171819202122232425262728293031

reservedWRC

ROROROROROROROROROROROROROROROROType

0000000000000001Reset

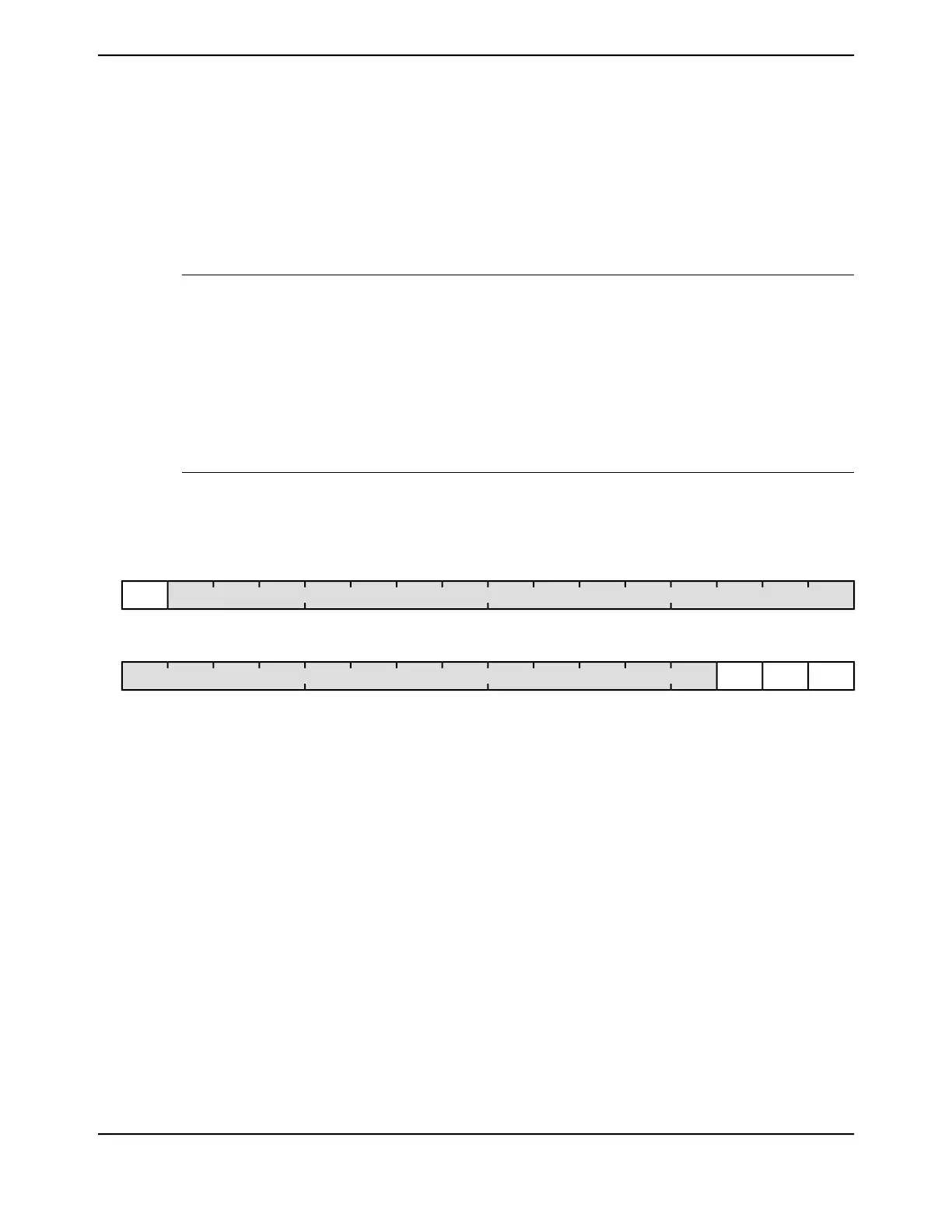

0123456789101112131415

INTENRESENINTTYPEreserved

RWRWRWROROROROROROROROROROROROROType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

Write Complete

The WRC values are defined as follows:

DescriptionValue

A write access to one of the WDT1 registers is in progress.0

A write access is not in progress, and WDT1 registers can be

read or written.

1

Note: This bit is reserved for WDT0 and has a reset value of 0.

1ROWRC31

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x000.000ROreserved30:3

June 18, 20141034

Texas Instruments-Production Data

Watchdog Timers

Loading...

Loading...