Register 12: Memory Timing Parameter Register 0 for Main Flash and EEPROM

(MEMTIM0), offset 0x0C0

The MEMTIM0 register provides timing parameters for the main Flash and EEPROM memories.

The timing parameters apply to the memory while the system is in run or sleep mode; the clocking

for these modes is consistent and unchanged since the system clock frequency and source remains

unchanged during transitions between run-to-sleep and sleep-back-to-run. Writes to MEMTIM0 do

not have any effect on system state; the register contents are applied only when the MEMTIMU bit

in the RSCLKCFG register is set. Doing so allows the software to execute out of the same memory

system for which the timing parameters are being modified.

Depending on the CPU frequency, the application must program specific values into the fields of

the Memory Timing Parameter Register 0 for Main Flash and EEPROM (MEMTIM0). The following

table details the bit field values that are required for the given CPU frequency ranges.

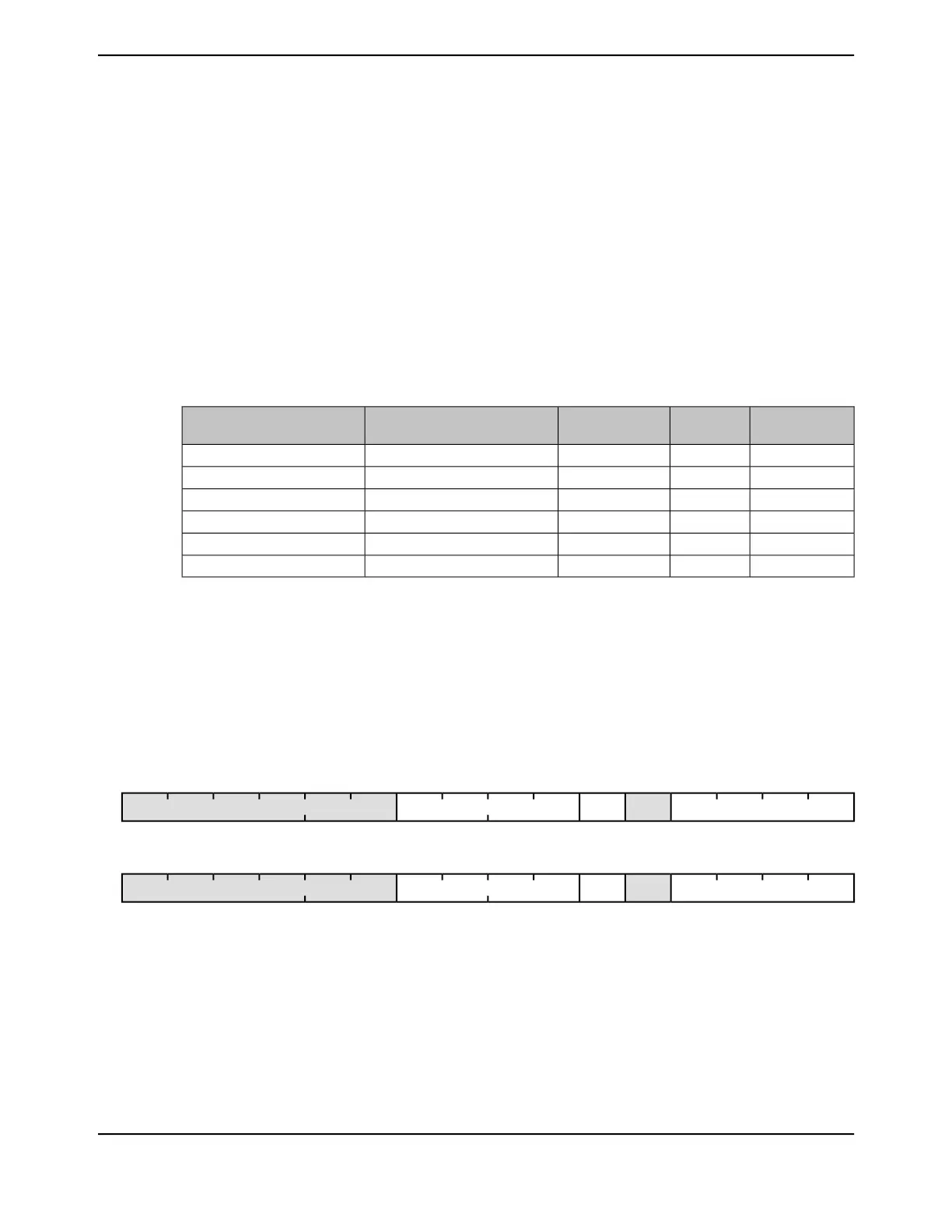

Table 5-12. MEMTIM0 Register Configuration versus Frequency

FWS/EWSFBCE/EBCEFBCHT/EBCHTTime Period Range (t) in nsCPU Frequency range (f) in

MHz

0x010x062.516

0x100x262.5 > t ≥ 2516 < f ≤ 40

0x200x325 > t ≥ 16.6740 < f ≤60

0x300x416.67 > t ≥ 12.560< f ≤80

0x400x512.5 > t ≥ 1080 < f ≤100

0x500x610 > t ≥ 8.33100< f ≤120

Note: The associated Flash and EEPROM fields in the MEMTIM0 register must be programmed

to the same values. For example, the FWS field must be programmed to the same value as

the EWS field.

Refer to “Flash Memory” on page 604 and “EEPROM” on page 615 for more information about Flash

and EEPROM programming.

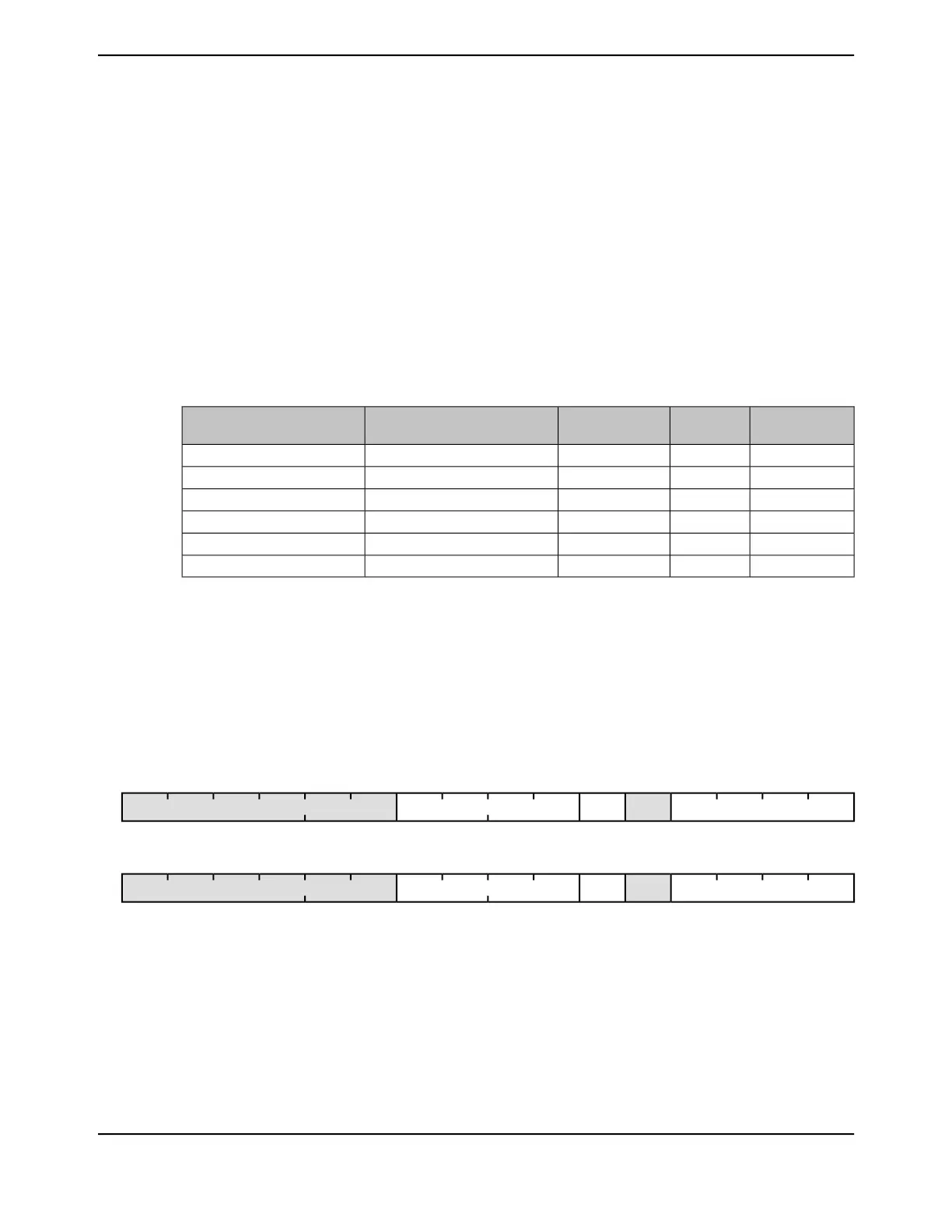

Memory Timing Parameter Register 0 for Main Flash and EEPROM (MEMTIM0)

Base 0x400F.E000

Offset 0x0C0

Type RW, reset 0x0030.0030

16171819202122232425262728293031

EWSreservedEBCEEBCHTreserved

RWRWRWRWRWRWRWRWRWRWROROROROROROType

0000110000000000Reset

0123456789101112131415

FWSreservedFBCEFBCHTreserved

RWRWRWRWRWRWRWRWRWRWRWRWRWRWRWRWType

0000110000000000Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0000.000ROreserved31:26

277June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...