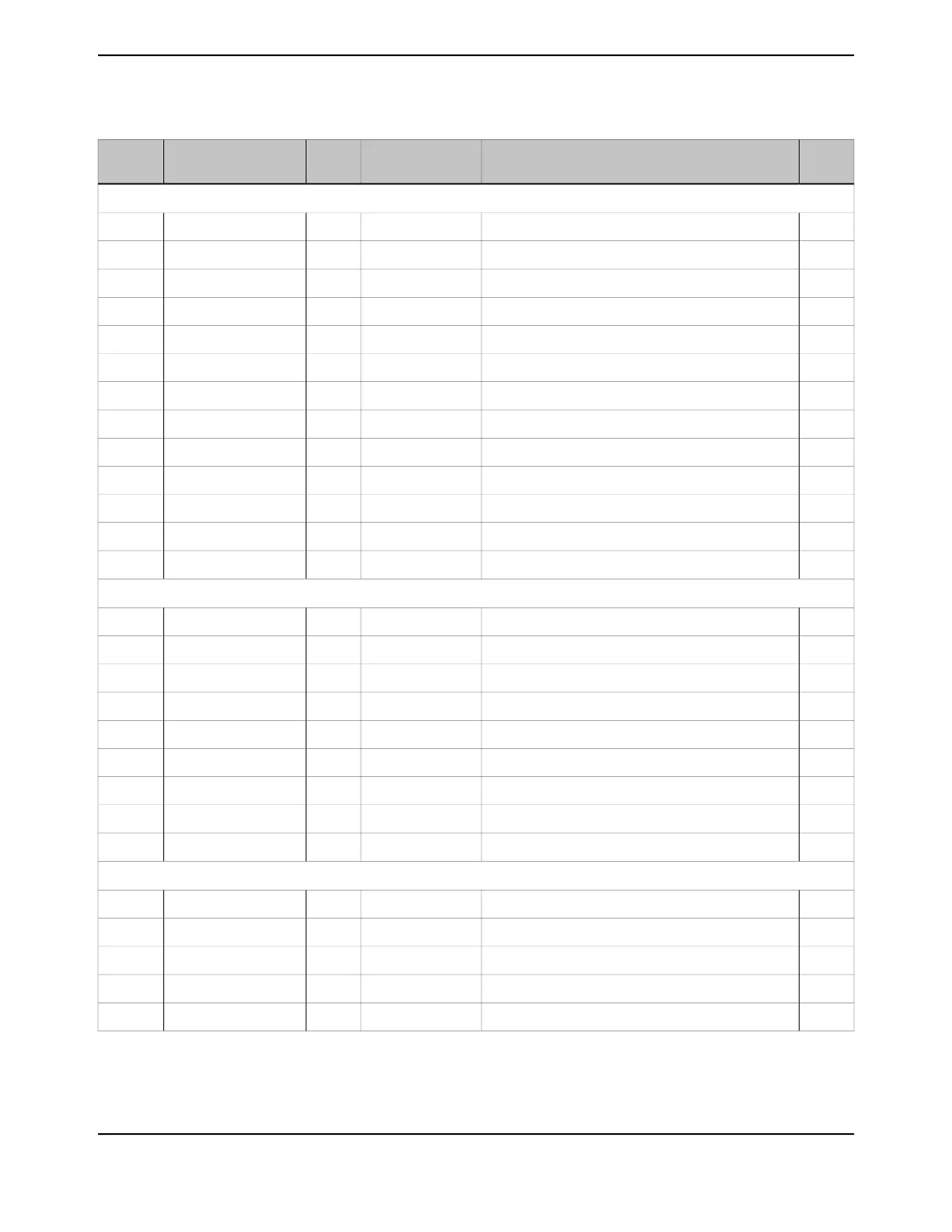

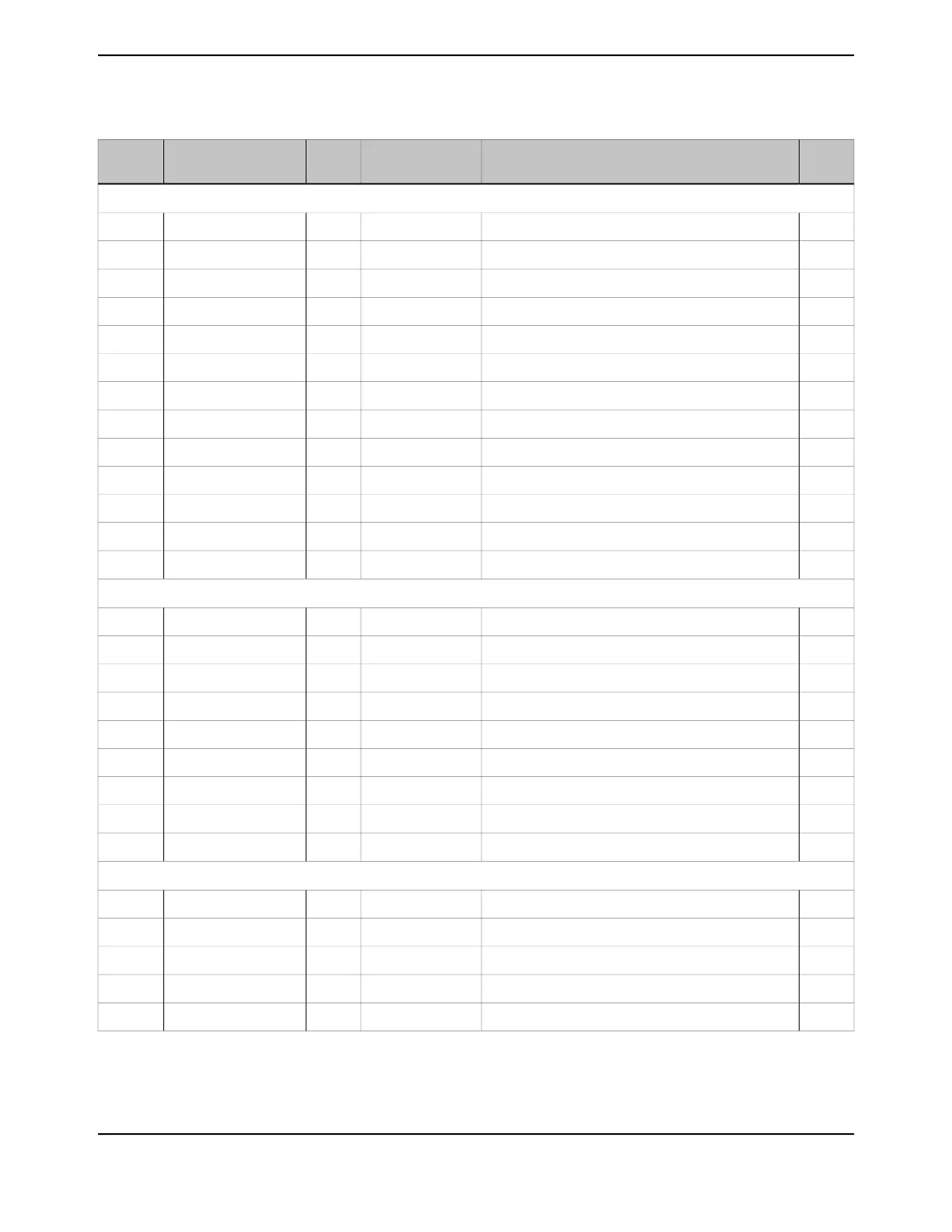

Table 18-4. Inter-Integrated Circuit (I

2

C) Interface Register Map

See

page

DescriptionResetTypeNameOffset

I

2

C Master

1302I2C Master Slave Address0x0000.0000RWI2CMSA0x000

1303I2C Master Control/Status0x0000.0020RWI2CMCS0x004

1312I2C Master Data0x0000.0000RWI2CMDR0x008

1313I2C Master Timer Period0x0000.0001RWI2CMTPR0x00C

1315I2C Master Interrupt Mask0x0000.0000RWI2CMIMR0x010

1318I2C Master Raw Interrupt Status0x0000.0000ROI2CMRIS0x014

1321I2C Master Masked Interrupt Status0x0000.0000ROI2CMMIS0x018

1324I2C Master Interrupt Clear0x0000.0000WOI2CMICR0x01C

1326I2C Master Configuration0x0000.0000RWI2CMCR0x020

1327I2C Master Clock Low Timeout Count0x0000.0000RWI2CMCLKOCNT0x024

1328I2C Master Bus Monitor0x0000.0003ROI2CMBMON0x02C

1329I2C Master Burst Length0x0000.0000RWI2CMBLEN0x030

1330I2C Master Burst Count0x0000.0000ROI2CMBCNT0x034

I

2

C Slave

1331I2C Slave Own Address0x0000.0000RWI2CSOAR0x800

1332I2C Slave Control/Status0x0000.0000ROI2CSCSR0x804

1335I2C Slave Data0x0000.0000RWI2CSDR0x808

1336I2C Slave Interrupt Mask0x0000.0000RWI2CSIMR0x80C

1338I2C Slave Raw Interrupt Status0x0000.0000ROI2CSRIS0x810

1341I2C Slave Masked Interrupt Status0x0000.0000ROI2CSMIS0x814

1344I2C Slave Interrupt Clear0x0000.0000WOI2CSICR0x818

1346I2C Slave Own Address 20x0000.0000RWI2CSOAR20x81C

1347I2C Slave ACK Control0x0000.0000RWI2CSACKCTL0x820

I

2

C Status and Control

1348I2C FIFO Data0x0000.0000RWI2CFIFODATA0xF00

1350I2C FIFO Control0x0004.0004RWI2CFIFOCTL0xF04

1352I2C FIFO Status0x0001.0005ROI2CFIFOSTATUS0xF08

1354I2C Peripheral Properties0x0000.0001ROI2CPP0xFC0

1355I2C Peripheral Configuration0x0000.0001ROI2CPC0xFC4

June 18, 20141300

Texas Instruments-Production Data

Inter-Integrated Circuit (I

2

C) Interface

Loading...

Loading...