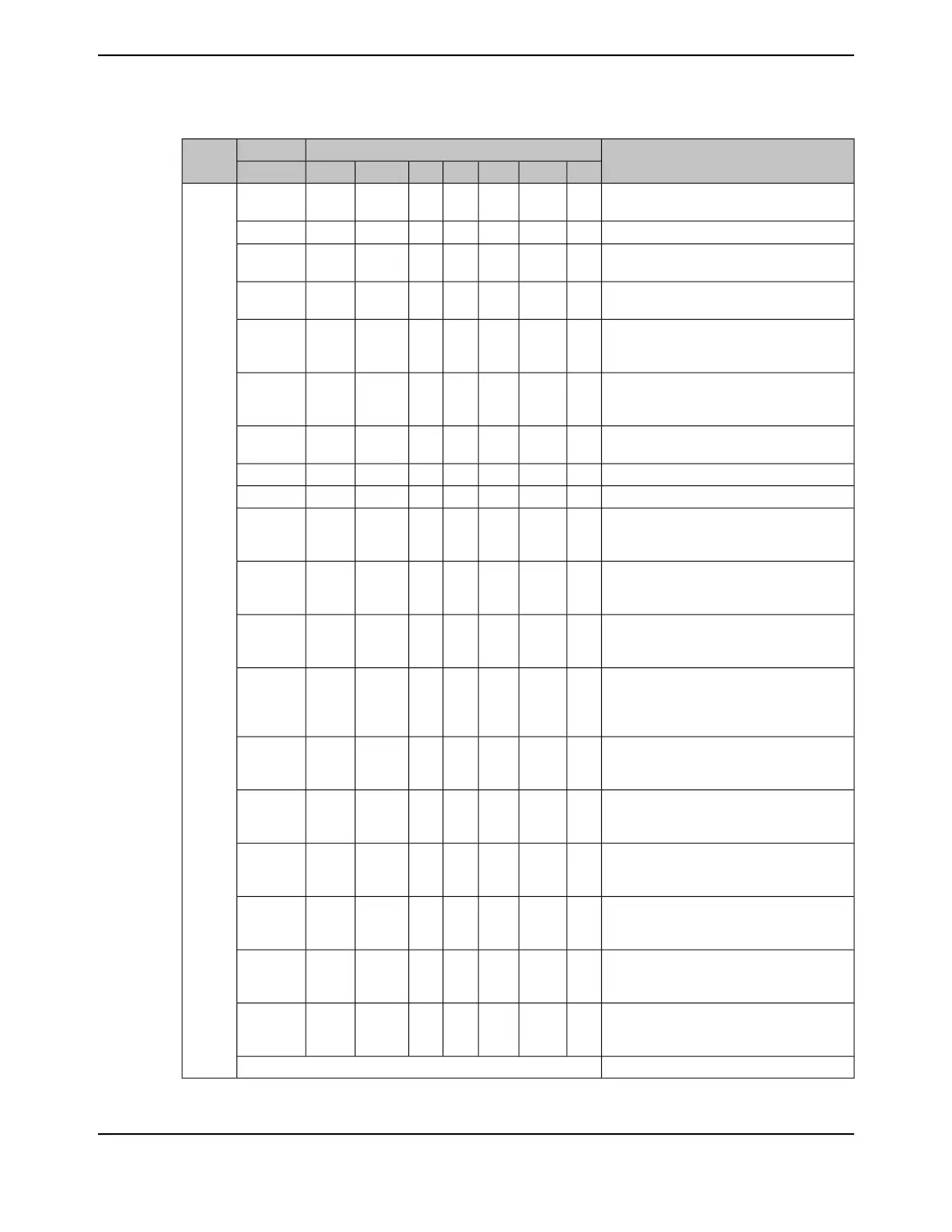

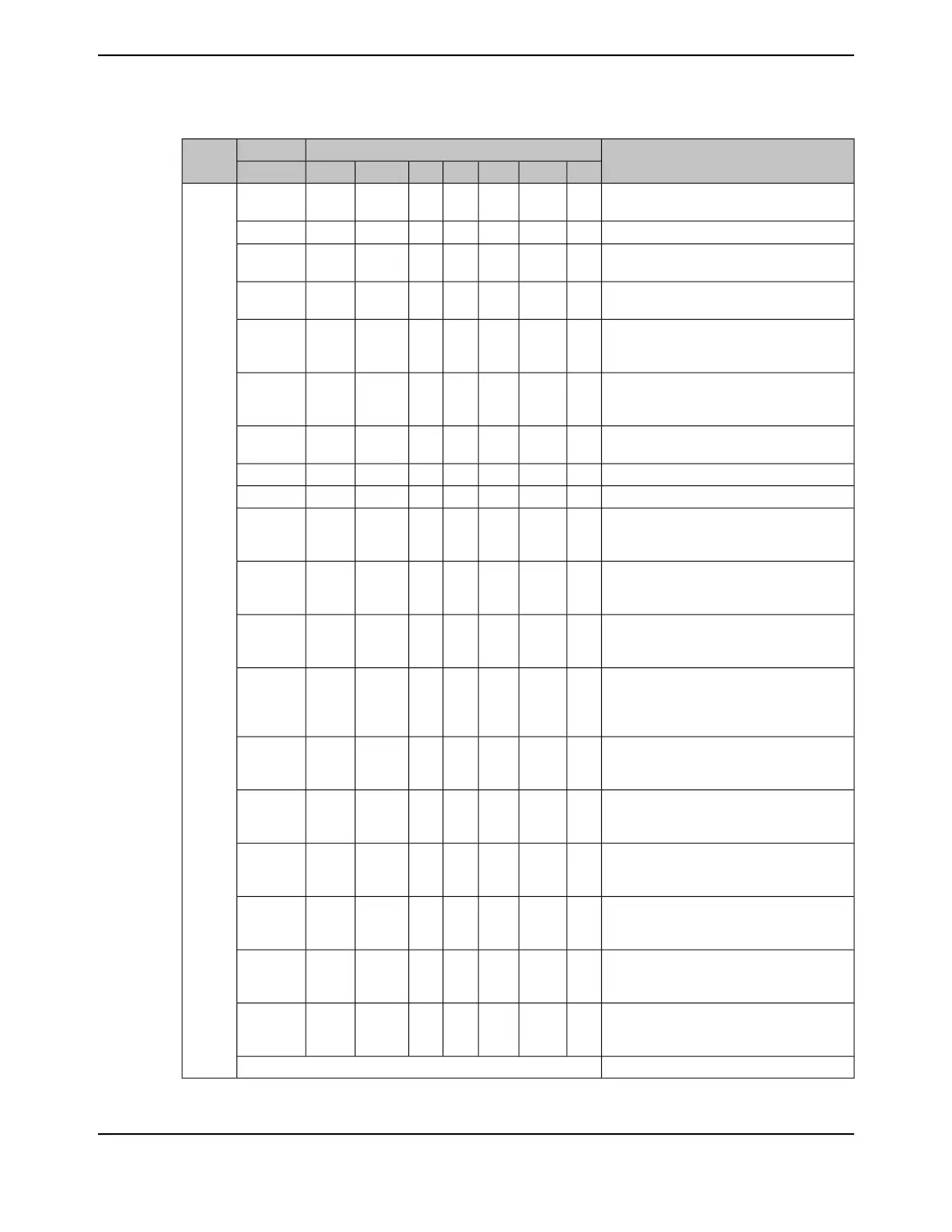

Table 18-5. Write Field Decoding for I2CMCS[6:0] (continued)

Next State Description

I2CMCS[6:0]I2CMSA[0]

Current

State

RUNSTARTSTOPACKHSQCCMDBURSTR/S

RECEIVE operation with negative ACK

(master remains in Master Receive state).

1000000X

Master

Receive

STOP condition (master goes to Idle state).

b

001X000X

RECEIVE followed by STOP condition (master

goes to Idle state).

1010000X

RECEIVE operation (master remains in Master

Receive state).

1001000X

N FIFO-serviced RECEIVE operations with

negative ACK on the last RECEIVE (master

remains in Master Receive state).

0000001X

N FIFO-serviced RECEIVE operations

followed by STOP condition (master goes to

Idle state).

0010001X

N FIFO-serviced RECEIVE operations (master

remains in Master Receive state).

0001001X

Illegal.1011000X

Illegal.0011001X

Repeated START condition followed by

RECEIVE operation with a negative ACK

(master remains in Master Receive state).

11000001

Repeated START condition followed by

RECEIVE and STOP condition (master goes

to Idle state).

11100001

Repeated START condition followed by

RECEIVE (master remains in Master Receive

state).

11010001

Repeated START condition followed by N

FIFO-serviced RECEIVE operations with a

negative ACK on the last RECEIVE (master

remains in Master Receive state).

01000011

Repeated START condition followed by N

FIFO-serviced RECEIVE operations and

STOP condition (master goes to Idle state).

01100011

Repeated START condition followed by N

FIFO-serviced RECEIVE operations (master

remains in Master Receive state).

01010011

Repeated START condition followed by

TRANSMIT (master goes to Master Transmit

state).

110X0000

Repeated START condition followed by

TRANSMIT and STOP condition (master goes

to Idle state).

111X0000

Repeated START condition followed by N

FIFO-serviced TRANSMIT operations (master

goes to Master Transmit state).

010X0010

Repeated START condition followed by N

FIFO-serviced TRANSMIT operations and

STOP condition (master goes to Idle state).

011X0010

NOP.All other combinations not listed are non-operations.

a. An X in a table cell indicates the bit can be 0 or 1.

June 18, 20141310

Texas Instruments-Production Data

Inter-Integrated Circuit (I

2

C) Interface

Loading...

Loading...