GPIO Port Control (GPIOPCTL)

GPIO Port A (AHB) base: 0x4005.8000

GPIO Port B (AHB) base: 0x4005.9000

GPIO Port C (AHB) base: 0x4005.A000

GPIO Port D (AHB) base: 0x4005.B000

GPIO Port E (AHB) base: 0x4005.C000

GPIO Port F (AHB) base: 0x4005.D000

GPIO Port G (AHB) base: 0x4005.E000

GPIO Port H (AHB) base: 0x4005.F000

GPIO Port J (AHB) base: 0x4006.0000

GPIO Port K (AHB) base: 0x4006.1000

GPIO Port L (AHB) base: 0x4006.2000

GPIO Port M (AHB) base: 0x4006.3000

GPIO Port N (AHB) base: 0x4006.4000

GPIO Port P (AHB) base: 0x4006.5000

GPIO Port Q (AHB) base: 0x4006.6000

Offset 0x52C

Type RW, reset -

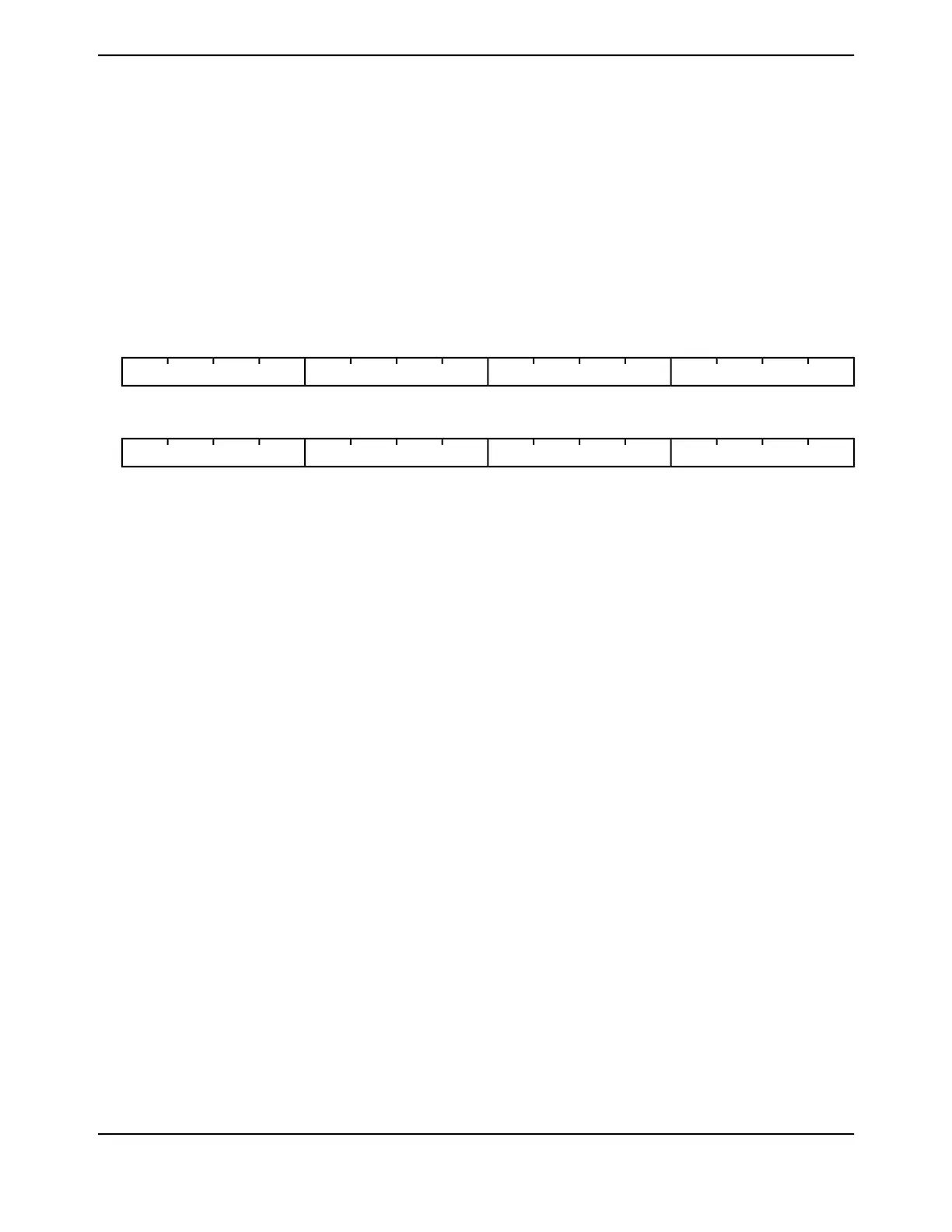

16171819202122232425262728293031

PMC4PMC5PMC6PMC7

RWRWRWRWRWRWRWRWRWRWRWRWRWRWRWRWType

----------------Reset

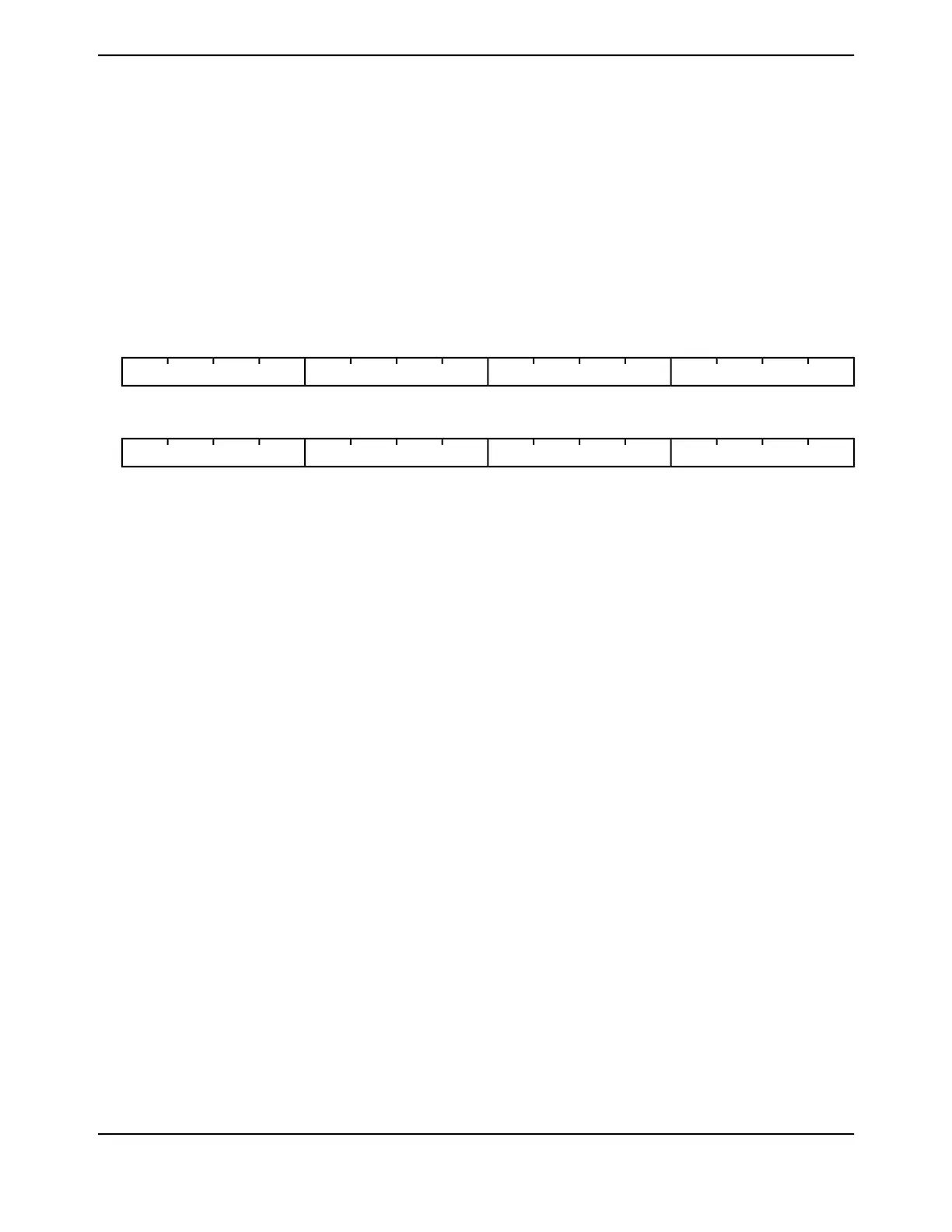

0123456789101112131415

PMC0PMC1PMC2PMC3

RWRWRWRWRWRWRWRWRWRWRWRWRWRWRWRWType

----------------Reset

DescriptionResetTypeNameBit/Field

Port Mux Control 7

This field controls the configuration for GPIO pin 7.

-RWPMC731:28

Port Mux Control 6

This field controls the configuration for GPIO pin 6.

-RWPMC627:24

Port Mux Control 5

This field controls the configuration for GPIO pin 5.

-RWPMC523:20

Port Mux Control 4

This field controls the configuration for GPIO pin 4.

-RWPMC419:16

Port Mux Control 3

This field controls the configuration for GPIO pin 3.

-RWPMC315:12

Port Mux Control 2

This field controls the configuration for GPIO pin 2.

-RWPMC211:8

Port Mux Control 1

This field controls the configuration for GPIO pin 1.

-RWPMC17:4

Port Mux Control 0

This field controls the configuration for GPIO pin 0.

-RWPMC03:0

June 18, 2014788

Texas Instruments-Production Data

General-Purpose Input/Outputs (GPIOs)

Loading...

Loading...