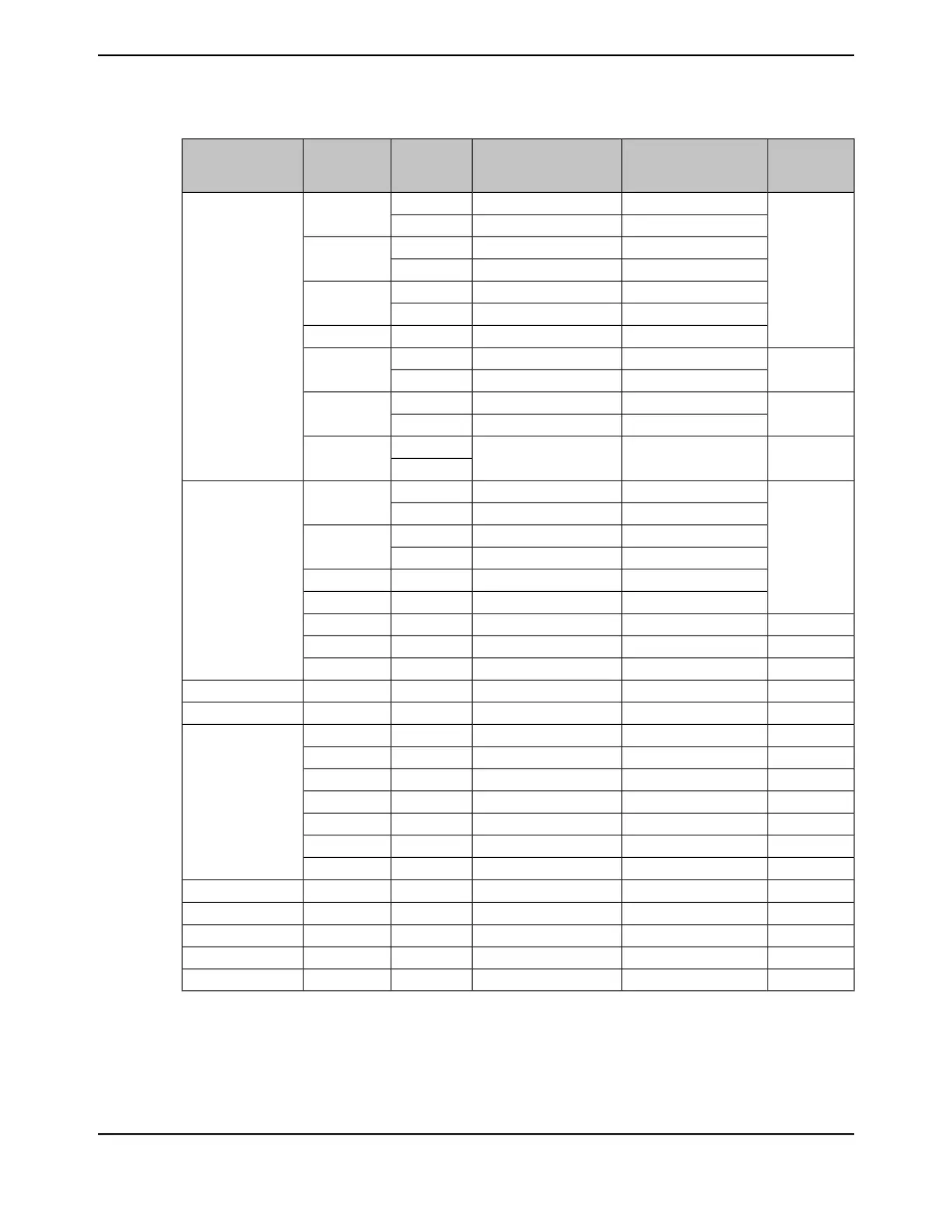

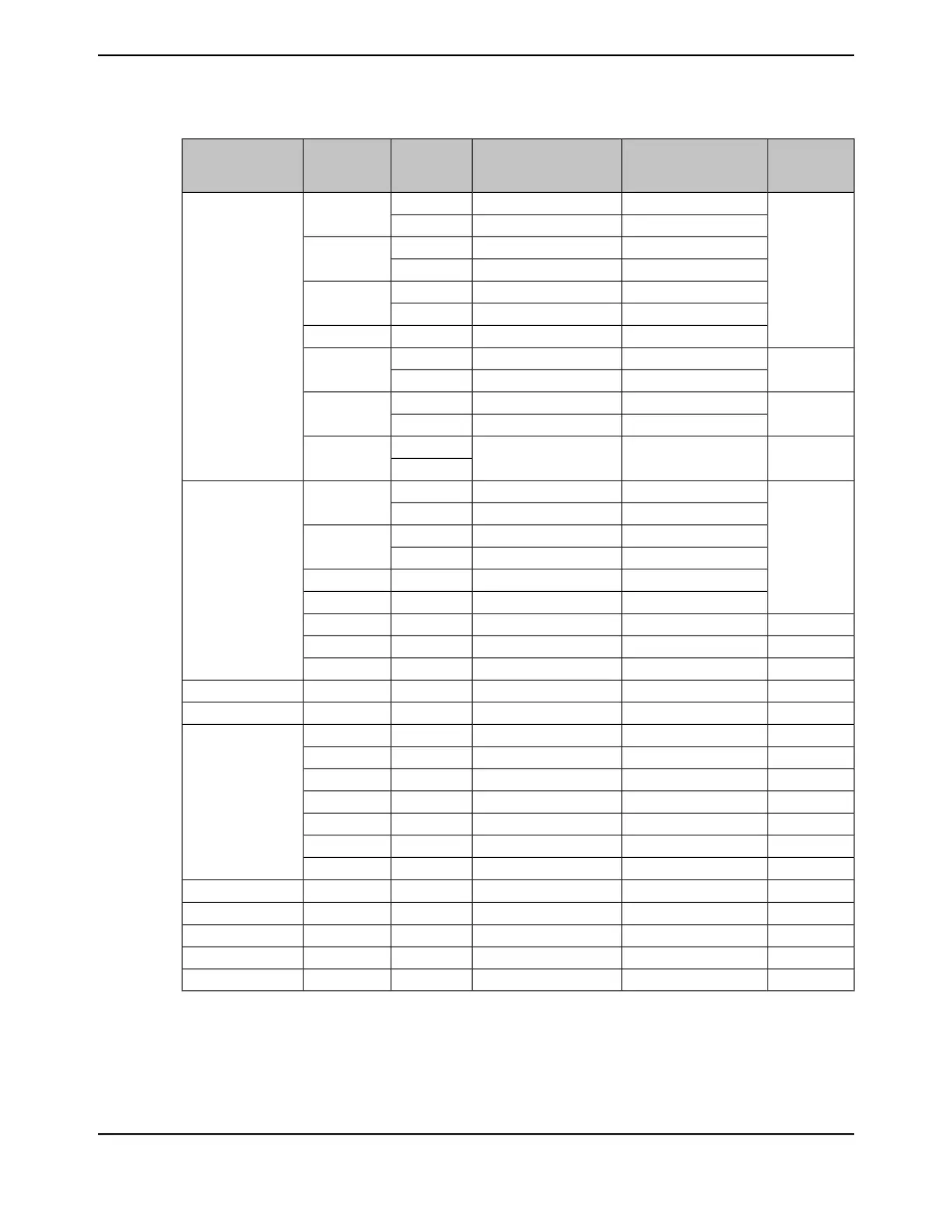

Table 11-9. EPI Host-Bus 16 Signal Connections (continued)

HB16 Signal

(MODE

=XFIFO)

HB16 Signal (MODE

=ADNOMUX (Cont.

Read))

HB16 Signal (MODE

=ADMUX)

BSELCSCFGEPI Signal

FEMPTY

A10A260

0x0

EPI0S26

BSEL0nBSEL0n1

A10A260

0x1

BSEL0nBSEL0n1

A10A260

0x2

BSEL1nBSEL1n1

CS0nCS0nX0x3

-

A10A260

0x4

BSEL1nBSEL1n1

-

A10A260

0x5

BSEL1nBSEL1n1

-CS0nCS0n

0

0x6

1

FFULL

A11A270

0x0

EPI0S27

BSEL1nBSEL1n1

A11A270

0x1

BSEL1nBSEL1n1

CS1nCS1nX0x2

CS1nCS1nX0x3

-CS0nCS0nX0x4

-CS1nCS1nX0x5

-CS1nCS1nX0x6

RDnRDn/OEnRDn/OEnXXEPI0S28

WRnWRnWRnXXEPI0S29

-ALEALEX0x0

EPI0S30

CSnCSnCSnX0x1

CS0nCS0nCS0nX0x2

-ALEALEX0x3

-ALEALEX0x4

-CS0nCS0nX0x5

-ALEALEX0x6

Clock

d

Clock

d

Clock

d

XXEPI0S31

iRDYiRDYiRDYXXEPI0S32

XCS3nCS3nXXEPI0S33

XCS2nCS2nXXEPI0S34

XCRECREXXEPI0S35

a. "X" indicates the state of this field is a don't care.

b. In this mode, half-word accesses are used. A0 is the LSB of the address and is equivalent to the internal Cortex-M3 A1

address. This pin should be connected to A0 of 16-bit memories.

c. When an entry straddles several row, the signal configuration is the same for all rows.

d. The clock signal is not required for this mode.

835June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...