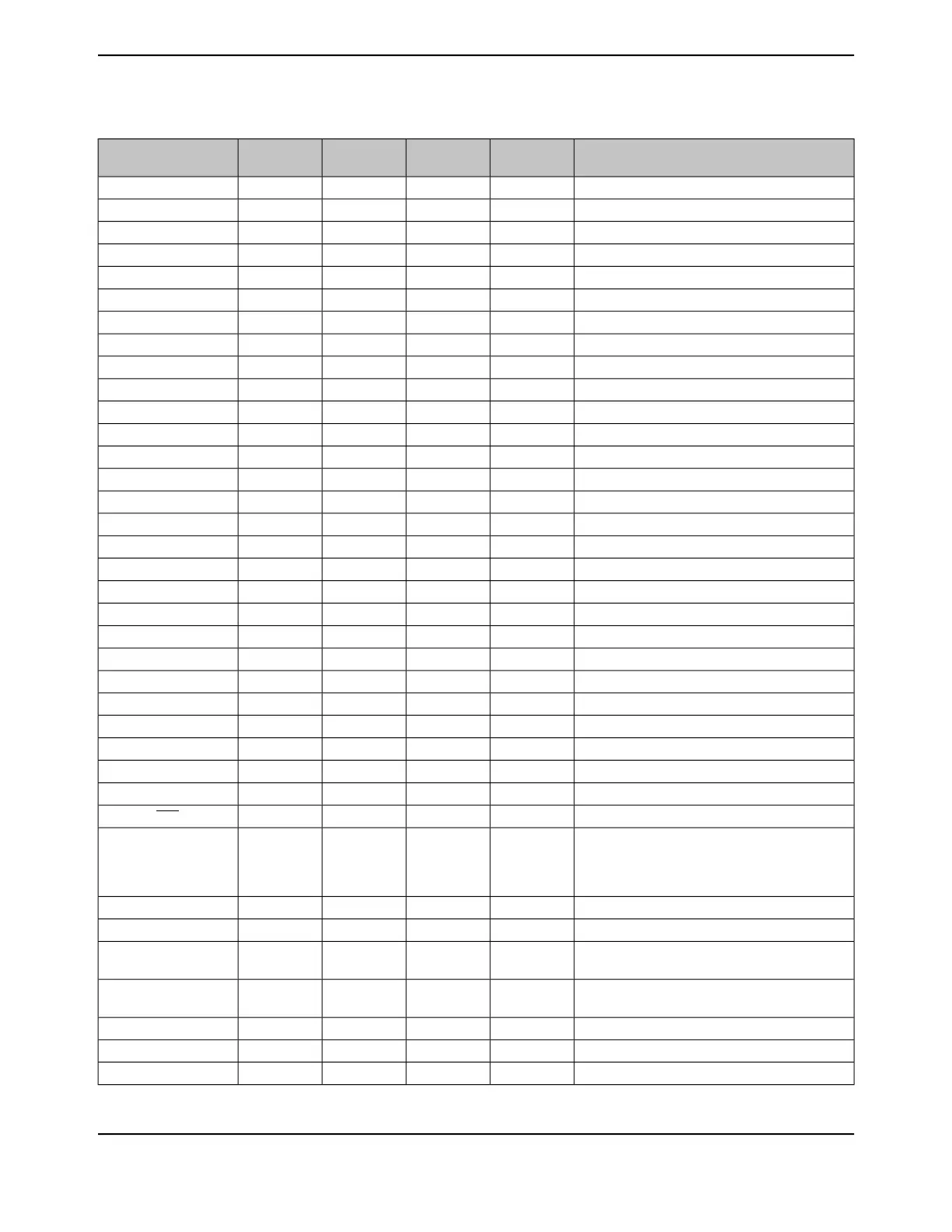

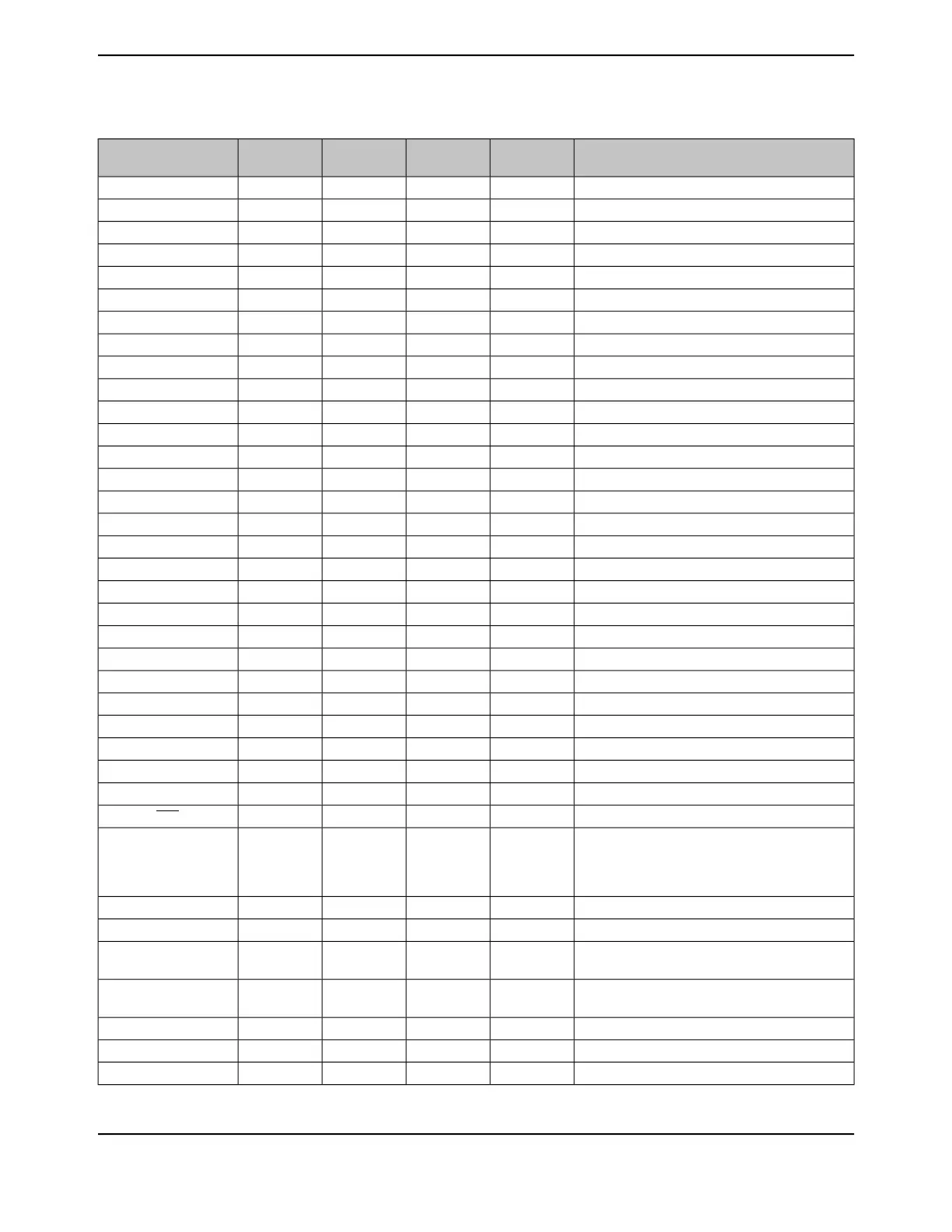

Table 26-3. Signals by Signal Name (continued)

DescriptionBuffer TypePin TypePin Mux / Pin

Assignment

Pin NumberPin Name

GPIO port L bit 6.TTLI/O-94PL6

GPIO port L bit 7.TTLI/O-93PL7

GPIO port M bit 0.TTLI/O-78PM0

GPIO port M bit 1.TTLI/O-77PM1

GPIO port M bit 2.TTLI/O-76PM2

GPIO port M bit 3.TTLI/O-75PM3

GPIO port M bit 4.TTLI/O-74PM4

GPIO port M bit 5.TTLI/O-73PM5

GPIO port M bit 6.TTLI/O-72PM6

GPIO port M bit 7.TTLI/O-71PM7

GPIO port N bit 0.TTLI/O-107PN0

GPIO port N bit 1.TTLI/O-108PN1

GPIO port N bit 2.TTLI/O-109PN2

GPIO port N bit 3.TTLI/O-110PN3

GPIO port N bit 4.TTLI/O-111PN4

GPIO port N bit 5.TTLI/O-112PN5

GPIO port P bit 0.TTLI/O-118PP0

GPIO port P bit 1.TTLI/O-119PP1

GPIO port P bit 2.TTLI/O-103PP2

GPIO port P bit 3.TTLI/O-104PP3

GPIO port P bit 4.TTLI/O-105PP4

GPIO port P bit 5.TTLI/O-106PP5

GPIO port Q bit 0.TTLI/O-5PQ0

GPIO port Q bit 1.TTLI/O-6PQ1

GPIO port Q bit 2.TTLI/O-11PQ2

GPIO port Q bit 3.TTLI/O-27PQ3

GPIO port Q bit 4.TTLI/O-102PQ4

4.87-kΩ resistor (1% precision) for Ethernet PHY.AnalogOfixed59RBIAS

System reset input.TTLIfixed70RST

Buffered version of the Hibernation module's

32.768-kHz clock. This signal is not output when

the part is in Hibernate mode and before being

configured after power-on reset.

TTLOPC5 (7)

PK7 (5)

PP3 (7)

24

60

104

RTCCLK

SSI module 0 clockTTLI/OPA2 (15)35SSI0Clk

SSI module 0 frame signalTTLI/OPA3 (15)36SSI0Fss

SSI Module 0 Bi-directional Data Pin 0 (SSI0TX in

Legacy SSI Mode).

TTLI/OPA4 (15)37SSI0XDAT0

SSI Module 0 Bi-directional Data Pin 1 (SSI0RX in

Legacy SSI Mode).

TTLI/OPA5 (15)38SSI0XDAT1

SSI Module 0 Bi-directional Data Pin 2.TTLI/OPA6 (13)40SSI0XDAT2

SSI Module 0 Bi-directional Data Pin 3.TTLI/OPA7 (13)41SSI0XDAT3

SSI module 1 clock.TTLI/OPB5 (15)120SSI1Clk

1791June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...