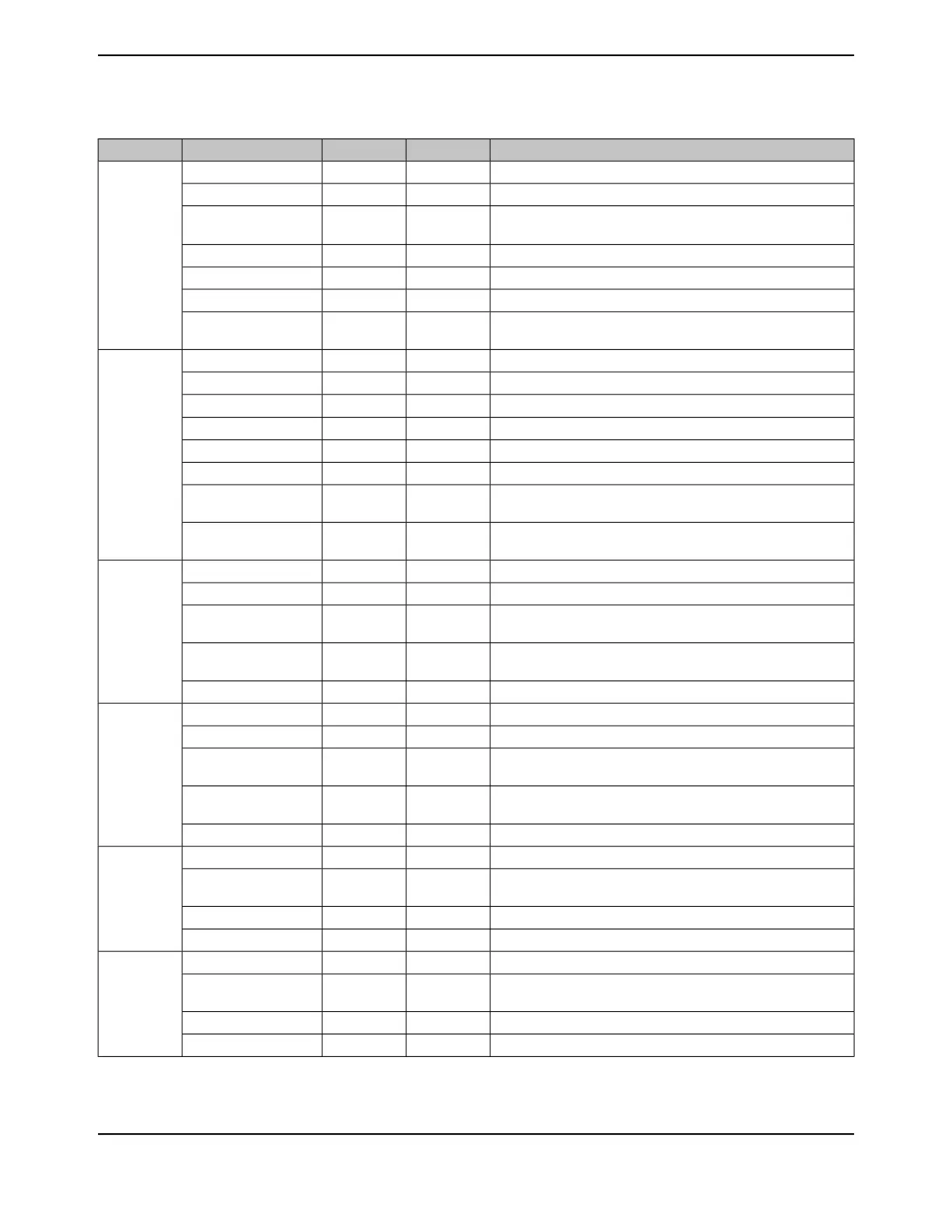

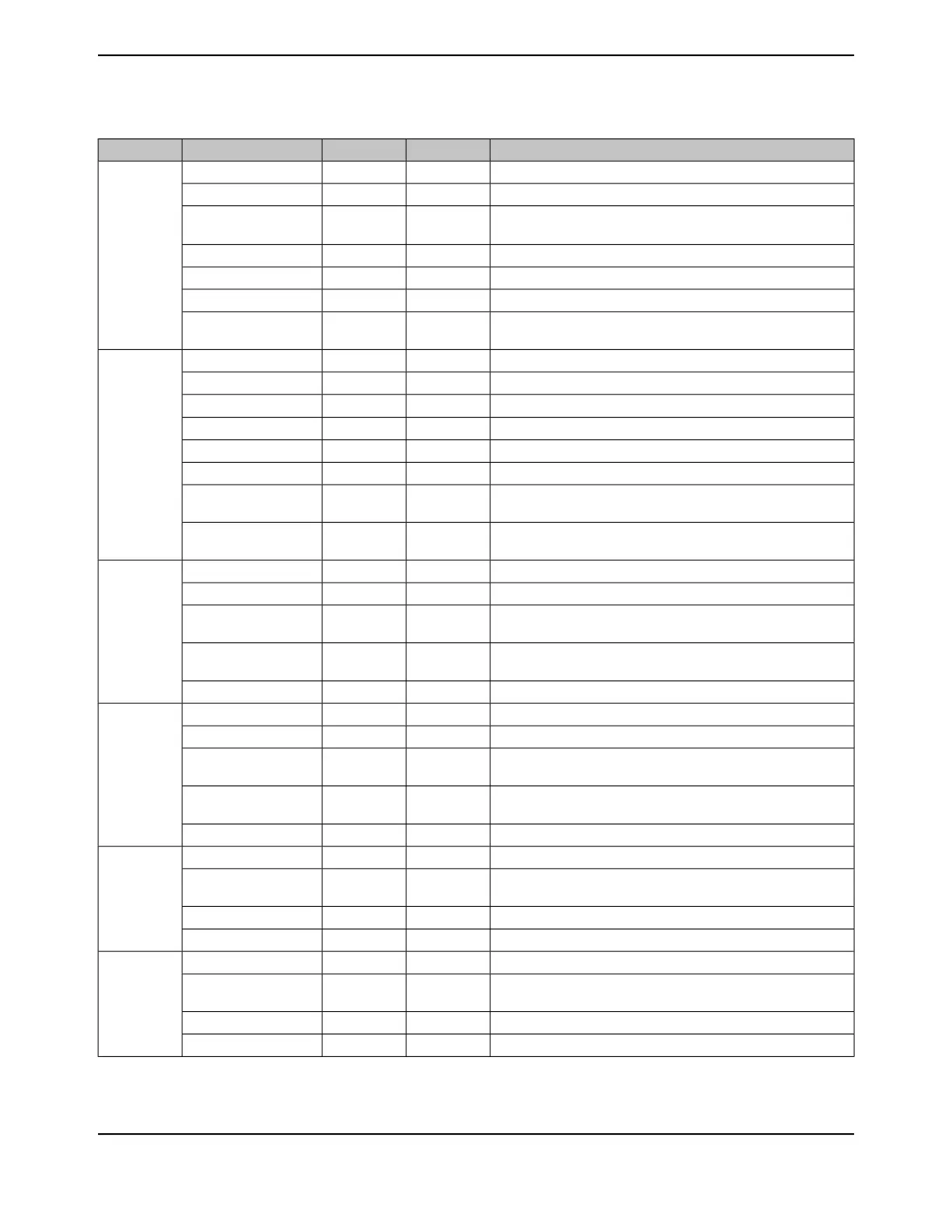

Table 26-2. Signals by Pin Number (continued)

DescriptionBuffer TypePin TypePin NamePin Number

GPIO port A bit 6.TTLI/OPA6

40

EPI module 0 signal 8.TTLI/OEPI0S8

I

2

C module 6 clock. Note that this signal has an active pull-up. The

corresponding port pin should not be configured as open drain.

ODI/OI2C6SCL

SSI Module 0 Bi-directional Data Pin 2.TTLI/OSSI0XDAT2

16/32-Bit Timer 3 Capture/Compare/PWM 0.TTLI/OT3CCP0

UART module 2 receive.TTLIU2Rx

Optionally used in Host mode to control an external power source

to supply power to the USB bus.

TTLOUSB0EPEN

GPIO port A bit 7.TTLI/OPA7

41

EPI module 0 signal 9.TTLI/OEPI0S9

I

2

C module 6 data.ODI/OI2C6SDA

SSI Module 0 Bi-directional Data Pin 3.TTLI/OSSI0XDAT3

16/32-Bit Timer 3 Capture/Compare/PWM 1.TTLI/OT3CCP1

UART module 2 transmit.TTLOU2Tx

Optionally used in Host mode to control an external power source

to supply power to the USB bus.

TTLOUSB0EPEN

Optionally used in Host mode by an external power source to

indicate an error state by that power source.

TTLIUSB0PFLT

GPIO port F bit 0.TTLI/OPF0

42

Ethernet 0 LED 0.TTLOEN0LED0

Motion Control Module 0 PWM 0. This signal is controlled by

Module 0 PWM Generator 0.

TTLOM0PWM0

SSI Module 3 Bi-directional Data Pin 1 (SSI3RX in Legacy SSI

Mode).

TTLI/OSSI3XDAT1

Trace data 2.TTLOTRD2

GPIO port F bit 1.TTLI/OPF1

43

Ethernet 0 LED 2.TTLOEN0LED2

Motion Control Module 0 PWM 1. This signal is controlled by

Module 0 PWM Generator 0.

TTLOM0PWM1

SSI Module 3 Bi-directional Data Pin 0 (SSI3TX in Legacy SSI

Mode).

TTLI/OSSI3XDAT0

Trace data 1.TTLOTRD1

GPIO port F bit 2.TTLI/OPF2

44

Motion Control Module 0 PWM 2. This signal is controlled by

Module 0 PWM Generator 1.

TTLOM0PWM2

SSI module 3 frame signal.TTLI/OSSI3Fss

Trace data 0.TTLOTRD0

GPIO port F bit 3.TTLI/OPF3

45

Motion Control Module 0 PWM 3. This signal is controlled by

Module 0 PWM Generator 1.

TTLOM0PWM3

SSI module 3 clock.TTLI/OSSI3Clk

Trace clock.TTLOTRCLK

1777June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...