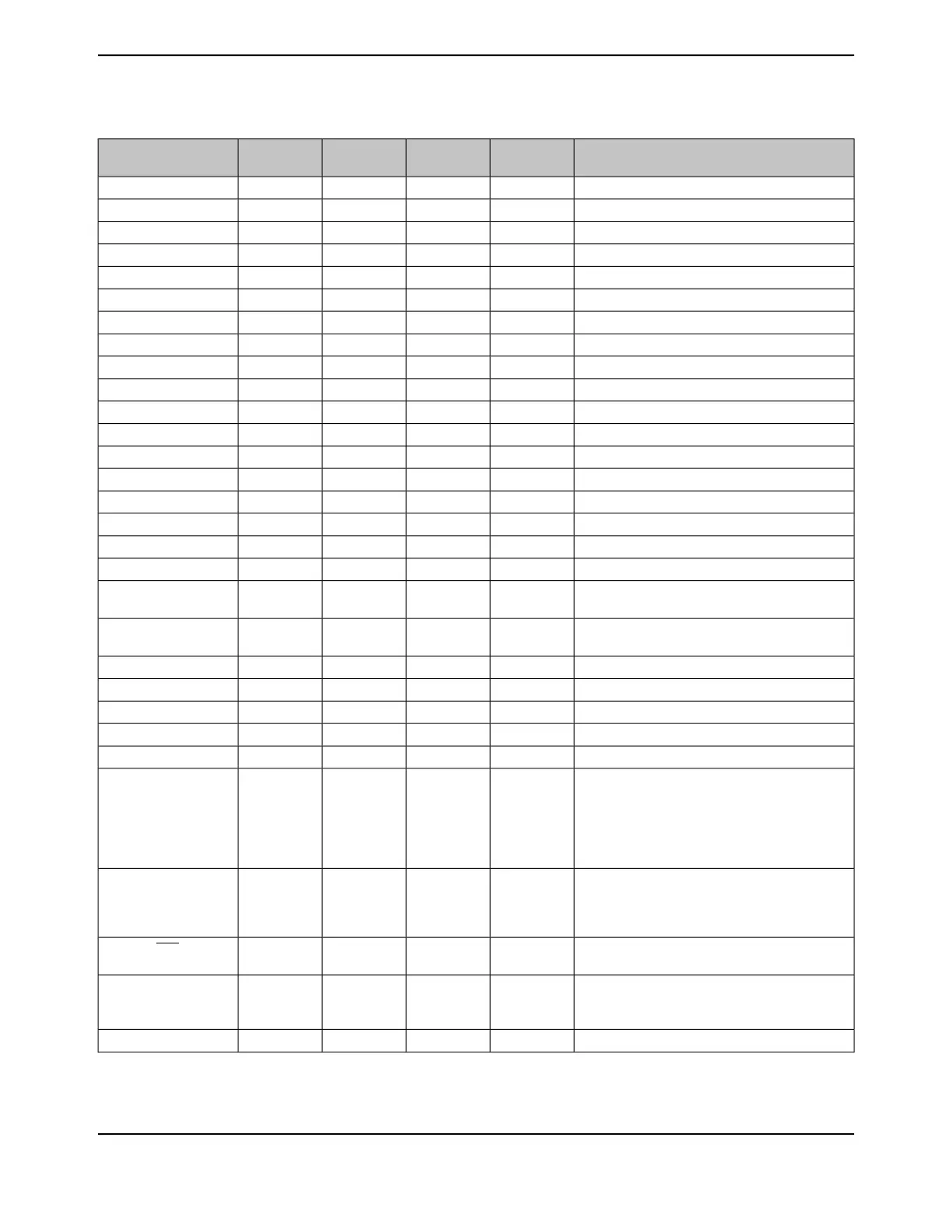

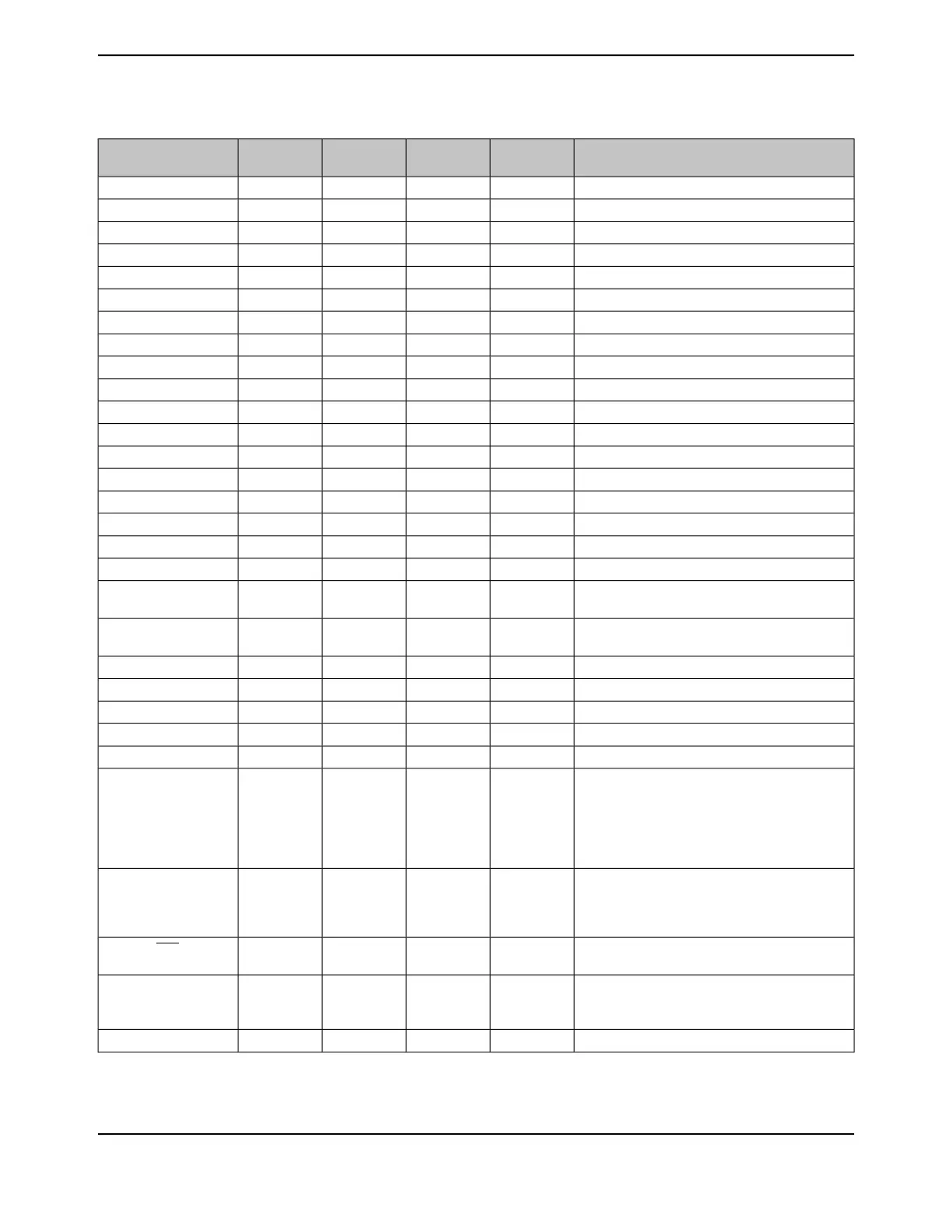

Table 26-3. Signals by Signal Name (continued)

DescriptionBuffer TypePin TypePin Mux / Pin

Assignment

Pin NumberPin Name

EPI module 0 signal 11.TTLI/OPG0 (15)49EPI0S11

EPI module 0 signal 12.TTLI/OPM3 (15)75EPI0S12

EPI module 0 signal 13.TTLI/OPM2 (15)76EPI0S13

EPI module 0 signal 14.TTLI/OPM1 (15)77EPI0S14

EPI module 0 signal 15.TTLI/OPM0 (15)78EPI0S15

EPI module 0 signal 16.TTLI/OPL0 (15)81EPI0S16

EPI module 0 signal 17.TTLI/OPL1 (15)82EPI0S17

EPI module 0 signal 18.TTLI/OPL2 (15)83EPI0S18

EPI module 0 signal 19.TTLI/OPL3 (15)84EPI0S19

EPI module 0 signal 20.TTLI/OPQ0 (15)5EPI0S20

EPI module 0 signal 21.TTLI/OPQ1 (15)6EPI0S21

EPI module 0 signal 22.TTLI/OPQ2 (15)11EPI0S22

EPI module 0 signal 23.TTLI/OPQ3 (15)27EPI0S23

EPI module 0 signal 24.TTLI/OPK7 (15)60EPI0S24

EPI module 0 signal 25.TTLI/OPK6 (15)61EPI0S25

EPI module 0 signal 26.TTLI/OPL4 (15)85EPI0S26

EPI module 0 signal 27.TTLI/OPB2 (15)91EPI0S27

EPI module 0 signal 28.TTLI/OPB3 (15)92EPI0S28

EPI module 0 signal 29.TTLI/OPP2 (15)

PN2 (15)

103

109

EPI0S29

EPI module 0 signal 30.TTLI/OPP3 (15)

PN3 (15)

104

110

EPI0S30

EPI module 0 signal 31.TTLI/OPK5 (15)62EPI0S31

EPI module 0 signal 32.TTLI/OPK4 (15)63EPI0S32

EPI module 0 signal 33.TTLI/OPL5 (15)86EPI0S33

EPI module 0 signal 34.TTLI/OPN4 (15)111EPI0S34

EPI module 0 signal 35.TTLI/OPN5 (15)112EPI0S35

Ground reference for logic and I/O pins.Power-fixed17

48

55

58

80

114

GND

The ground reference for the analog circuits (ADC,

Analog Comparators, etc.). These are separated

from GND to minimize the electrical noise contained

on VDD from affecting the analog functions.

Power-fixed10GNDA

An output that indicates the processor is in

Hibernate mode.

TTLOfixed65HIB

I

2

C module 0 clock. Note that this signal has an

active pull-up. The corresponding port pin should

not be configured as open drain.

ODI/OPB2 (2)91I2C0SCL

I

2

C module 0 data.ODI/OPB3 (2)92I2C0SDA

1787June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...