www.ti.com

IO Wrap Register Map

1159

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

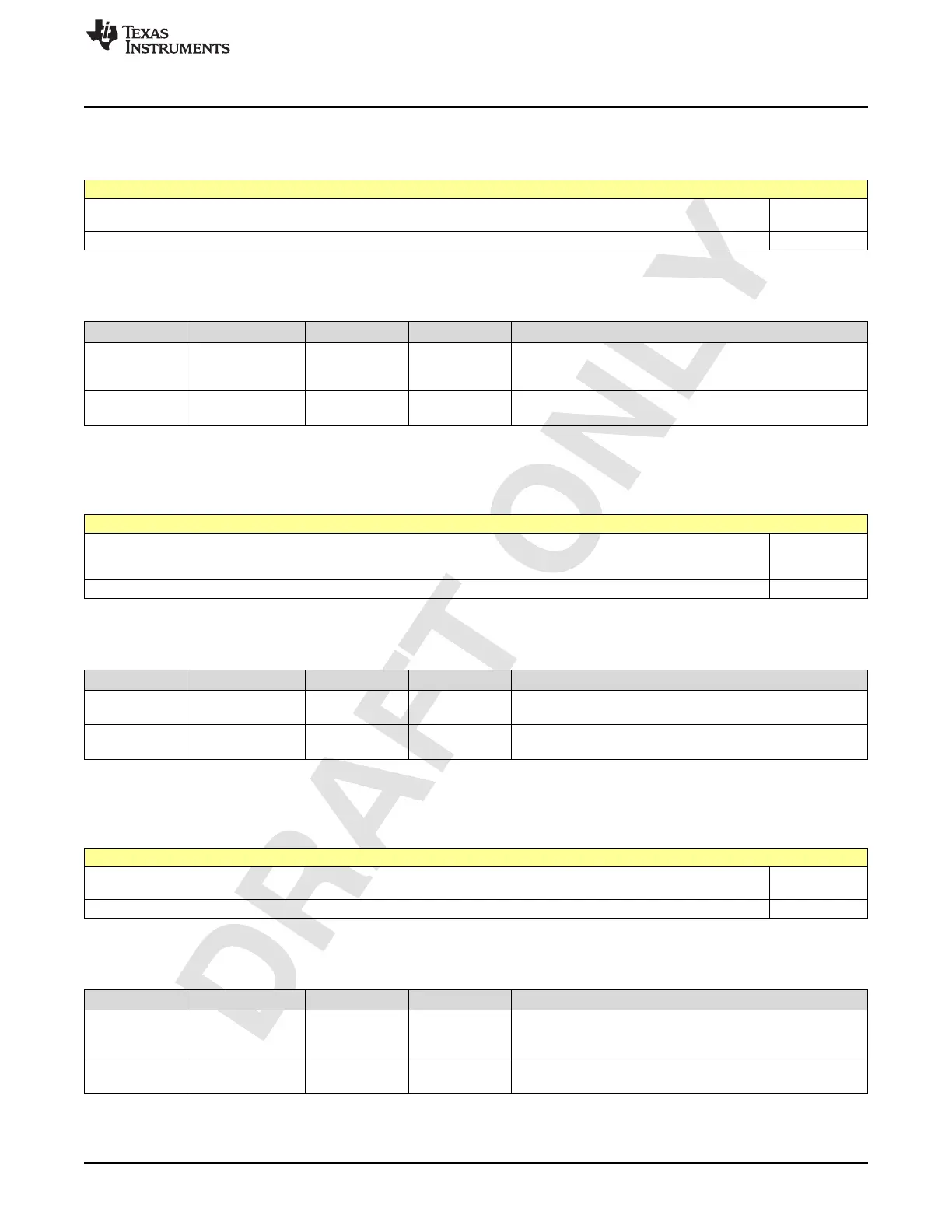

2.16.485 Register 8B8h (offset = 8B8h) [reset = 0h]

Figure 2-2748. Register 8B8h

7 6 5 4 3 2 1 0

SEL_INTPI_TDD_EN_TXA POL_INTPI_TD

D_EN_TXA

R/W-0h R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-2764. Register 8B8 Field Descriptions

Bit Field Type Reset Description

2-1

SEL_INTPI_TDD_

EN_TXA

R/W 0h

select control for intpi_tdd_en_txa. 0 indicates take from

parallel GPIO 1 indicates take from Serial LVDS GPIO 2

indicates take from Serdes GPIO

0-0

POL_INTPI_TDD_

EN_TXA

R/W 0h

polarity control for intpi_tdd_en_txa. 0 indicates pass through

from GPIO when selected 1 indicates inverted signal

2.16.486 Register 8B9h (offset = 8B9h) [reset = 2h]

Figure 2-2749. Register 8B9h

7 6 5 4 3 2 1 0

OVR_SEL_INT

PI_TDD_EN_T

XA

OVR_INTPI_T

DD_EN_TXA

R/W-1h R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-2765. Register 8B9 Field Descriptions

Bit Field Type Reset Description

1-1

OVR_SEL_INTPI_

TDD_EN_TXA

R/W 1h

control to select whether the input function intpi_tdd_en_txa

needs to be overriden ot not. 1 indicates override.

0-0

OVR_INTPI_TDD_

EN_TXA

R/W 0h override value for ovr_sel_intpi_tdd_en_txa is made high

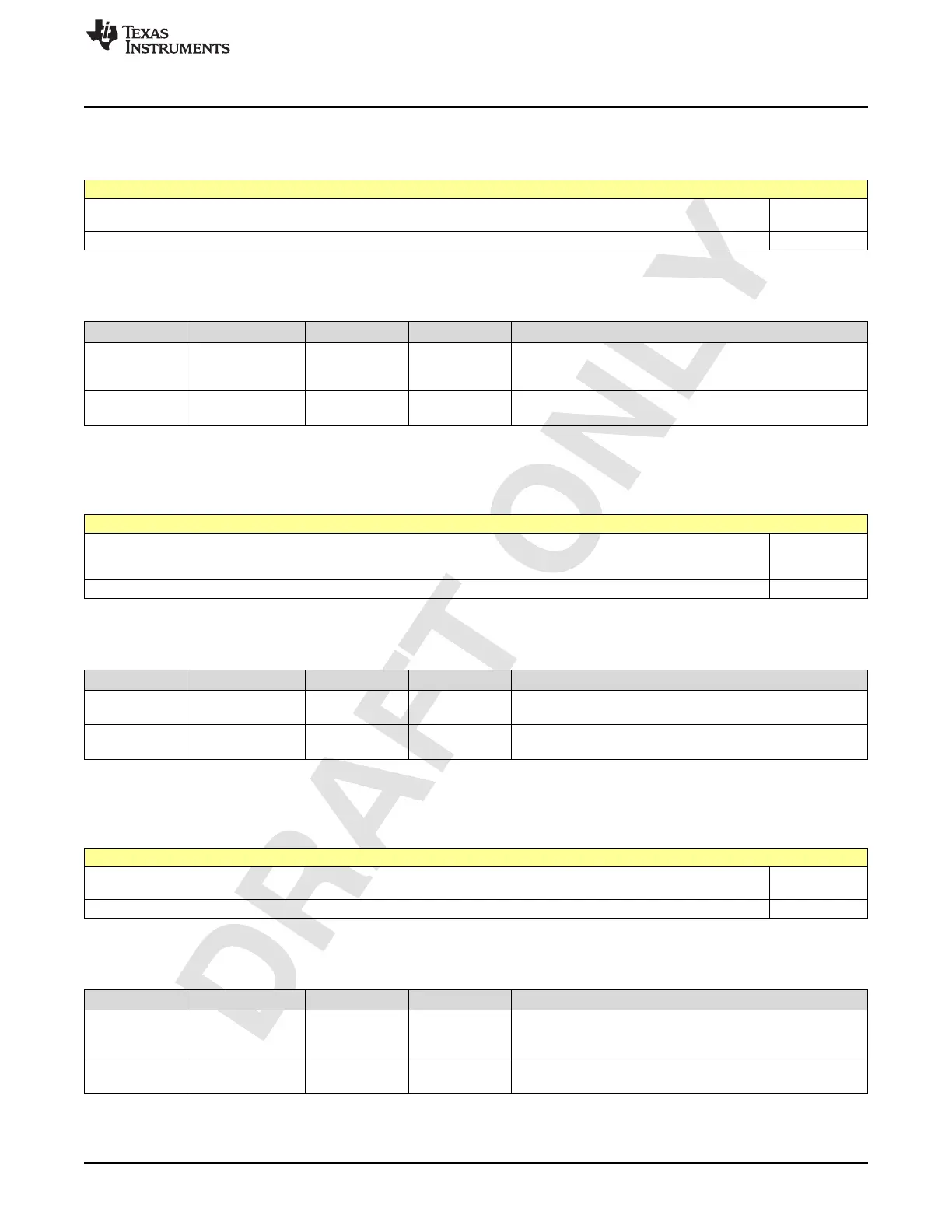

2.16.487 Register 8BCh (offset = 8BCh) [reset = 0h]

Figure 2-2750. Register 8BCh

7 6 5 4 3 2 1 0

SEL_INTPI_TDD_EN_TXB POL_INTPI_TD

D_EN_TXB

R/W-0h R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-2766. Register 8BC Field Descriptions

Bit Field Type Reset Description

2-1

SEL_INTPI_TDD_

EN_TXB

R/W 0h

select control for intpi_tdd_en_txb. 0 indicates take from

parallel GPIO 1 indicates take from Serial LVDS GPIO 2

indicates take from Serdes GPIO

0-0

POL_INTPI_TDD_

EN_TXB

R/W 0h

polarity control for intpi_tdd_en_txb. 0 indicates pass through

from GPIO when selected 1 indicates inverted signal

Loading...

Loading...