www.ti.com

ANA_4T4R Register Map

535

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

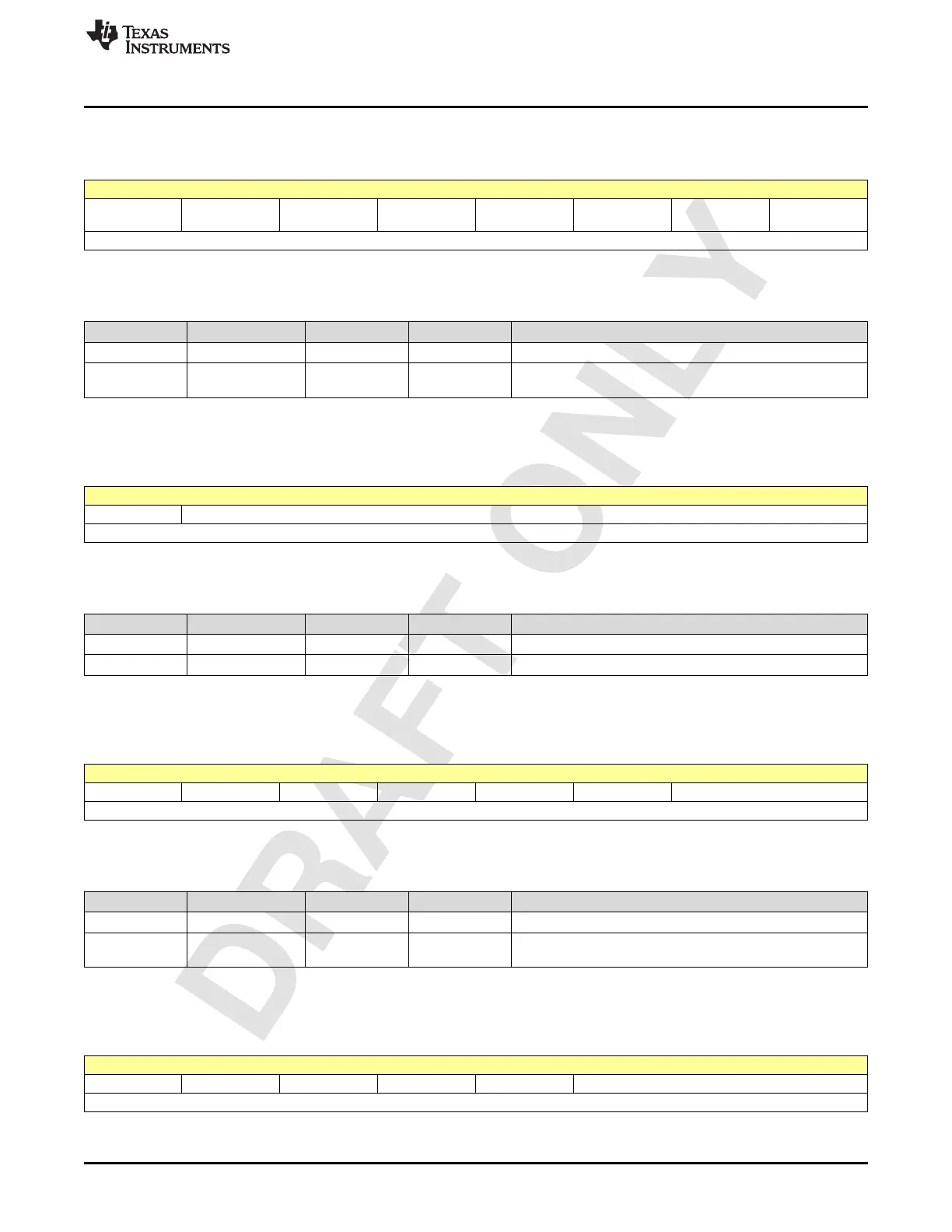

2.7.3 Register 10Eh (offset = 10Eh) [reset = 0h]

Figure 2-924. Register 10Eh

7 6 5 4 3 2 1 0

0 0 0 0 0 0 0 CTL_FBDIV_DI

VBY2

R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-931. Register 10E Field Descriptions

Bit Field Type Reset Description

7-1 0 R/W 0h Must read or write 0

0-0

CTL_FBDIV_DIVB

Y2

R/W 0h extra by2 in feedback divider in the pll

2.7.4 Register 10Fh (offset = 10Fh) [reset = 12h]

Figure 2-925. Register 10Fh

7 6 5 4 3 2 1 0

0 CTL_FBDIV_DIV

R/W-0h R/W-12h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-932. Register 10F Field Descriptions

Bit Field Type Reset Description

7-7 0 R/W 0h Must read or write 0

6-0 CTL_FBDIV_DIV R/W 12h Feedback divider. 18 is default assuming 9Ghz dac.

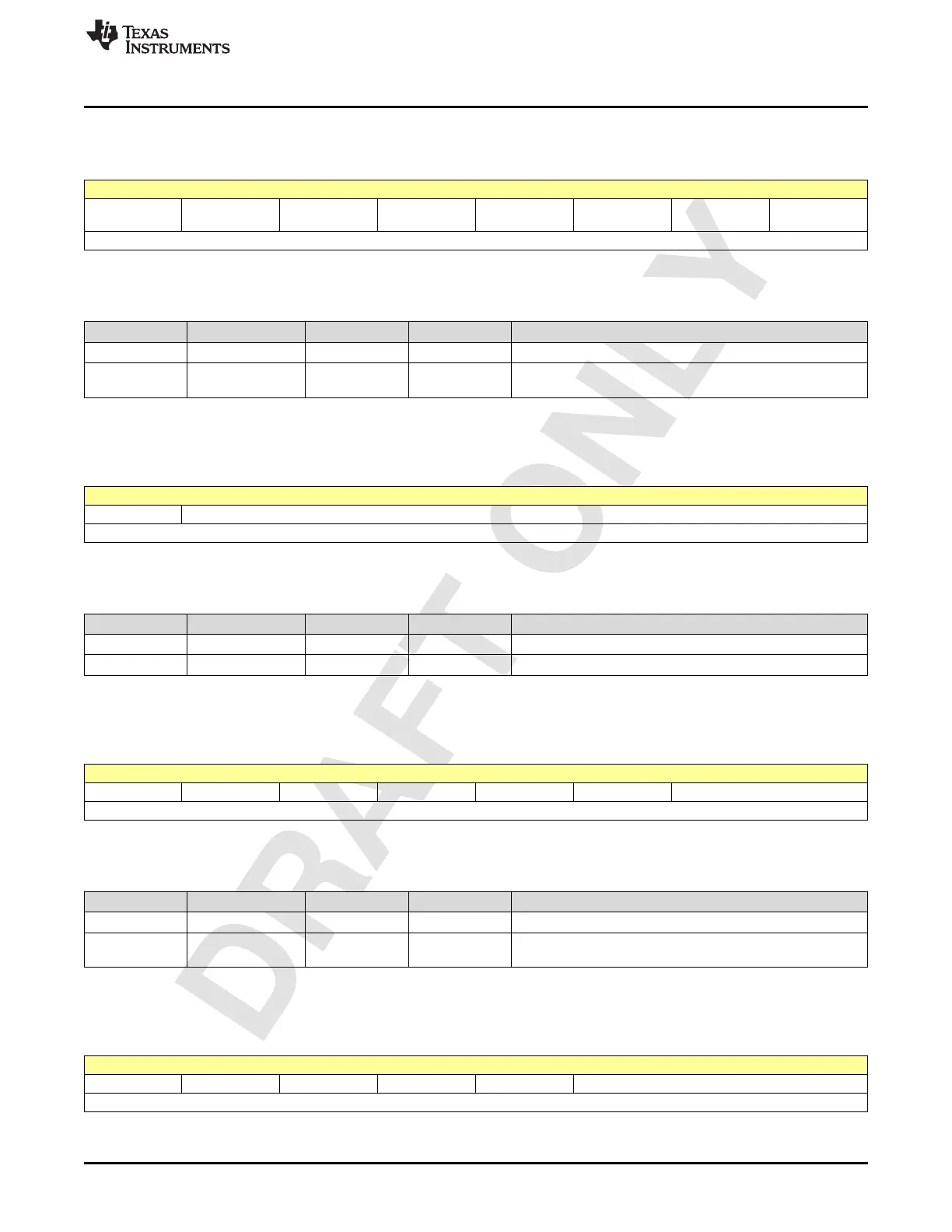

2.7.5 Register 110h (offset = 110h) [reset = 0h]

Figure 2-926. Register 110h

7 6 5 4 3 2 1 0

0 0 0 0 0 0 CTL_OUTDIV_MUX_TX

R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-933. Register 110 Field Descriptions

Bit Field Type Reset Description

7-2 0 R/W 0h Must read or write 0

1-0

CTL_OUTDIV_MU

X_TX

R/W 0h

Mux choosing between ext ref-clk and pll_clk for dac. That is

MSB bit. LSB bit choses between by1 and byn.

2.7.6 Register 111h (offset = 111h) [reset = 0h]

Figure 2-927. Register 111h

7 6 5 4 3 2 1 0

0 0 0 0 0 CTL_OUTDIV_DIV_TX

R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Loading...

Loading...