www.ti.com

JESD_SUBCHIP Register Map

251

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

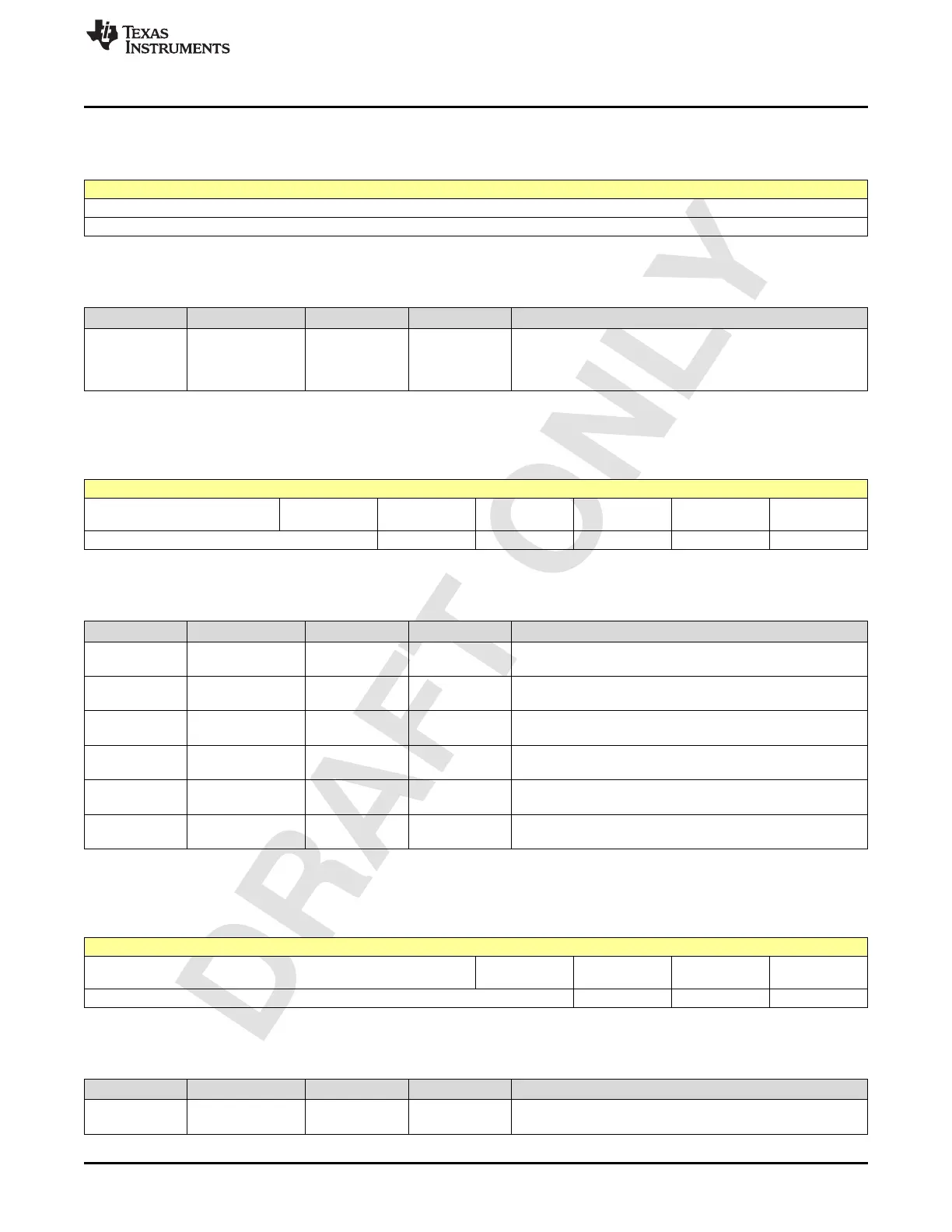

2.3.174 Register 193h (offset = 193h) [reset = 0h]

Figure 2-215. Register 193h

7 6 5 4 3 2 1 0

DBG_TX_READ_OUT_REG2[15:8]

R-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-218. Register 193 Field Descriptions

Bit Field Type Reset Description

7-0

DBG_TX_READ_O

UT_REG2[15:8]

R 0h

Data from first 4T mux output, is sent to this status register, to

check for data toggling.

dbg_tx_read_out_reg1 and dbg_tx_read_out_reg2 has two

consecutive samples

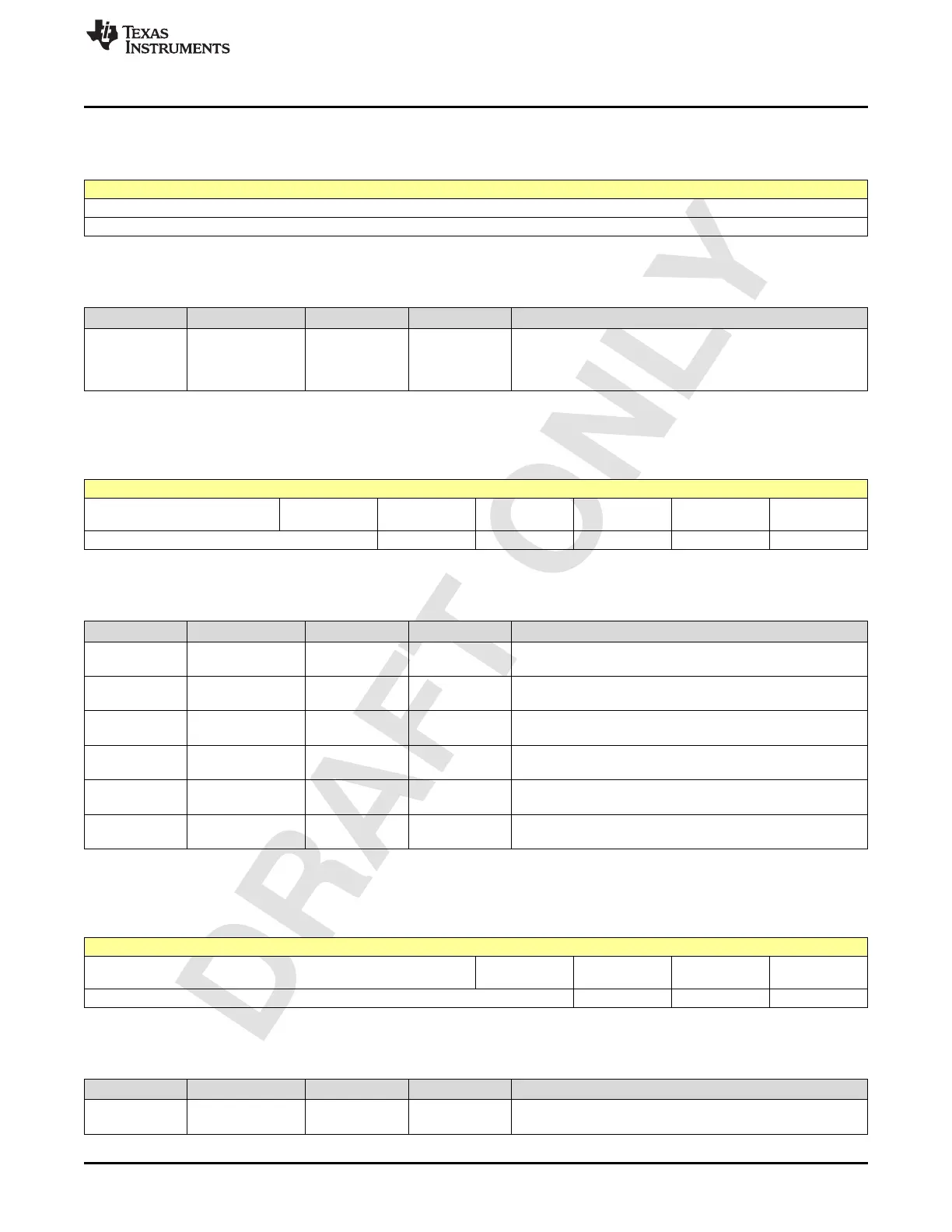

2.3.175 Register 194h (offset = 194h) [reset = 0h]

Figure 2-216. Register 194h

7 6 5 4 3 2 1 0

DBG_FB_ON_

C

DBG_FB_ON_

A

DBG_RX_ON_

D

DBG_RX_ON_

C

DBG_RX_ON_

B

DBG_RX_ON_

A

R-0h R-0h R-0h R-0h R-0h R-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-219. Register 194 Field Descriptions

Bit Field Type Reset Description

5-5 DBG_FB_ON_C R 0h

Sig-valid from TDD controller is assigned to this status

register, post synchronizer

4-4 DBG_FB_ON_A R 0h

Sig-valid from TDD controller is assigned to this status

register, post synchronizer

3-3 DBG_RX_ON_D R 0h

Sig-valid from TDD controller is assigned to this status

register, post synchronizer

2-2 DBG_RX_ON_C R 0h

Sig-valid from TDD controller is assigned to this status

register, post synchronizer

1-1 DBG_RX_ON_B R 0h

Sig-valid from TDD controller is assigned to this status

register, post synchronizer

0-0 DBG_RX_ON_A R 0h

Sig-valid from TDD controller is assigned to this status

register, post synchronizer

2.3.176 Register 195h (offset = 195h) [reset = 0h]

Figure 2-217. Register 195h

7 6 5 4 3 2 1 0

DBG_TX_ON_

D

DBG_TX_ON_

C

DBG_TX_ON_

B

DBG_TX_ON_

A

R-0h R-0h R-0h R-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-220. Register 195 Field Descriptions

Bit Field Type Reset Description

3-3 DBG_TX_ON_D R 0h

Sig-valid from TDD controller is assigned to this status

register, post synchronizer

Loading...

Loading...