DAC JESD Register Map

www.ti.com

366

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

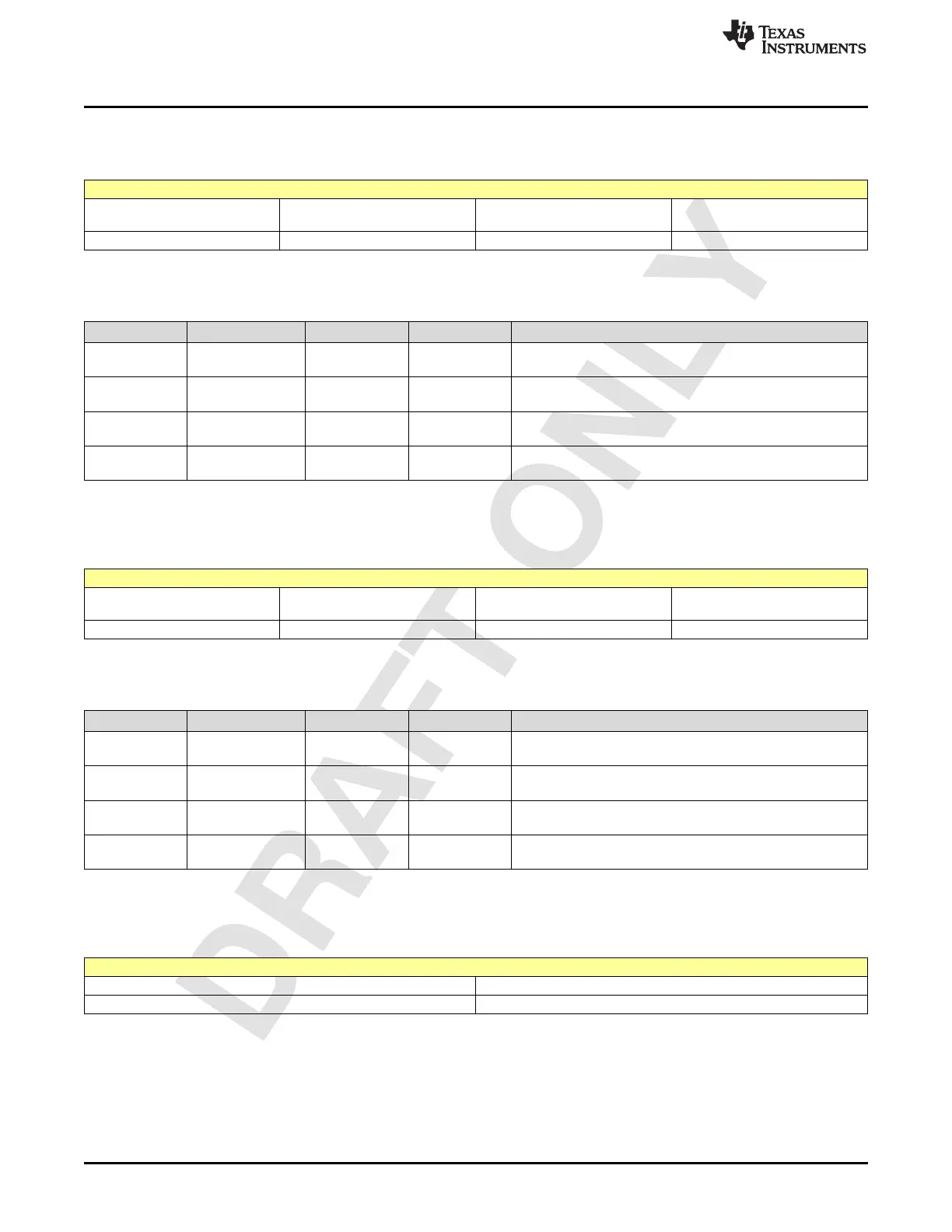

2.4.258 Register 146h (offset = 146h) [reset = 0h]

Figure 2-487. Register 146h

7 6 5 4 3 2 1 0

CTRL_TX1_JESD_CLK_DIV2_P

3

CTRL_TX1_JESD_CLK_DIV2_P

2

CTRL_TX1_JESD_CLK_DIV2_P

1

CTRL_TX1_JESD_CLK_DIV2_P

0

R/W-0h R/W-0h R/W-0h R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-491. Register 146 Field Descriptions

Bit Field Type Reset Description

7-6

CTRL_TX1_JESD_

CLK_DIV2_P3

R/W 0h

bit[1] - select bit[0] as clk-en

bit[0] - 0:DIS, 1-EN

5-4

CTRL_TX1_JESD_

CLK_DIV2_P2

R/W 0h

bit[1] - select bit[0] as clk-en

bit[0] - 0:DIS, 1-EN

3-2

CTRL_TX1_JESD_

CLK_DIV2_P1

R/W 0h

bit[1] - select bit[0] as clk-en

bit[0] - 0:DIS, 1-EN

1-0

CTRL_TX1_JESD_

CLK_DIV2_P0

R/W 0h

bit[1] - select bit[0] as clk-en

bit[0] - 0:DIS, 1-EN

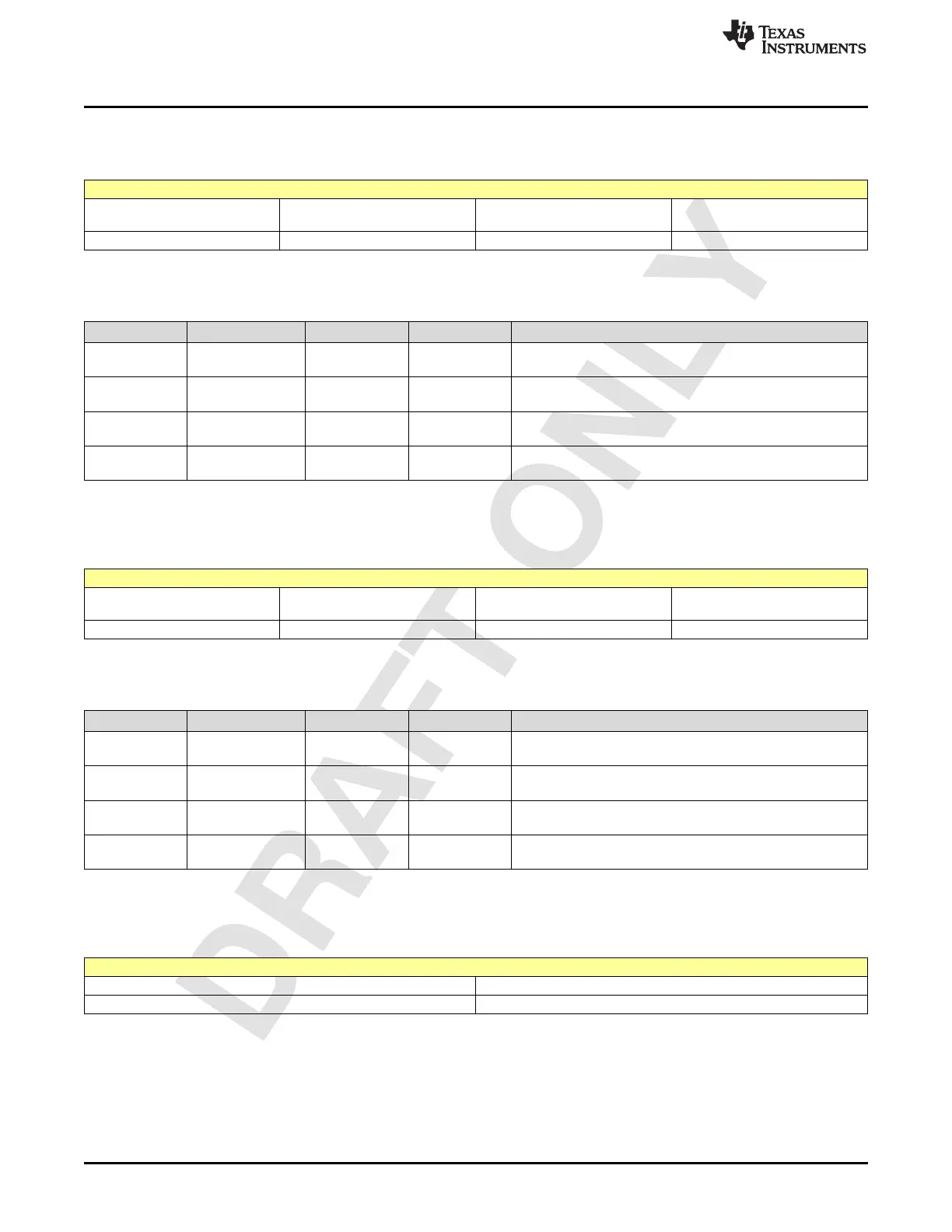

2.4.259 Register 147h (offset = 147h) [reset = 0h]

Figure 2-488. Register 147h

7 6 5 4 3 2 1 0

CTRL_TX2_JESD_CLK_DIV2_P

3

CTRL_TX2_JESD_CLK_DIV2_P

2

CTRL_TX2_JESD_CLK_DIV2_P

1

CTRL_TX2_JESD_CLK_DIV2_P

0

R/W-0h R/W-0h R/W-0h R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-492. Register 147 Field Descriptions

Bit Field Type Reset Description

7-6

CTRL_TX2_JESD_

CLK_DIV2_P3

R/W 0h

bit[1] - select bit[0] as clk-en

bit[0] - 0:DIS, 1-EN

5-4

CTRL_TX2_JESD_

CLK_DIV2_P2

R/W 0h

bit[1] - select bit[0] as clk-en

bit[0] - 0:DIS, 1-EN

3-2

CTRL_TX2_JESD_

CLK_DIV2_P1

R/W 0h

bit[1] - select bit[0] as clk-en

bit[0] - 0:DIS, 1-EN

1-0

CTRL_TX2_JESD_

CLK_DIV2_P0

R/W 0h

bit[1] - select bit[0] as clk-en

bit[0] - 0:DIS, 1-EN

2.4.260 Register 148h (offset = 148h) [reset = 88h]

Figure 2-489. Register 148h

7 6 5 4 3 2 1 0

MAPPER_SYNC_FIFO_TX1_OFFSET_S4TO2 MAPPER_SYNC_FIFO_TX1_OFFSET_S4TO4

R/W-8h R/W-8h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Loading...

Loading...