JESD_SUBCHIP Register Map

www.ti.com

166

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

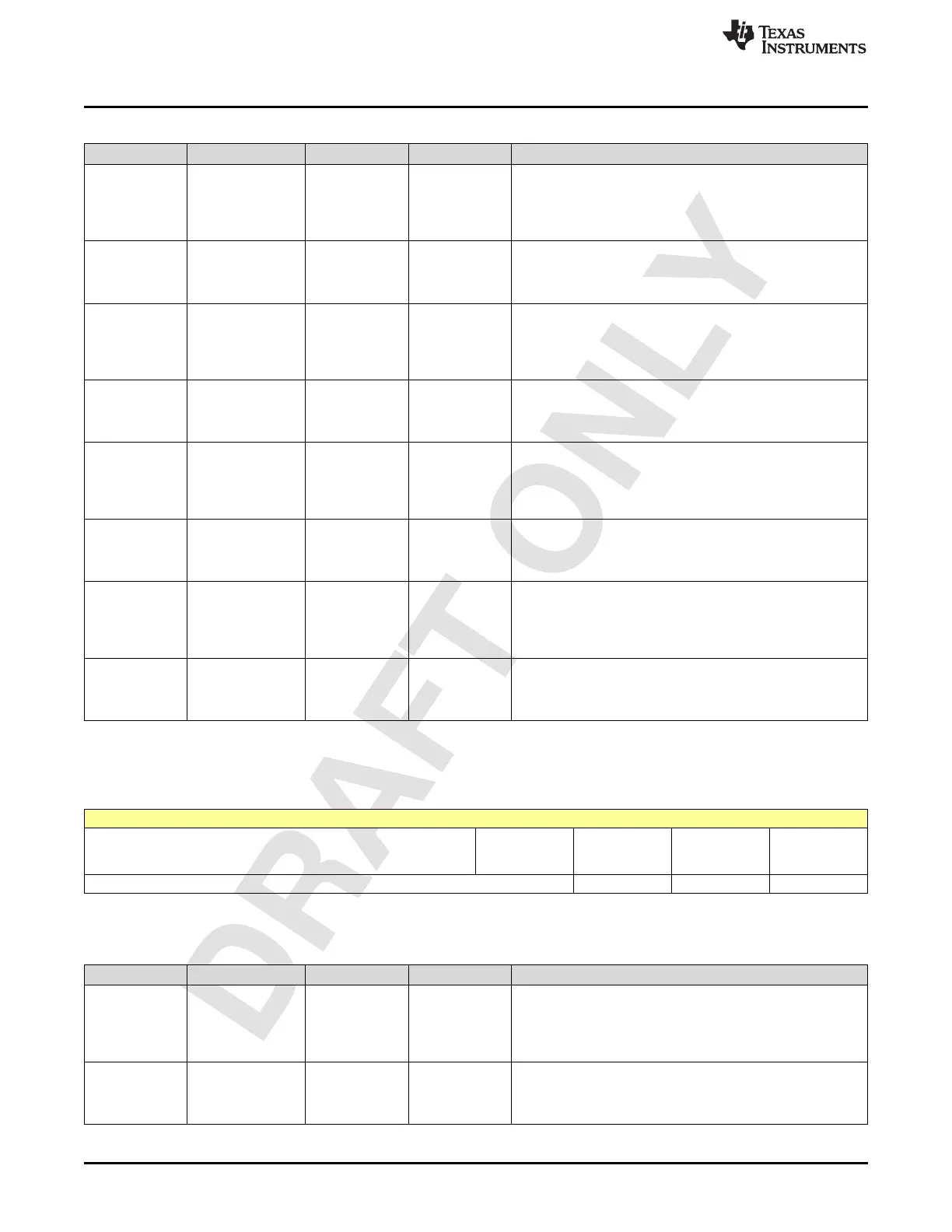

Table 2-54. Register 2C Field Descriptions

Bit Field Type Reset Description

7-7

RXD_SIG_INVALI

D_RD_OVR

R/W 0h

FOR LOW POWER CONSUMPTION:

ASYNC FIFOs are gated based on sig-invalid from TDD

controller. Setting this register to 1 overrides this behaviour

and the gating of data depends on the value of

RXD_SIG_INVALID_RD_VAL.

6-6

RXD_SIG_INVALI

D_RD_VAL

R/W 0h

FOR LOW POWER CONSUMPTION:

When RXD_SIG_INVALID_RD_OVR is 1,

setting this register to val = 0, gates the data

setting to val = 1, ungates the data

5-5

RXC_SIG_INVALI

D_RD_OVR

R/W 0h

FOR LOW POWER CONSUMPTION:

ASYNC FIFOs are gated based on sig-invalid from TDD

controller. Setting this register to 1 overrides this behaviour

and the gating of data depends on the value of

RXC_SIG_INVALID_RD_VAL.

4-4

RXC_SIG_INVALI

D_RD_VAL

R/W 0h

FOR LOW POWER CONSUMPTION:

When RXC_SIG_INVALID_RD_OVR is 1,

setting this register val = 0, gates the data

setting to val = 1, ungates the data

3-3

RXB_SIG_INVALID

_RD_OVR

R/W 0h

FOR LOW POWER CONSUMPTION:

ASYNC FIFOs are gated based on sig-invalid from TDD

controller. Setting this register to 1 overrides this behaviour

and the gating of data depends on the value of

RXB_SIG_INVALID_RD_VAL.

2-2

RXB_SIG_INVALID

_RD_VAL

R/W 0h

FOR LOW POWER CONSUMPTION:

When RXB_SIG_INVALID_RD_OVR is 1,

setting this register val = 0, gates the data

setting to val = 1, ungates the data

1-1

RXA_SIG_INVALID

_RD_OVR

R/W 0h

FOR LOW POWER CONSUMPTION:

ASYNC FIFOs are gated based on sig-invalid from TDD

controller. Setting this register to 1 overrides this behaviour

and the gating of data depends on the value of

RXC_SIG_INVALID_RD_VAL.

0-0

RXA_SIG_INVALID

_RD_VAL

R/W 0h

FOR LOW POWER CONSUMPTION:

When RXA_SIG_INVALID_RD_OVR is 1,

setting this register val = 0, gates the data

setting to val = 1, ungates the data

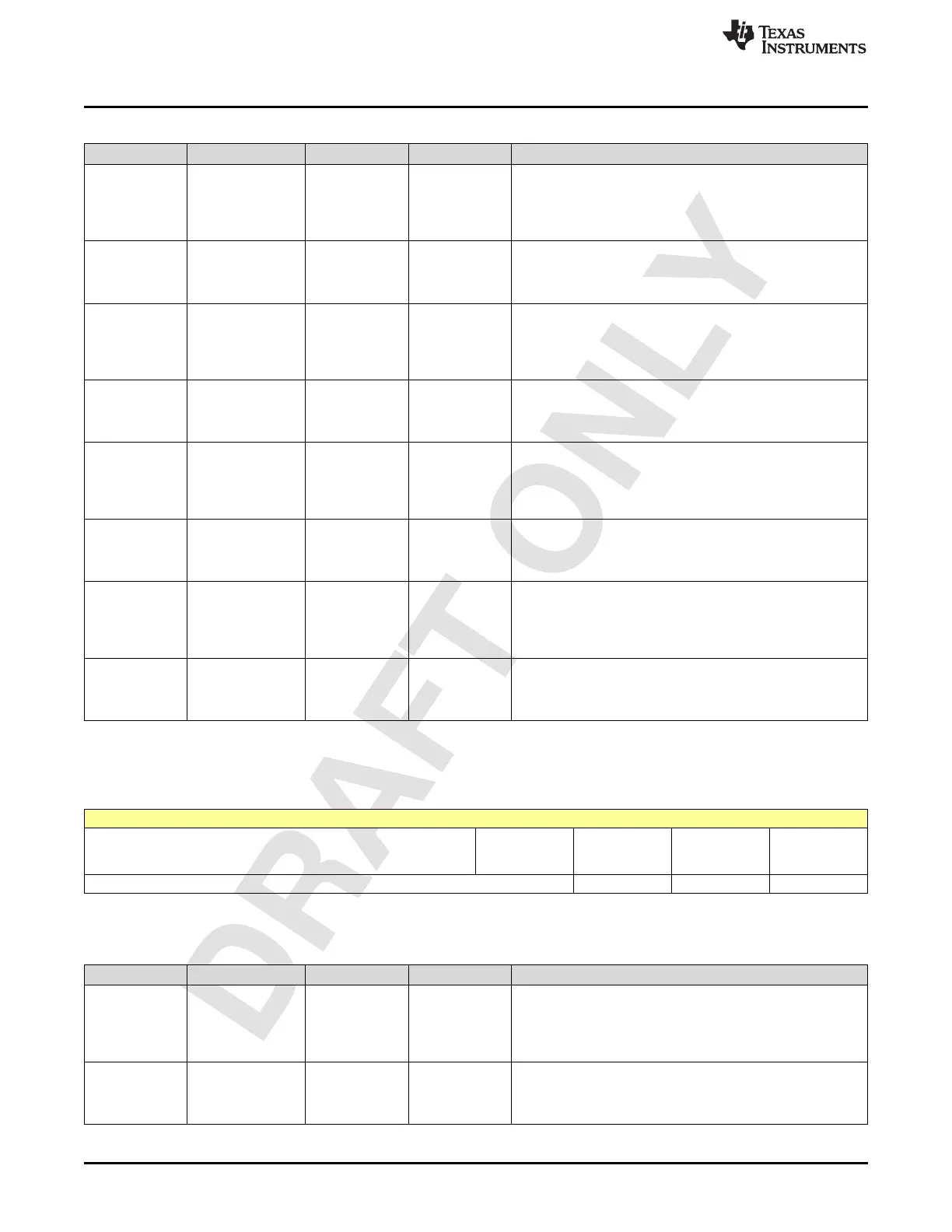

2.3.11 Register 2Dh (offset = 2Dh) [reset = 0h]

Figure 2-52. Register 2Dh

7 6 5 4 3 2 1 0

FBCD_SIG_IN

VALID_RD_OV

R

FBCD_SIG_IN

VALID_RD_VA

L

FBAB_SIG_INV

ALID_RD_OVR

FBAB_SIG_INV

ALID_RD_VAL

R/W-0h R/W-0h R/W-0h R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-55. Register 2D Field Descriptions

Bit Field Type Reset Description

3-3

FBCD_SIG_INVALI

D_RD_OVR

R/W 0h

FOR LOW POWER CONSUMPTION:

ASYNC FIFOs are gated based on sig-invalid from TDD

controller. Setting this register to 1 overrides this behaviour

and the gating of data depends on the value of

FBCD_SIG_INVALID_RD_VAL.

2-2

FBCD_SIG_INVALI

D_RD_VAL

R/W 0h

FOR LOW POWER CONSUMPTION:

When FBCD_SIG_INVALID_RD_OVR is 1,

setting this register val = 0, gates the data

setting to val = 1, ungates the data

Loading...

Loading...