IO Wrap Register Map

www.ti.com

1200

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

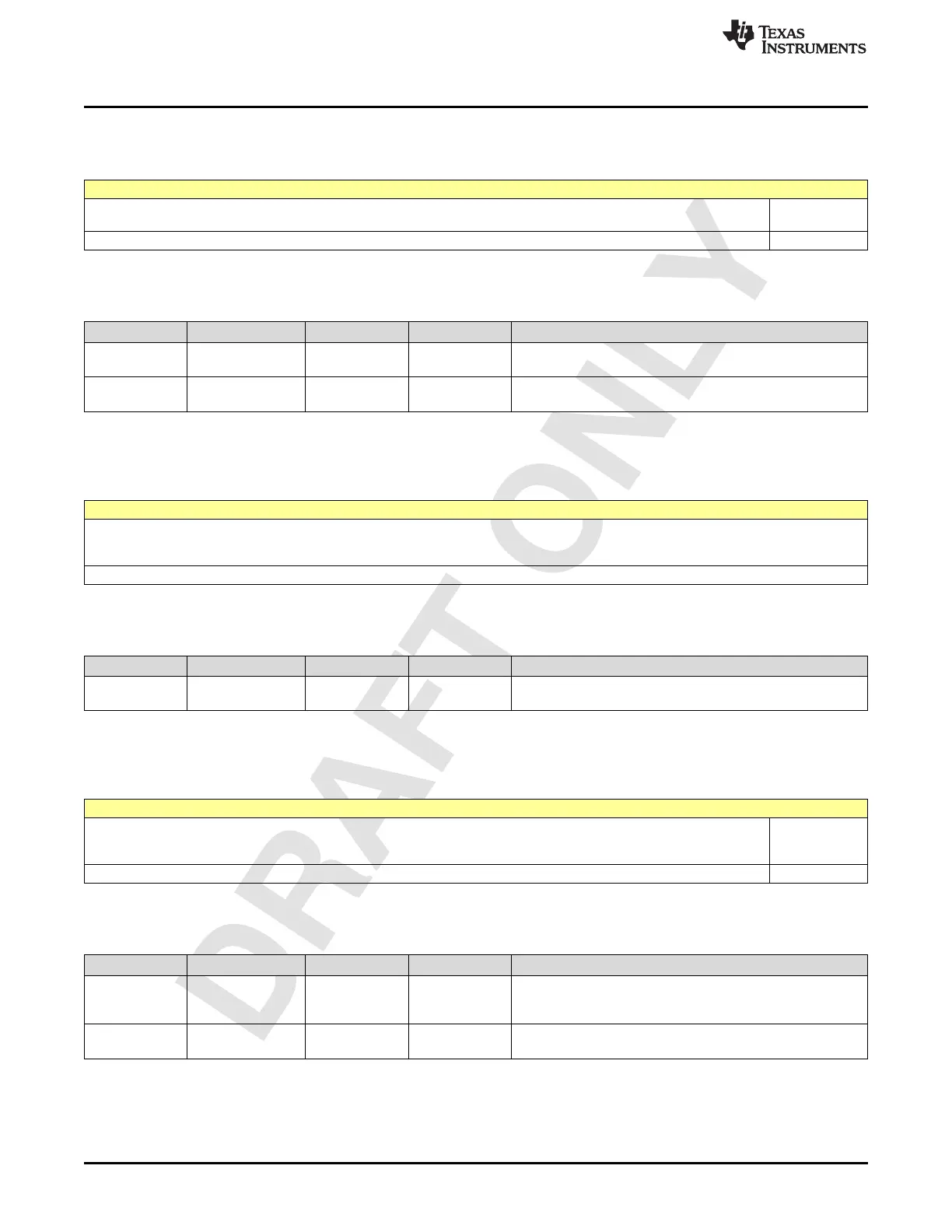

2.16.607 Register 10C1h (offset = 10C1h) [reset = 2h]

Figure 2-2870. Register 10C1h

7 6 5 4 3 2 1 0

OVR_SEL_INT

PO_ALARM_2

OVR_INTPO_A

LARM_2

R/W-1h R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-2886. Register 10C1 Field Descriptions

Bit Field Type Reset Description

1-1

OVR_SEL_INTPO_

ALARM_2

R/W 1h

control to select whether the input function intpo_alarm_2

needs to be overriden ot not. 1 indicates override.

0-0

OVR_INTPO_ALA

RM_2

R/W 0h

override value for intpo_alarm_2 when ovr_sel_intpo_alarm_2

is made high

2.16.608 Register 10C4h (offset = 10C4h) [reset = 0h]

Figure 2-2871. Register 10C4h

7 6 5 4 3 2 1 0

POL_INTPO_D

AC_SYNC_N_

AB_0

R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-2887. Register 10C4 Field Descriptions

Bit Field Type Reset Description

0-0

POL_INTPO_DAC

_SYNC_N_AB_0

R/W 0h

polarity control for intpo_dac_sync_n_ab_0. 0 indicates pass

through from GPIO when selected 1 indicates inverted signal

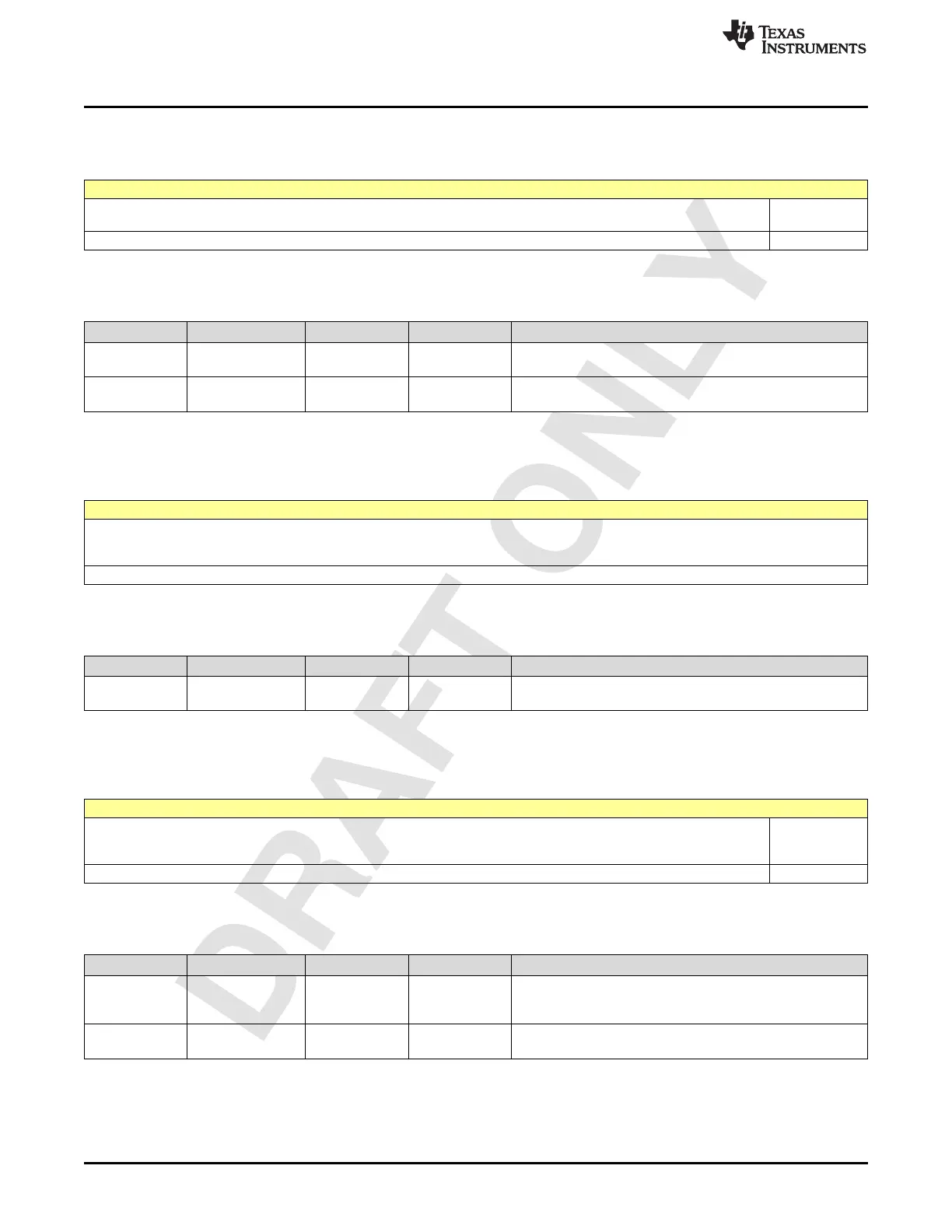

2.16.609 Register 10C5h (offset = 10C5h) [reset = 2h]

Figure 2-2872. Register 10C5h

7 6 5 4 3 2 1 0

OVR_SEL_INT

PO_DAC_SYN

C_N_AB_0

OVR_INTPO_D

AC_SYNC_N_

AB_0

R/W-1h R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-2888. Register 10C5 Field Descriptions

Bit Field Type Reset Description

1-1

OVR_SEL_INTPO_

DAC_SYNC_N_AB

_0

R/W 1h

control to select whether the input function

intpo_dac_sync_n_ab_0 needs to be overriden ot not. 1

indicates override.

0-0

OVR_INTPO_DAC

_SYNC_N_AB_0

R/W 0h

override value for intpo_dac_sync_n_ab_0 when

ovr_sel_intpo_dac_sync_n_ab_0 is made high

Loading...

Loading...