www.ti.com

DAC JESD Register Map

275

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

Table 2-262. Register 3C Field Descriptions

Bit Field Type Reset Description

7-4

SERDES_FIFO_O

FFSET_LANE1

R/W 8h

Used to set the difference between read and write pointers in

the SERDES-JESD FIFO for lane1/lane5

3-0

SERDES_FIFO_O

FFSET_LANE0

R/W 8h

Used to set the difference between read and write pointers in

the SERDES-JESD FIFO for lane0/lane4

2.4.30 Register 3Dh (offset = 3Dh) [reset = 88h]

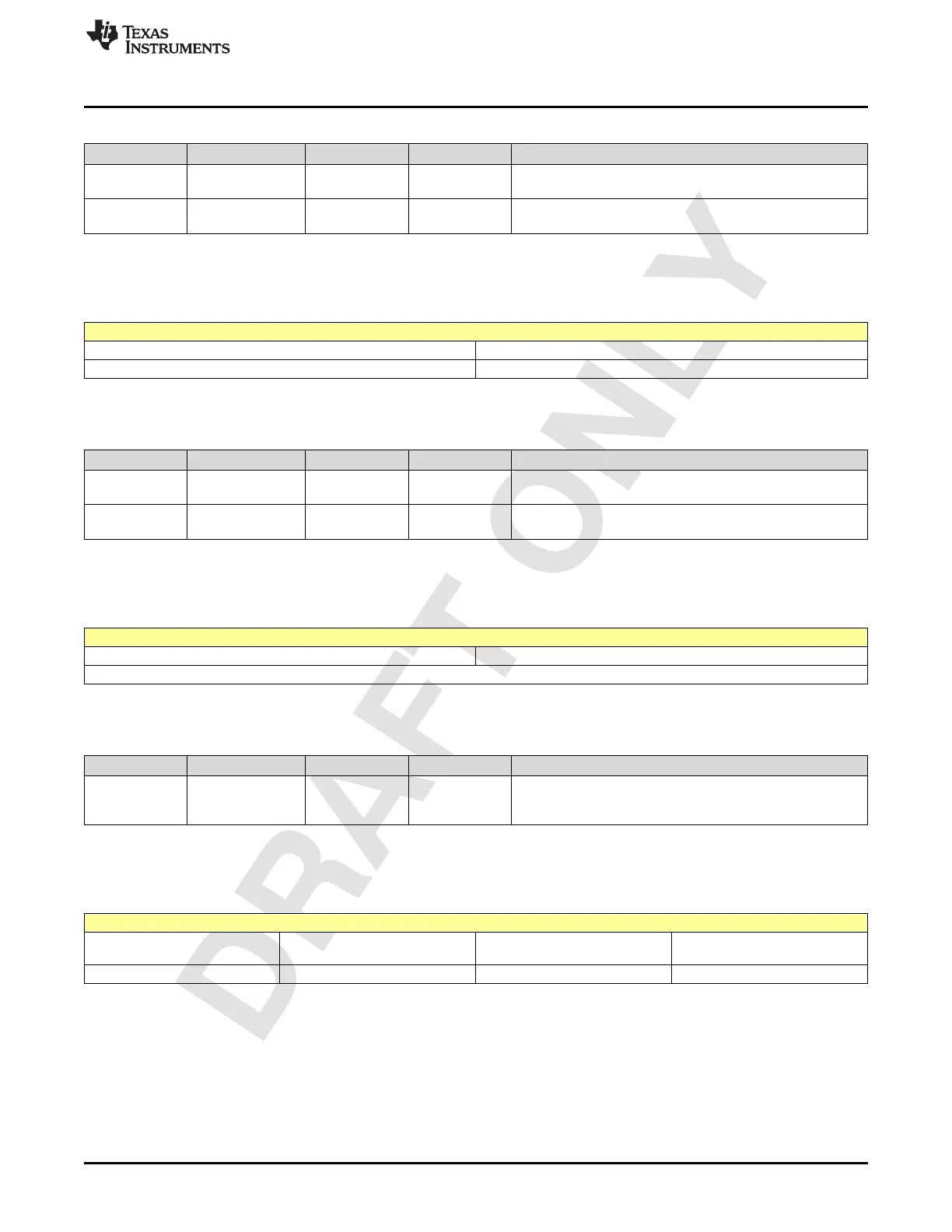

Figure 2-259. Register 3Dh

7 6 5 4 3 2 1 0

SERDES_FIFO_OFFSET_LANE3 SERDES_FIFO_OFFSET_LANE2

R/W-8h R/W-8h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-263. Register 3D Field Descriptions

Bit Field Type Reset Description

7-4

SERDES_FIFO_O

FFSET_LANE3

R/W 8h

Used to set the difference between read and write pointers in

the SERDES-JESD FIFO for lane3/lane7

3-0

SERDES_FIFO_O

FFSET_LANE2

R/W 8h

Used to set the difference between read and write pointers in

the SERDES-JESD FIFO for lane2/lane6

2.4.31 Register 3Eh (offset = 3Eh) [reset = 0h]

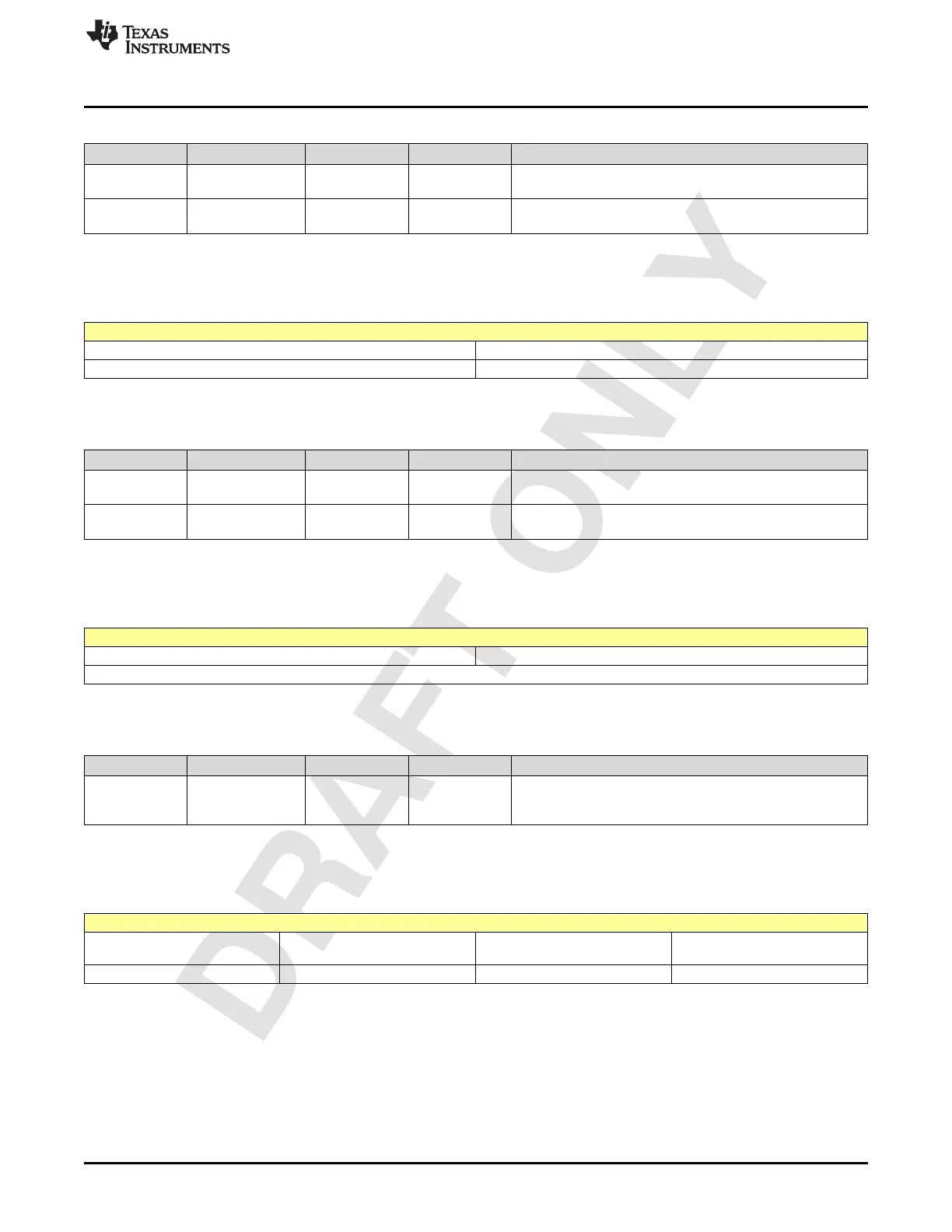

Figure 2-260. Register 3Eh

7 6 5 4 3 2 1 0

SERDES_FIFO_ERROR_DIFF2_UNMASK

R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-264. Register 3E Field Descriptions

Bit Field Type Reset Description

3-0

SERDES_FIFO_E

RROR_DIFF2_UN

MASK

R/W 0h

By default if ptr spacing is 2, fifo errors are not raised. If

needed make this mask to 15.

3:0 bits - lane 3 to lane 0

2.4.32 Register 3Fh (offset = 3Fh) [reset = Ah]

Figure 2-261. Register 3Fh

7 6 5 4 3 2 1 0

SYNC_FIFO_66TO33_OFFSET_

LANE23

SYNC_FIFO_66TO33_OFFSET_

LANE01

SYNC_FIFO_33TO66_OFFSET_

LANE23

SYNC_FIFO_33TO66_OFFSET_

LANE01

R/W-0h R/W-0h R/W-2h R/W-2h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Loading...

Loading...