SERDES Register Map

www.ti.com

512

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

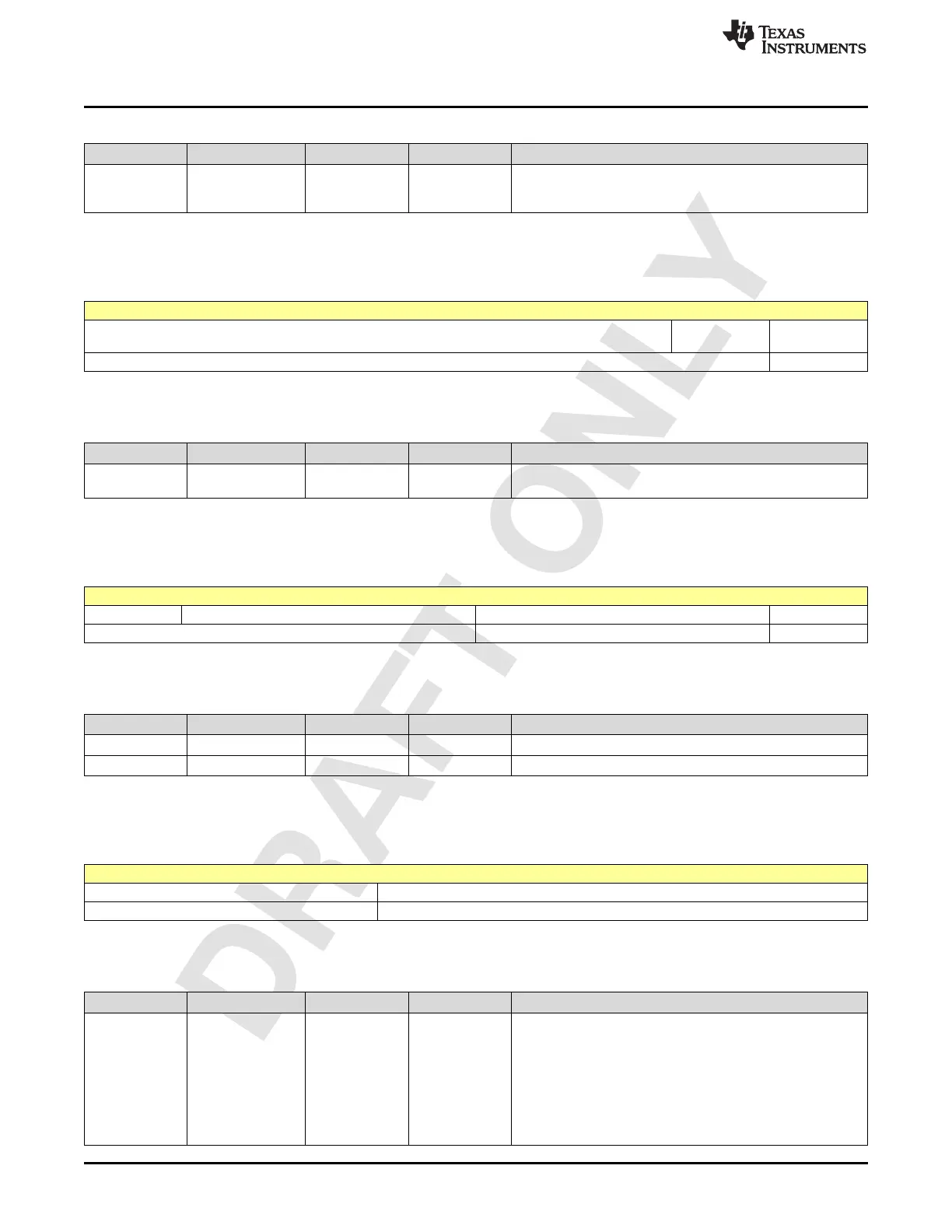

Table 2-864. Register 49F6 Field Descriptions

Bit Field Type Reset Description

1-1

REFCLK_SRC_SE

L

R/W 0h

Reference clock path control:

0h: Reference clock from ckip pin

1h: Reference clock from internal clock

2.6.145 Register 49F8h (offset = 49F8h) [reset = 2h]

Figure 2-859. Register 49F8h

7 6 5 4 3 2 1 0

RX_PLL_VCO_

RANGE_MSB

R/W-1h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-865. Register 49F8 Field Descriptions

Bit Field Type Reset Description

1-1

RX_PLL_VCO_RA

NGE_MSB

R/W 1h

For PLL VCO range settings, see Register PzFDh: RX PLL

VCO RANGE LSB.

2.6.146 Register 49FAh (offset = 49FAh) [reset = 48h]

Figure 2-860. Register 49FAh

7 6 5 4 3 2 1 0

VRVDD_RX VRVDD2_RX

R/W-4h R/W-4h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-866. Register 49FA Field Descriptions

Bit Field Type Reset Description

6-4 VRVDD_RX R/W 4h

3-1 VRVDD2_RX R/W 4h

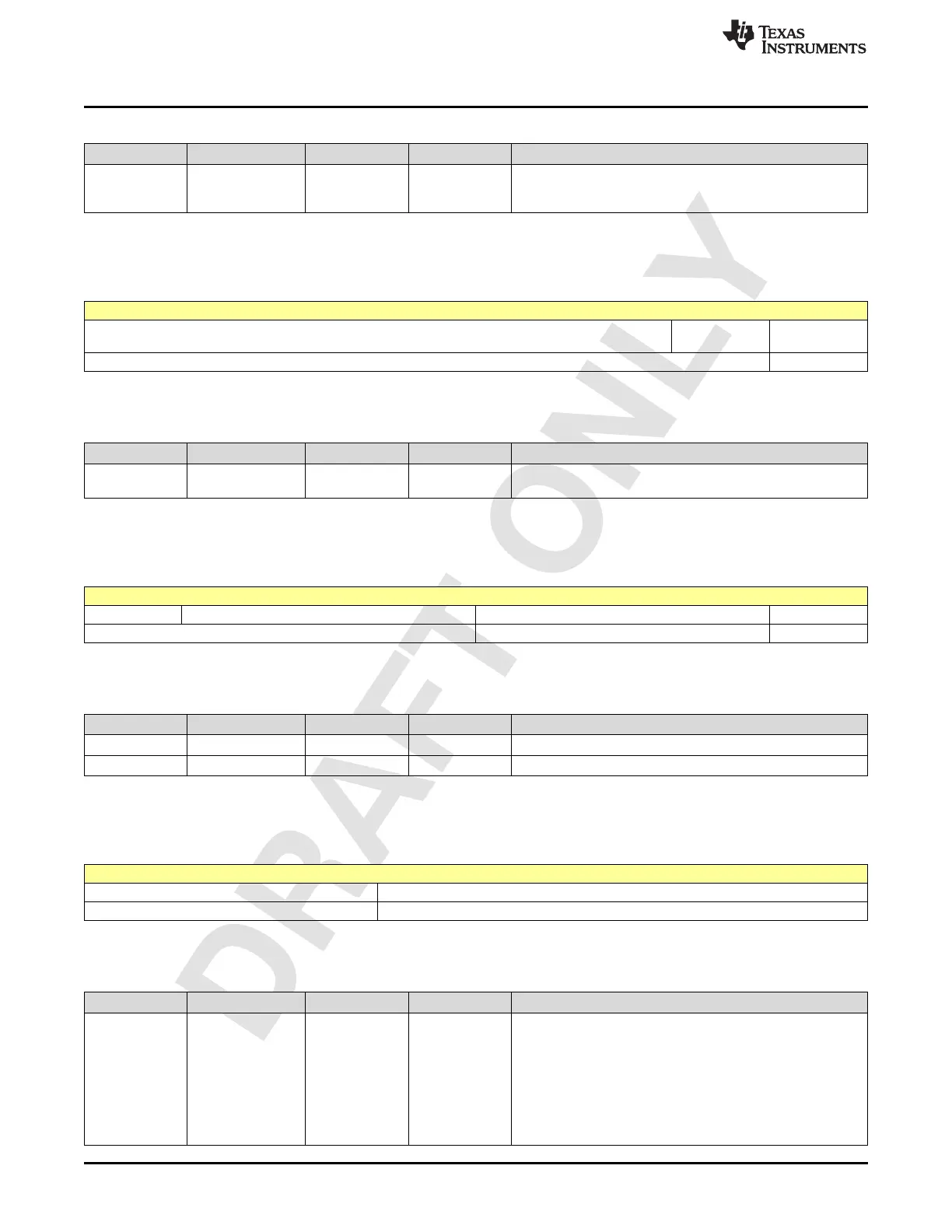

2.6.147 Register 49FBh (offset = 49FBh) [reset = 60h]

Figure 2-861. Register 49FBh

7 6 5 4 3 2 1 0

RX_PLL_VCO_RANGE_LSB

R/W-3h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-867. Register 49FB Field Descriptions

Bit Field Type Reset Description

7-5

RX_PLL_VCO_RA

NGE_LSB

R/W 3h

PLL VCO range settings:

0h: 27Gbps < NRZ rate < 32Gbps

1h: 25Gbps < NRZ rate < 30Gbps

2h: 24Gbps < NRZ rate < 28Gbps

3h: 23Gbps < NRZ rate < 26Gbps

4h: 22Gbps < NRZ rate < 24Gbps

5h: 21Gbps < NRZ rate < 23Gbps

6h: 20Gbps < NRZ rate < 22Gbps

7h: 19Gbps < NRZ rate < 21Gbps

Loading...

Loading...