ADC JESD Register Map

www.ti.com

446

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

Table 2-677. Register 102 Field Descriptions

Bit Field Type Reset Description

7-4

JESD_MISC_STAT

US_LANE1

R 0h

bit0 - sync_req

bit1 - first sync req

bit2 - sysref req

bit3 - bit wise of of multiframe_end

3-0

JESD_MISC_STAT

US_LANE0

R 0h

bit0 - sync_req

bit1 - first sync req

bit2 - sysref req

bit3 - bit wise of of multiframe_end

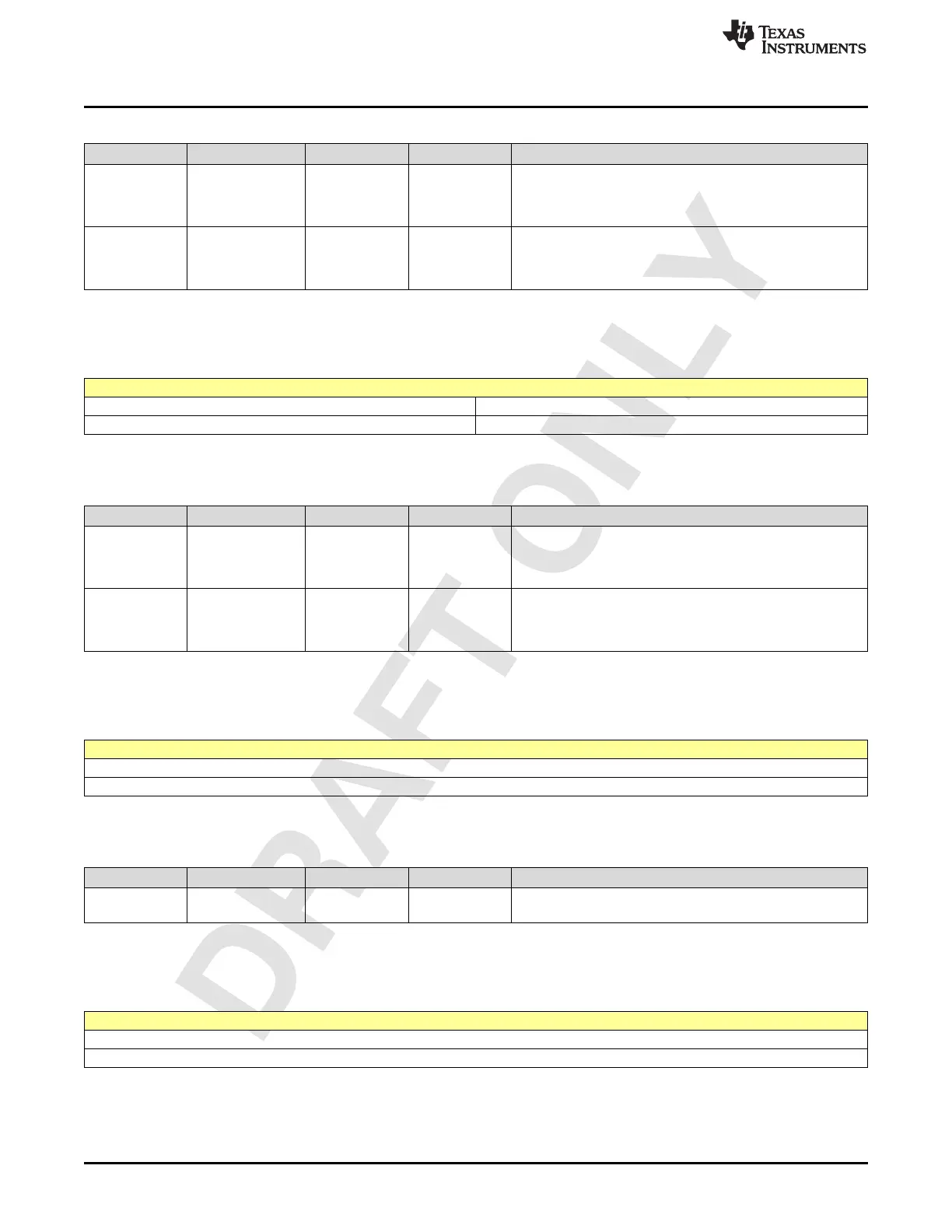

2.5.177 Register 103h (offset = 103h) [reset = 0h]

Figure 2-673. Register 103h

7 6 5 4 3 2 1 0

JESD_MISC_STATUS_LANE3 JESD_MISC_STATUS_LANE2

R-0h R-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-678. Register 103 Field Descriptions

Bit Field Type Reset Description

7-4

JESD_MISC_STAT

US_LANE3

R 0h

bit0 - sync_req

bit1 - first sync req

bit2 - sysref req

bit3 - bit wise of of multiframe_end

3-0

JESD_MISC_STAT

US_LANE2

R 0h

bit0 - sync_req

bit1 - first sync req

bit2 - sysref req

bit3 - bit wise of of multiframe_end

2.5.178 Register 104h (offset = 104h) [reset = 0h]

Figure 2-674. Register 104h

7 6 5 4 3 2 1 0

JESD_SYNC_ERR_CNT_LANE0

R-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-679. Register 104 Field Descriptions

Bit Field Type Reset Description

7-0

JESD_SYNC_ERR

_CNT_LANE0

R 0h

Register is relevant for JESD-B

Number of sync toggles after init_state removal for STX1/5

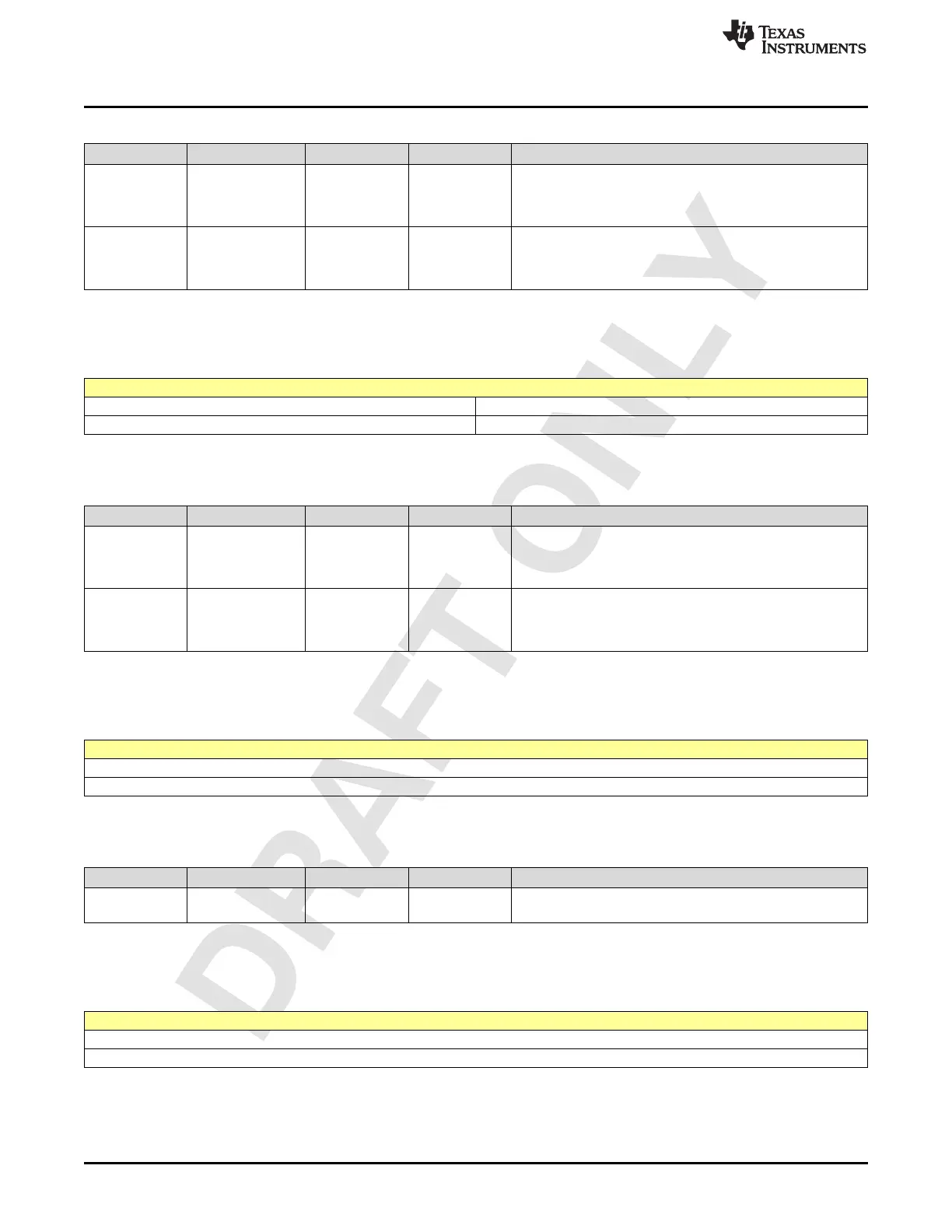

2.5.179 Register 105h (offset = 105h) [reset = 0h]

Figure 2-675. Register 105h

7 6 5 4 3 2 1 0

JESD_SYNC_ERR_CNT_LANE1

R-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Loading...

Loading...