www.ti.com

DAC JESD Register Map

277

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

Table 2-266. Register 40 Field Descriptions (continued)

Bit Field Type Reset Description

1-1

LINK1_COMMA_A

LIGN_RESET

R/W 0h

For Lanes[2:3]/lanes[6:7]

JESDB: reset K28.5 pattern search and start again

JESDC: reset sync_header alignment search and start again

0-0

LINK0_COMMA_A

LIGN_RESET

R/W 0h

For Lanes[0:1]/lanes[4:5]

JESDB: reset K28.5 pattern search and start again

JESDC: reset sync_header alignment search and start again

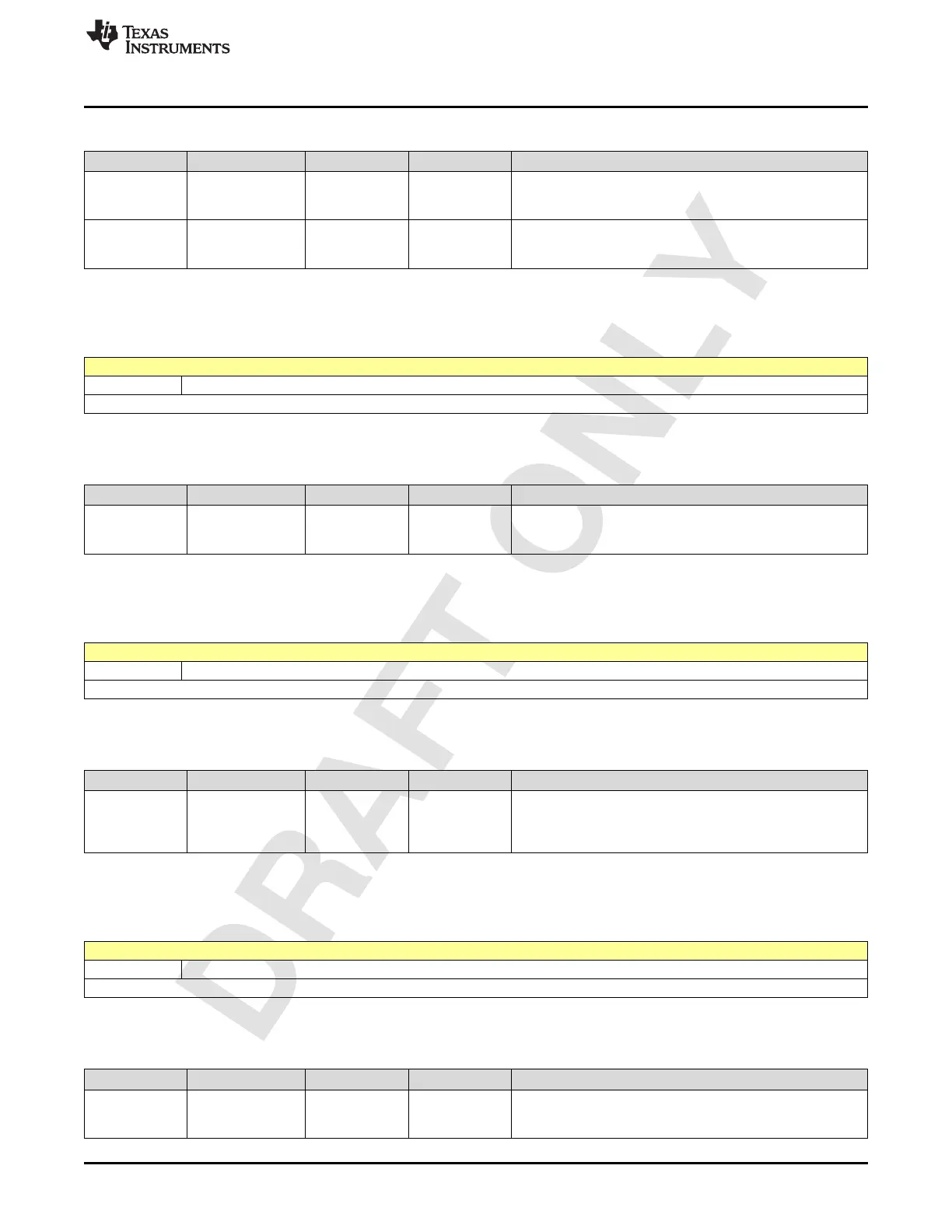

2.4.34 Register 41h (offset = 41h) [reset = 0h]

Figure 2-263. Register 41h

7 6 5 4 3 2 1 0

COMMA_ALIGN_BIT_COUNTER_INIT

R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-267. Register 41 Field Descriptions

Bit Field Type Reset Description

6-0

COMMA_ALIGN_B

IT_COUNTER_INI

T

R/W 0h Load the internal index-counter with this value

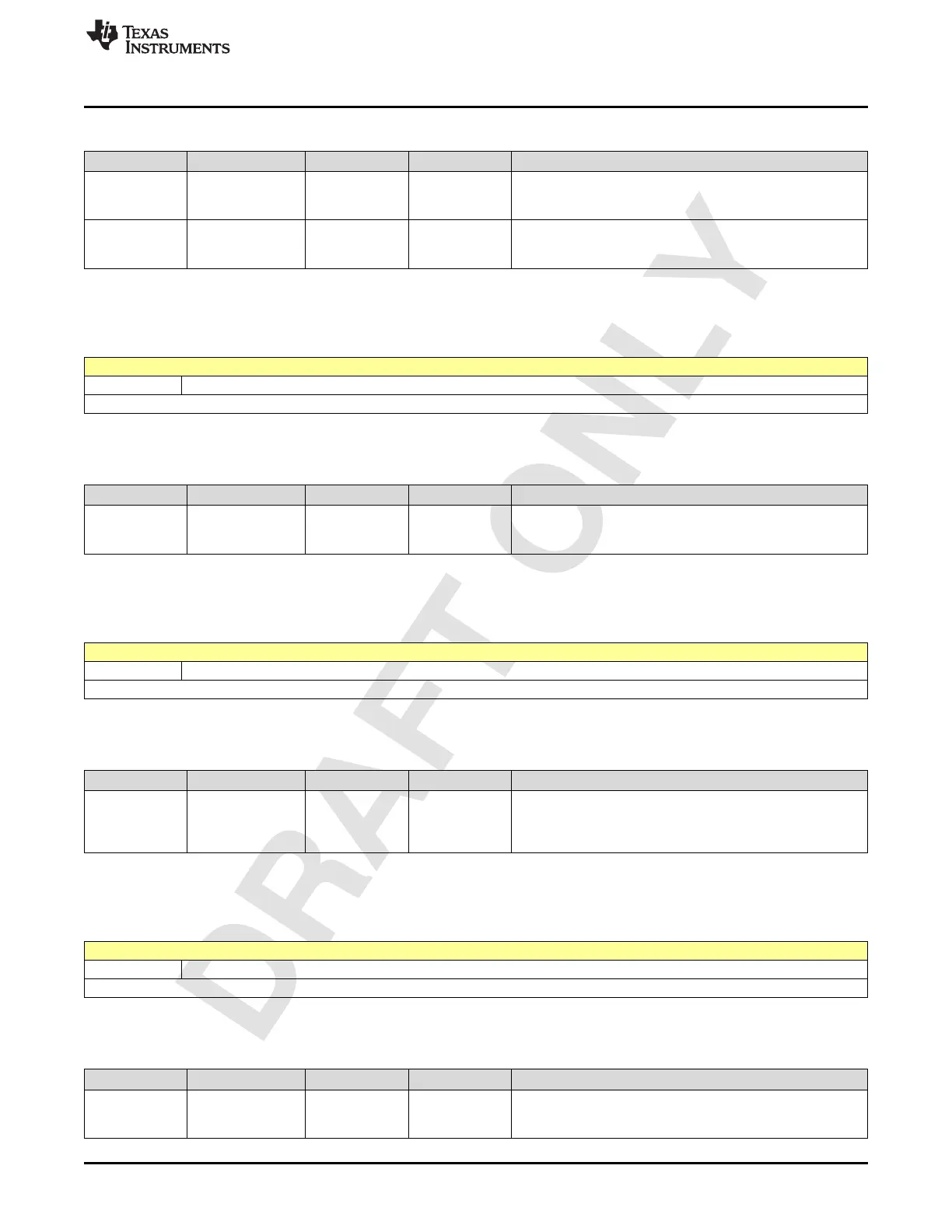

2.4.35 Register 42h (offset = 42h) [reset = 10h]

Figure 2-264. Register 42h

7 6 5 4 3 2 1 0

COMMA_ALIGN_VALID_THRESH

R/W-10h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-268. Register 42 Field Descriptions

Bit Field Type Reset Description

6-0

COMMA_ALIGN_V

ALID_THRESH

R/W 10h

JESDB: Minimum number of 4*K28.5 control characters

needed to jump from hunt state to lock state

JESDC: Minimum number of sync-header toggles needed to

jump from hunt state to lock state

2.4.36 Register 43h (offset = 43h) [reset = 2h]

Figure 2-265. Register 43h

7 6 5 4 3 2 1 0

COMMA_ALIGN_INVALID_THRESH

R/W-2h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-269. Register 43 Field Descriptions

Bit Field Type Reset Description

6-0

COMMA_ALIGN_I

NVALID_THRESH

R/W 2h

JESDB: UNUSED

JESDC: Minimum number of continous sync-header invalid

pattern needed to jump from lock state to hunt state

Loading...

Loading...