DAC JESD Register Map

www.ti.com

276

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

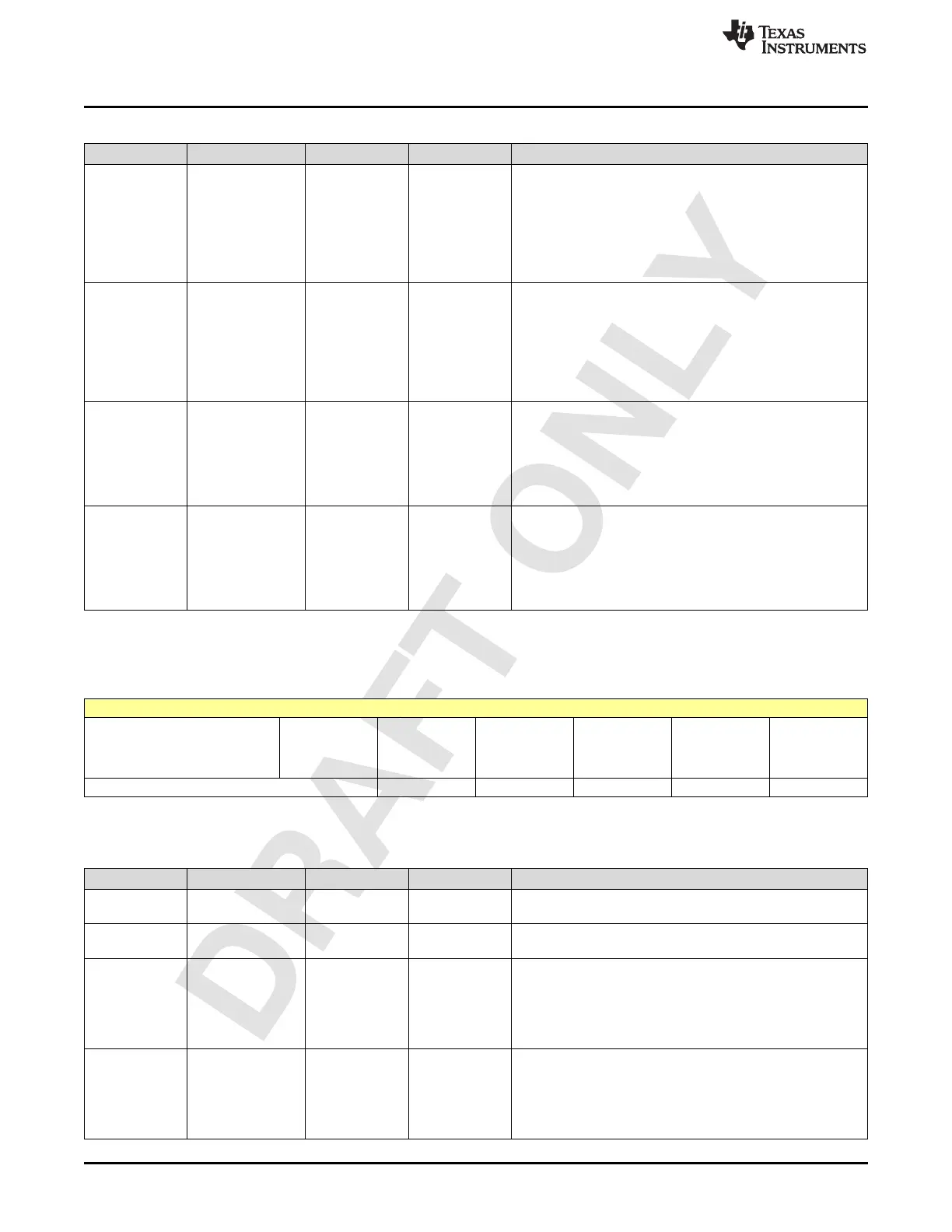

Table 2-265. Register 3F Field Descriptions

Bit Field Type Reset Description

7-6

SYNC_FIFO_66TO

33_OFFSET_LANE

23

R/W 0h

JESDB: UNUSED.

JESDC: Offset for 66to33 lanes[2:3]/lanes[6:7] fifo(fifo which is

used to convert JESDC 66-bit words to 33 bits so that the

elastic buffer can be common between JESDB and JESDC)

0 : 0

1 : 1

2 : 2

3 : 3

5-4

SYNC_FIFO_66TO

33_OFFSET_LANE

01

R/W 0h

JESDB: UNUSED.

JESDC: Offset for 66to33 lanes[0:1]/lanes[4:5] fifo(fifo which is

used to convert JESDC 66-bit words to 33 bits so that the

elastic buffer can be common between JESDB and JESDC)

0 : 0

1 : 1

2 : 2

3 : 3

3-2

SYNC_FIFO_33TO

66_OFFSET_LANE

23

R/W 2h

JESDB: UNUSED.

JESDC: Offset for 33to66 lanes[2:3]/lanes[6:7] fifo (fifo which

is used to convert 33 bits from gearbox to 66 bits for IP use).

0 : 0

1 : 1

2 : 2

3 : 3

1-0

SYNC_FIFO_33TO

66_OFFSET_LANE

01

R/W 2h

JESDB: UNUSED.

JESDC: Offset for 33to66 lanes[0:1]/lanes[4:5] fifo (fifo which

is used to convert 33 bits from gearbox to 66 bits for IP use).

0 : 0

1 : 1

2 : 2

3 : 3

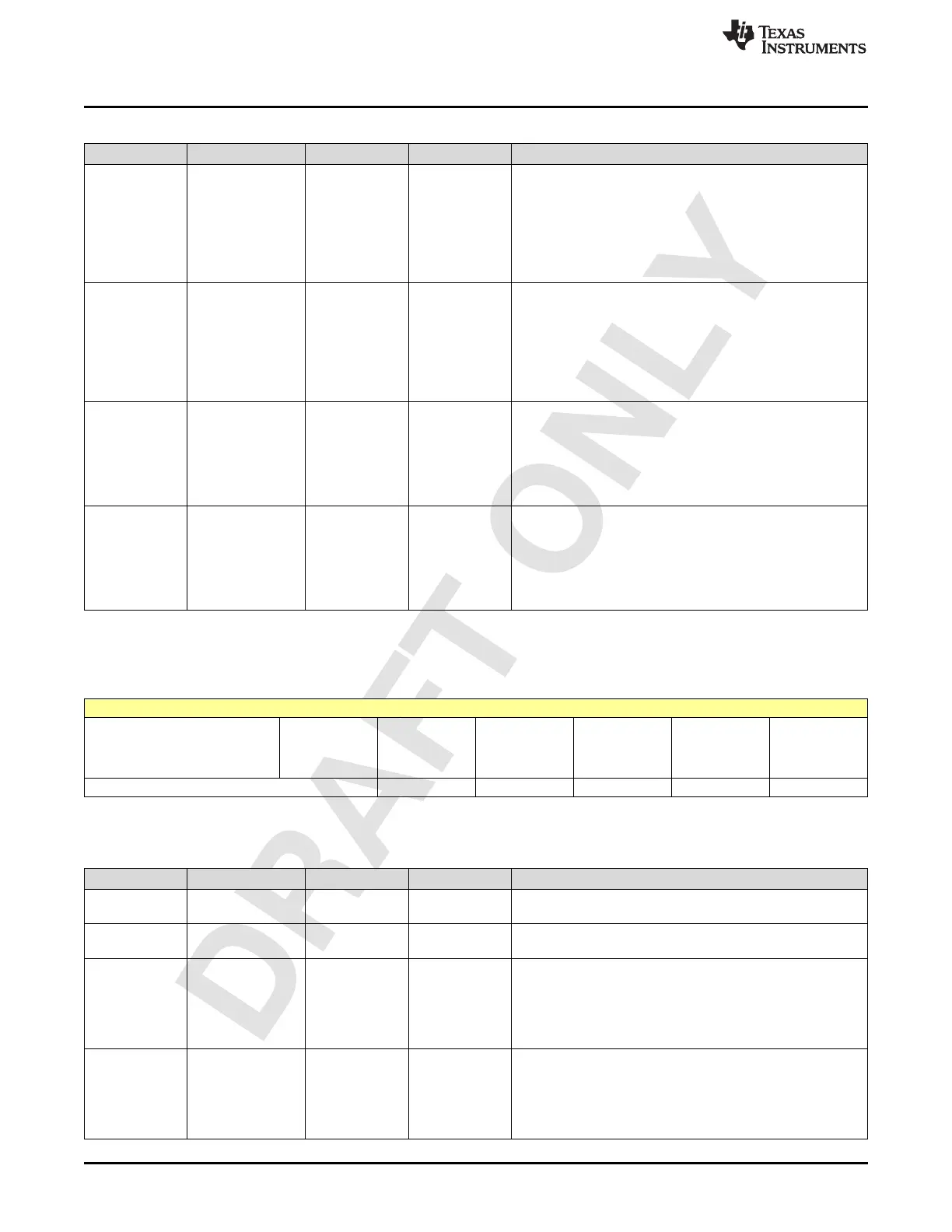

2.4.33 Register 40h (offset = 40h) [reset = 0h]

Figure 2-262. Register 40h

7 6 5 4 3 2 1 0

COMMA_ALIG

N_TIMER_EN

COMMA_ALIG

N_REALIGN_M

ASK

LINK1_COMM

A_ALIGN_LOC

K_RESET_DIS

ABLE

LINK0_COMM

A_ALIGN_LOC

K_RESET_DIS

ABLE

LINK1_COMM

A_ALIGN_RES

ET

LINK0_COMM

A_ALIGN_RES

ET

R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-266. Register 40 Field Descriptions

Bit Field Type Reset Description

5-5

COMMA_ALIGN_T

IMER_EN

R/W 0h UNUSED

4-4

COMMA_ALIGN_R

EALIGN_MASK

R/W 0h TESTMODE

3-3

LINK1_COMMA_A

LIGN_LOCK_RES

ET_DISABLE

R/W 0h

For Lanes[2:3]/lanes[6:7]

JESDB: Any lane error will reset the k28.5 pattern search.

Setting this will will override the reset of those state machines.

JESDC: Any lane error will reset the sync-header alignment

search. Setting this will will override the reset of those state

machines

2-2

LINK0_COMMA_A

LIGN_LOCK_RES

ET_DISABLE

R/W 0h

For Lanes[0:1]/lanes[4:5]

JESDB: Any lane error will reset the k28.5 pattern search.

Setting this will will override the reset of those state machines.

JESDC: Any lane error will reset the sync-header alignment

search. Setting this will will override the reset of those state

machines

Loading...

Loading...