RX Top Register Map

www.ti.com

842

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

Table 2-1867. Register 5EA Field Descriptions

Bit Field Type Reset Description

3-3 reserved R 0h

2-2

RX_AGC_ATTN_C

HANGED

R 0h

Whether any any gain was changed DVGA/DSA/LNA as seen

by statistics module

1-1

RX_AGC_BAND1_

LNA_BYPASS_CH

ANGED

R 0h

Whether LNA gain was changed for Band 1 as seen by

statistics module

0-0

RX_AGC_BAND0_

LNA_BYPASS_CH

ANGED

R 0h

Whether LNA gain was changed for Band 0 as seen by

statistics module

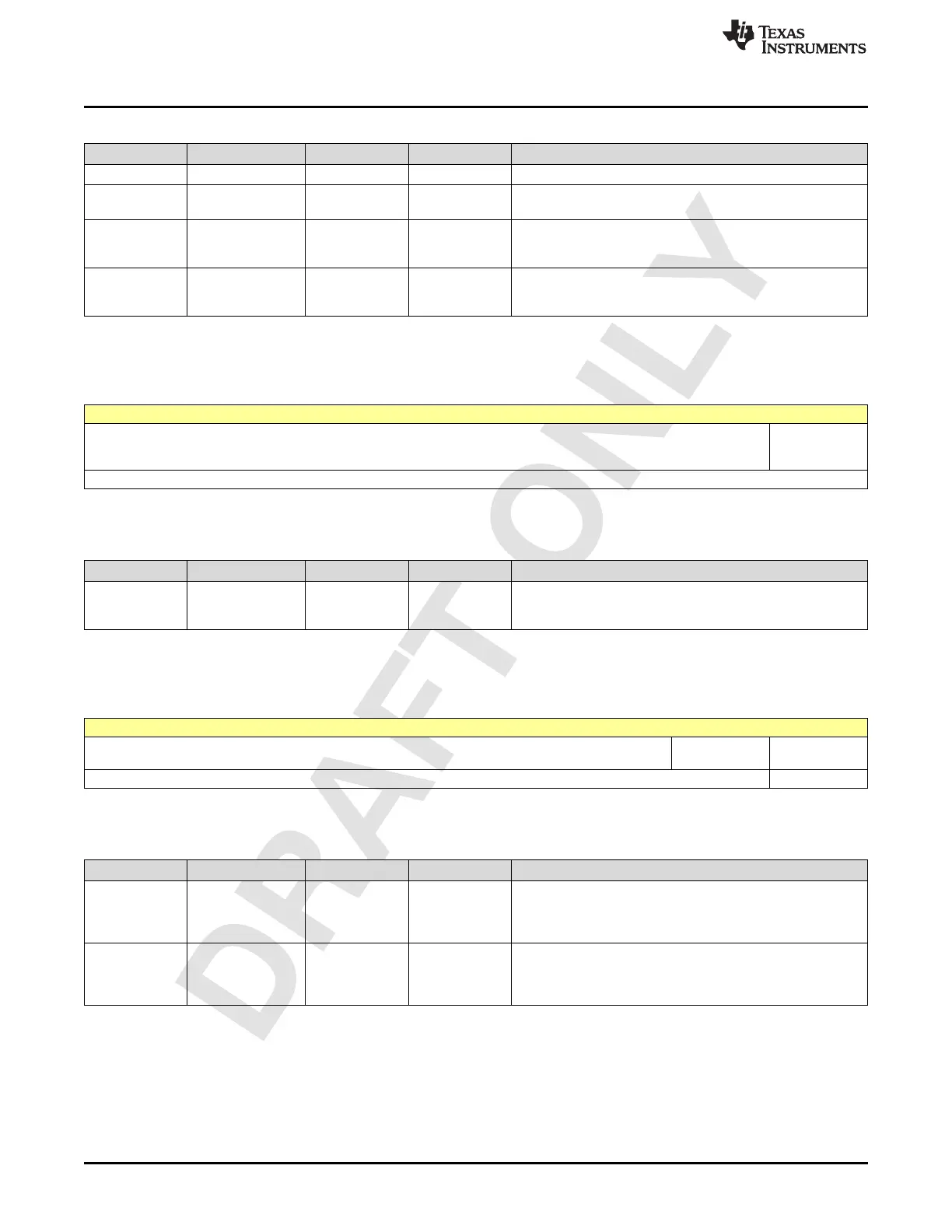

2.13.443 Register 5ECh (offset = 5ECh) [reset = 0h]

Figure 2-1855. Register 5ECh

7 6 5 4 3 2 1 0

RX_AGC_CUR

R_EXT_LNA_E

N

R-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-1868. Register 5EC Field Descriptions

Bit Field Type Reset Description

0-0

RX_AGC_CURR_E

XT_LNA_EN

R 0h

Current external LNA enable

0 : Ext LNA is bypassed

1 : Ext LNA is enabled

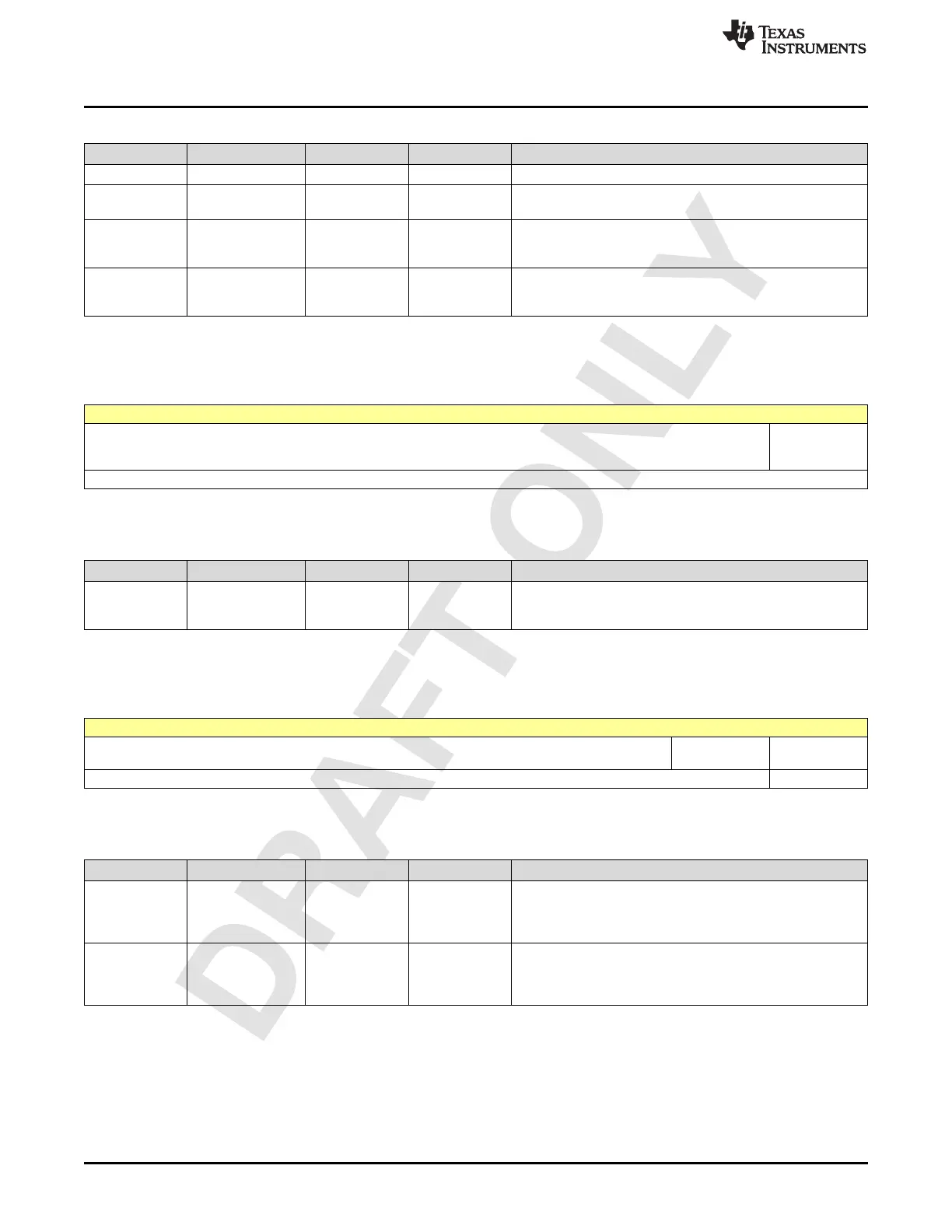

2.13.444 Register 634h (offset = 634h) [reset = 0h]

Figure 2-1856. Register 634h

7 6 5 4 3 2 1 0

RX_ALC_CLK_

EN

RX_ALC_ENA

BLE

R/W-0h R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-1869. Register 634 Field Descriptions

Bit Field Type Reset Description

1-1 RX_ALC_CLK_EN R/W 0h

clock enable for ALC module. Need to be set along with

enable_alc

0 : Disable

1 : Enable

0-0 RX_ALC_ENABLE R/W 0h

Digital Gain Compensation enabled. Can be enabled

irrespective of whether Internal AGC is enabled/disabled

0 : disable

1 : enable

Loading...

Loading...