JESD_SUBCHIP Register Map

www.ti.com

164

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

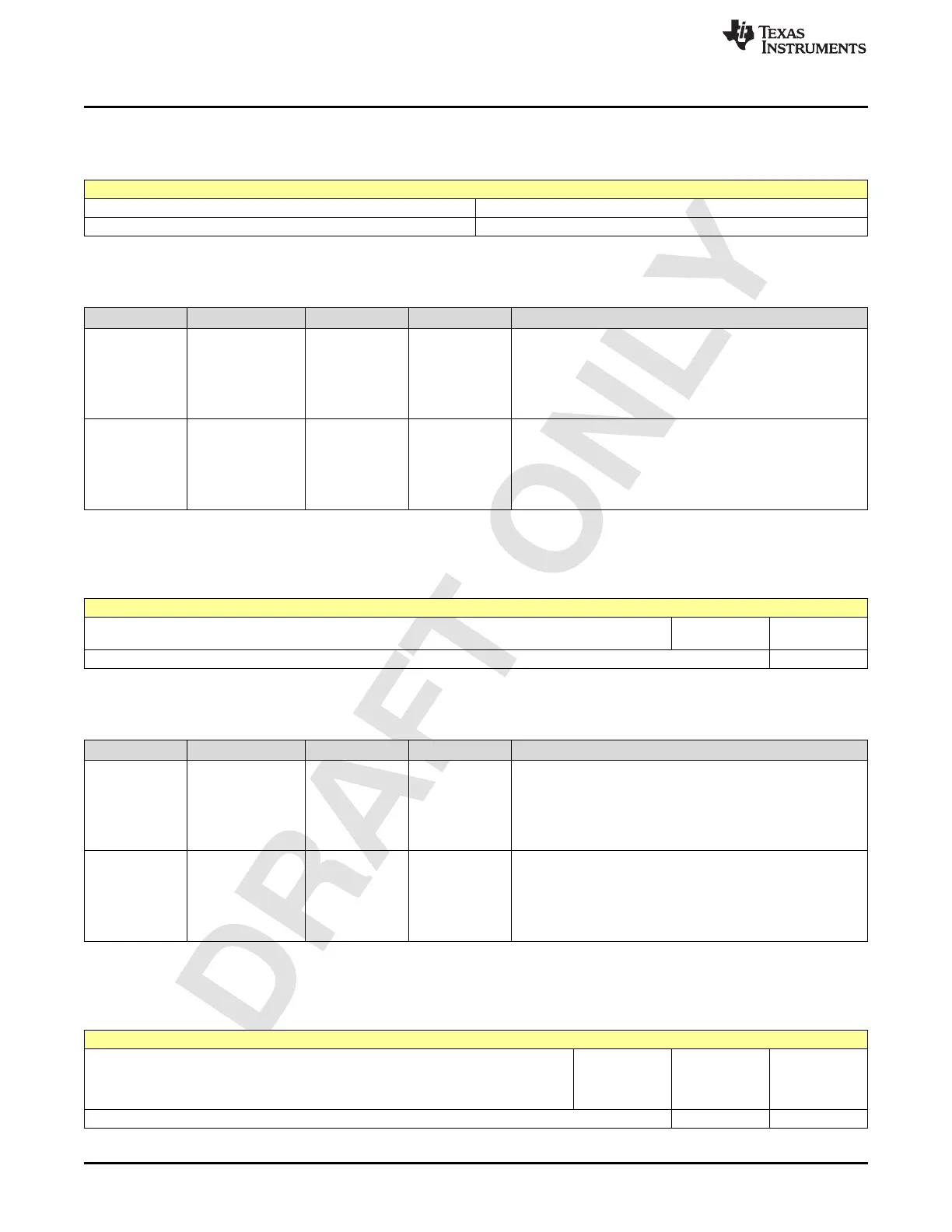

2.3.6 Register 27h (offset = 27h) [reset = FFh]

Figure 2-47. Register 27h

7 6 5 4 3 2 1 0

SERDESCD_TXBCLK_ENA SERDESAB_TXBCLK_ENA

R/W-Fh R/W-Fh

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-50. Register 27 Field Descriptions

Bit Field Type Reset Description

7-4

SERDESCD_TXBC

LK_ENA

R/W Fh

register to enable SerdesCD STX5, STX6, STX7 and STX8

txbclks (0 -disable, 1 - enable)

[3] = STX8 txbclk enable

[2] = STX7 txbclk enable

[1] = STX6 txbclk enable

[0] = STX5 txbclk enable

3-0

SERDESAB_TXBC

LK_ENA

R/W Fh

register to enable SerdesAB STX1, STX2, STX3 and STX4

txbclks (0 -disable, 1 - enable)

[3] = STX4 txbclk enable

[2] = STX3 txbclk enable

[1] = STX2 txbclk enable

[0] = STX1 txbclk enable

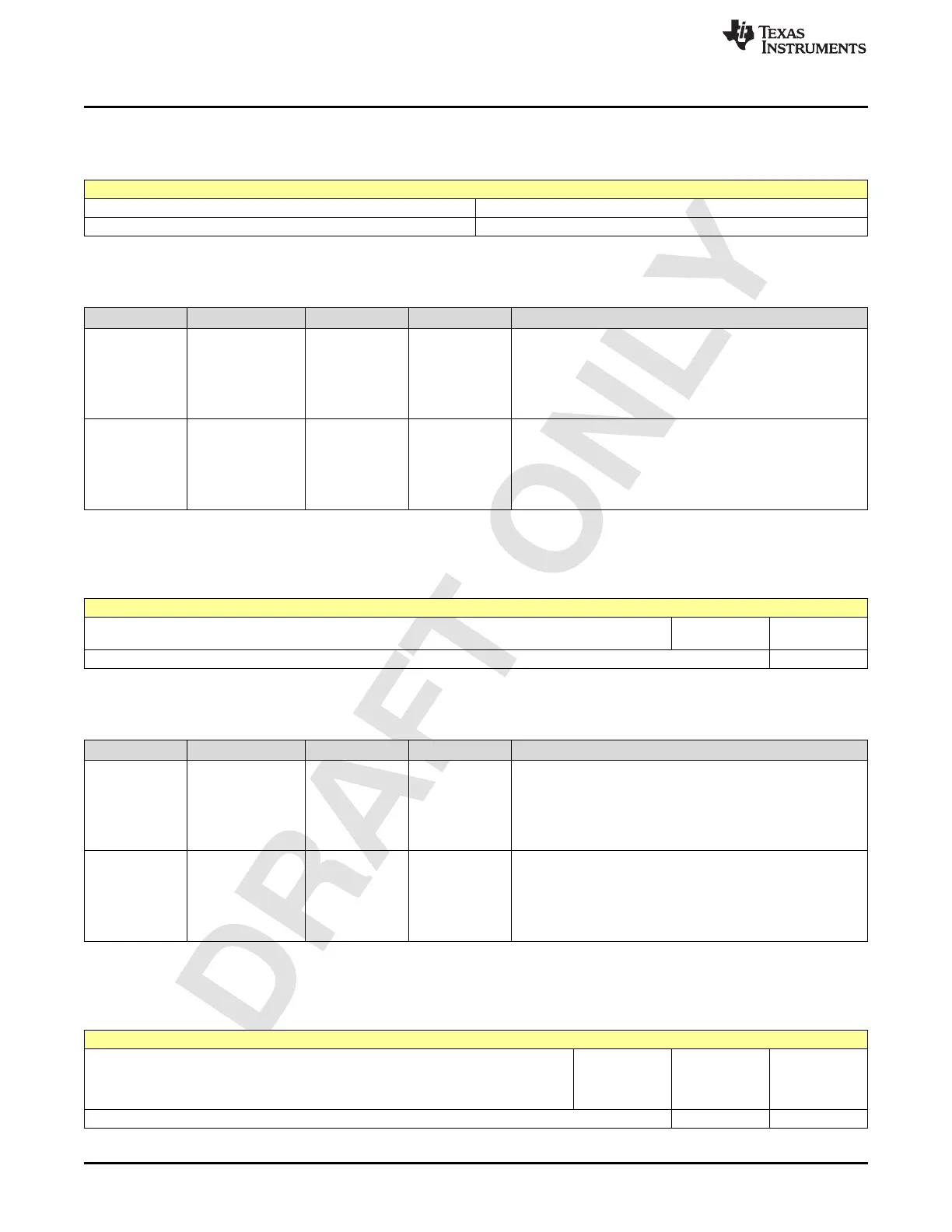

2.3.7 Register 29h (offset = 29h) [reset = 3h]

Figure 2-48. Register 29h

7 6 5 4 3 2 1 0

DUAL_2T2R1F

_MODE_CD

DUAL_2T2R1F

_MODE_AB

R/W-1h R/W-1h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-51. Register 29 Field Descriptions

Bit Field Type Reset Description

1-1

DUAL_2T2R1F_M

ODE_CD

R/W 1h

Used for 2r1f_cd instance

Default mode is dual 2r1f modes.

For RX L1 and M16 cases (or) FB M4, make this bit 0.

Recommended to use LATTE to configure this register as the

correct values and the sequence depends on the mode of

usage.

0-0

DUAL_2T2R1F_M

ODE_AB

R/W 1h

Used for 2r1f_ab instance

Default mode is dual 2r1f modes.

For RX L1 and M16 cases (or) FB M4, make this bit 0.

Recommended to use LATTE to configure this register as the

correct values and the sequence depends on the mode of

usage.

2.3.8 Register 2Ah (offset = 2Ah) [reset = 0h]

Figure 2-49. Register 2Ah

7 6 5 4 3 2 1 0

DDC_RD_CLK

_FBCD_FBAB_

CLK_SYSREF_

MUX

DDC_RD_CLK

_RXD_RXB_CL

K_SYSREF_M

UX

DDC_RD_CLK

_RXC_RXA_CL

K_SYSREF_M

UX

R/W-0h R/W-0h R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Loading...

Loading...