ADC JESD Register Map

www.ti.com

454

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

Table 2-703. Register 11C Field Descriptions

Bit Field Type Reset Description

7-6 0 R/W 0h Must read or write 0

5-4

CTRL_FB_MAPPE

R_CLK_GATING

R/W 0h

When set to 2'b10, all functional clock gating of fb mapper is

disabled

3-2

CTRL_RX2_MAPP

ER_CLK_GATING

R/W 0h

When set to 2'b10, all functional clock gating of rx2 mapper is

disabled

1-0

CTRL_RX1_MAPP

ER_CLK_GATING

R/W 0h

When set to 2'b10, all functional clock gating of rx1 mapper is

disabled

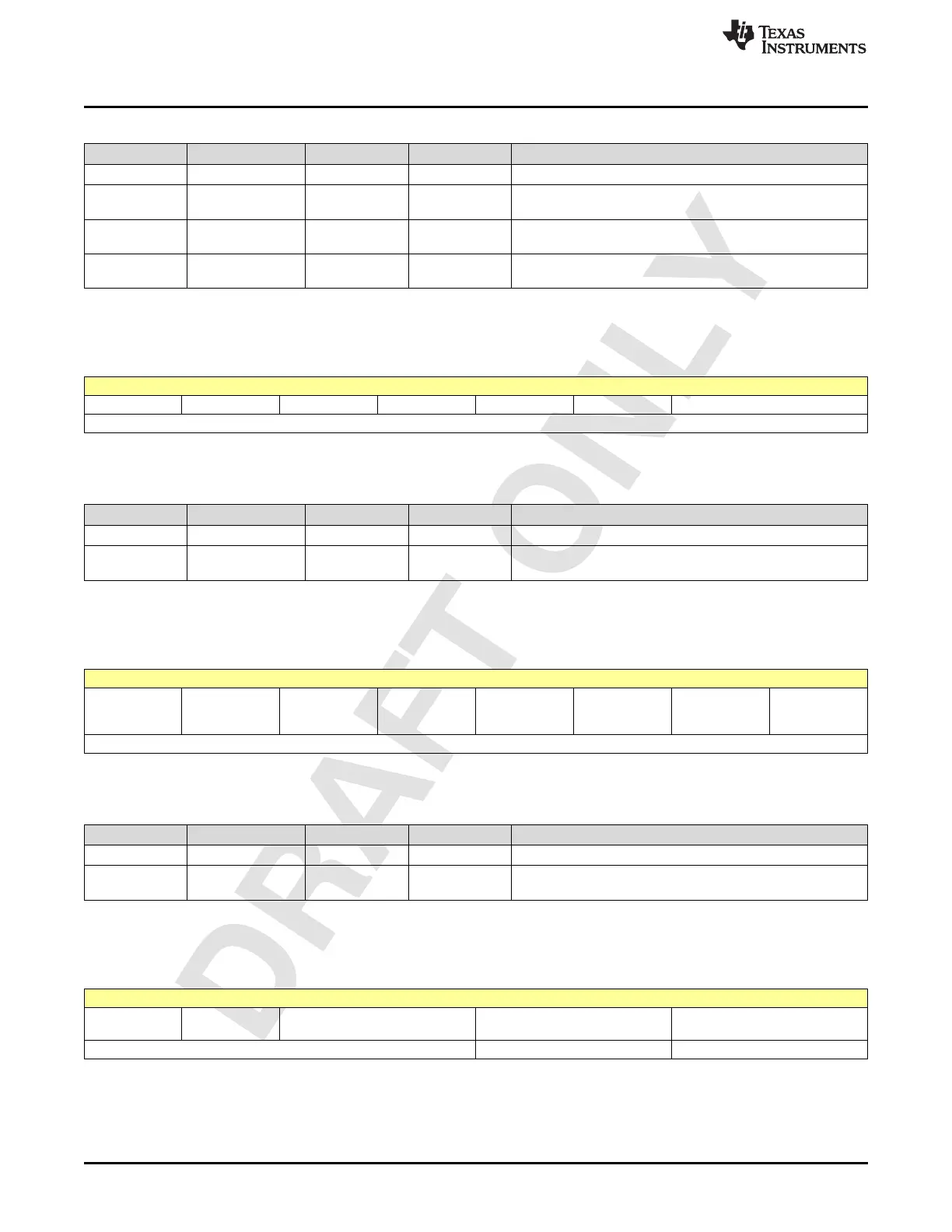

2.5.203 Register 11Dh (offset = 11Dh) [reset = 0h]

Figure 2-699. Register 11Dh

7 6 5 4 3 2 1 0

0 0 0 0 0 0 CTRL_RX3_RX4_CLK_GATING

R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-704. Register 11D Field Descriptions

Bit Field Type Reset Description

7-2 0 R/W 0h Must read or write 0

1-0

CTRL_RX3_RX4_

CLK_GATING

R/W 0h

When set to 2'b10, all functional clock gating of rx34 mapper

is disabled

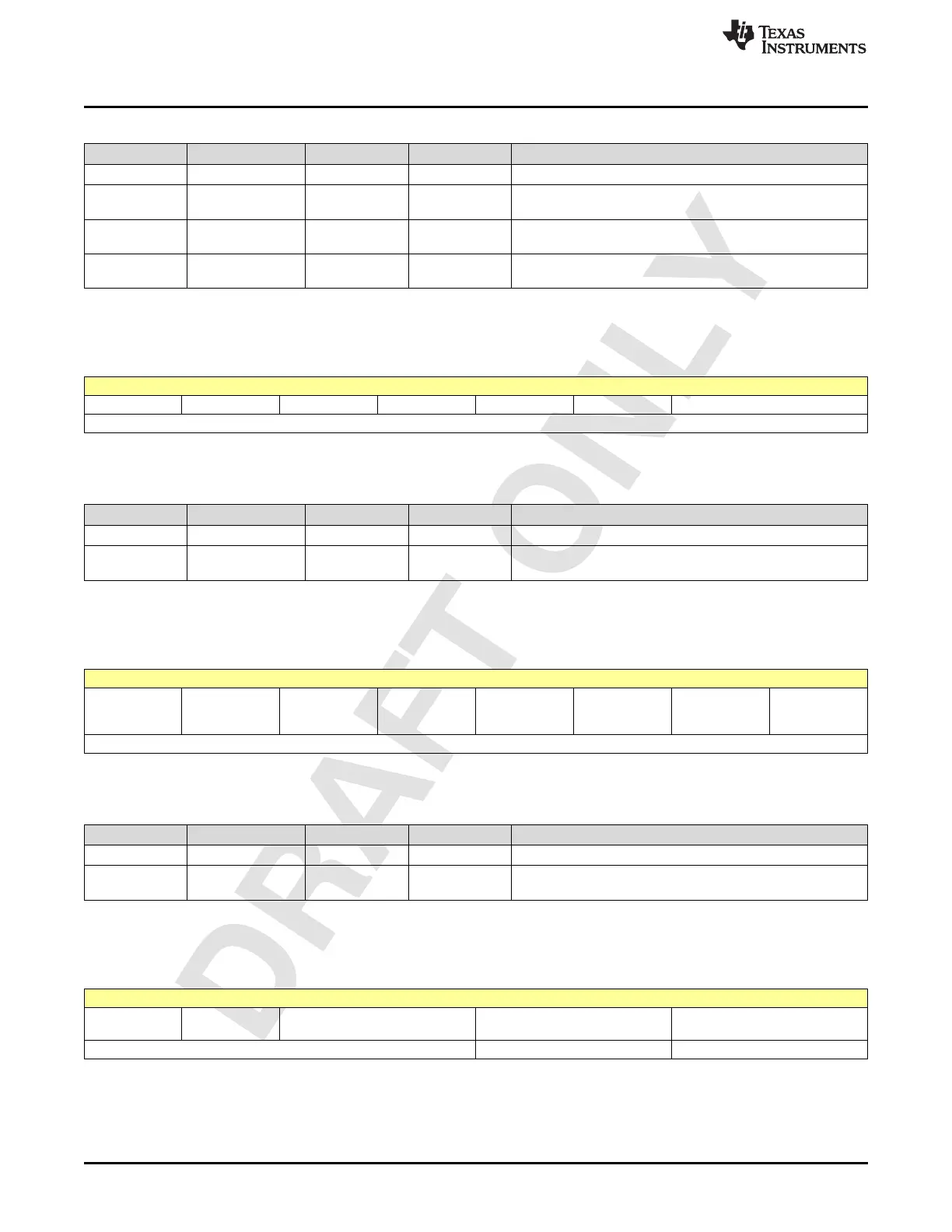

2.5.204 Register 11Eh (offset = 11Eh) [reset = 1h]

Figure 2-700. Register 11Eh

7 6 5 4 3 2 1 0

0 0 0 0 0 0 0 EN_SERDES_

FIFO_DATA_G

ATING

R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-1h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-705. Register 11E Field Descriptions

Bit Field Type Reset Description

7-1 0 R/W 0h Must read or write 0

0-0

EN_SERDES_FIF

O_DATA_GATING

R/W 1h

By default, serdes data is gated on empty flag. If set to 0, this

gating is disabled

2.5.205 Register 120h (offset = 120h) [reset = 0h]

Figure 2-701. Register 120h

7 6 5 4 3 2 1 0

0 0 CTRL_RX3_RX4_MSF_SIG_INV

ALID

CTRL_RX2_MSF_SIG_INVALID CTRL_RX1_MSF_SIG_INVALID

R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Loading...

Loading...