www.ti.com

SERDES Register Map

513

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

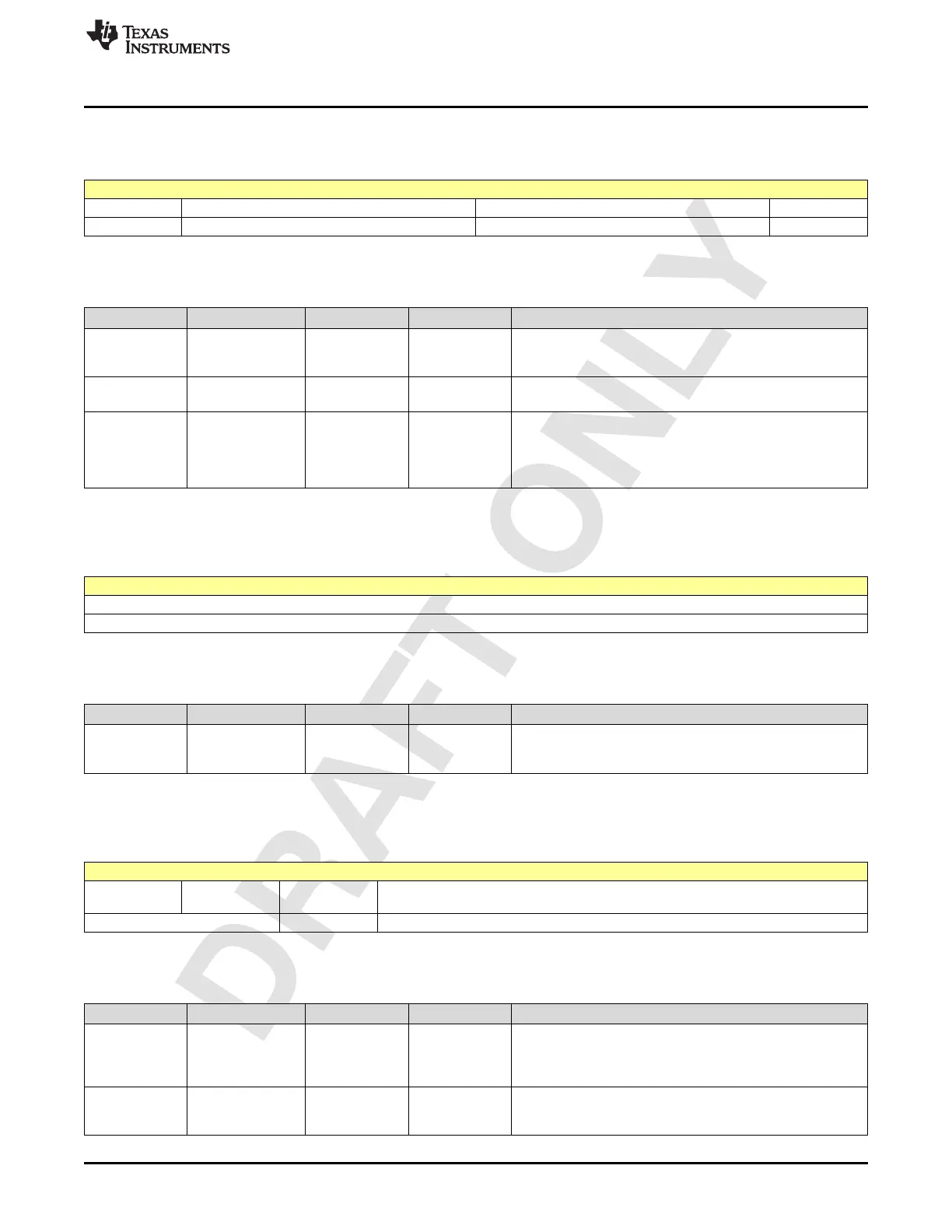

2.6.148 Register 49FCh (offset = 49FCh) [reset = B4h]

Figure 2-862. Register 49FCh

7 6 5 4 3 2 1 0

PU_RX_PLL RX_CHARGE_PUMP_CUR RX_VCO_CURRENT

R/W-1h R/W-3h R/W-2h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-868. Register 49FC Field Descriptions

Bit Field Type Reset Description

7-7 PU_RX_PLL R/W 1h

Power up RX PLL.

0h: Power down

1h: Power up

6-4

RX_CHARGE_PU

MP_CUR

R/W 3h Set the charge pump current.

3-1

RX_VCO_CURRE

NT

R/W 2h

Sets VCO current.

100b: 24Gbps < NRZ rate < 32Gbps

101b: 21Gbps < NRZ rate < 23Gbps

110b: 20Gbps < NRZ rate < 22Gbps

111b: 19Gbps < NRZ rate < 21Gbps

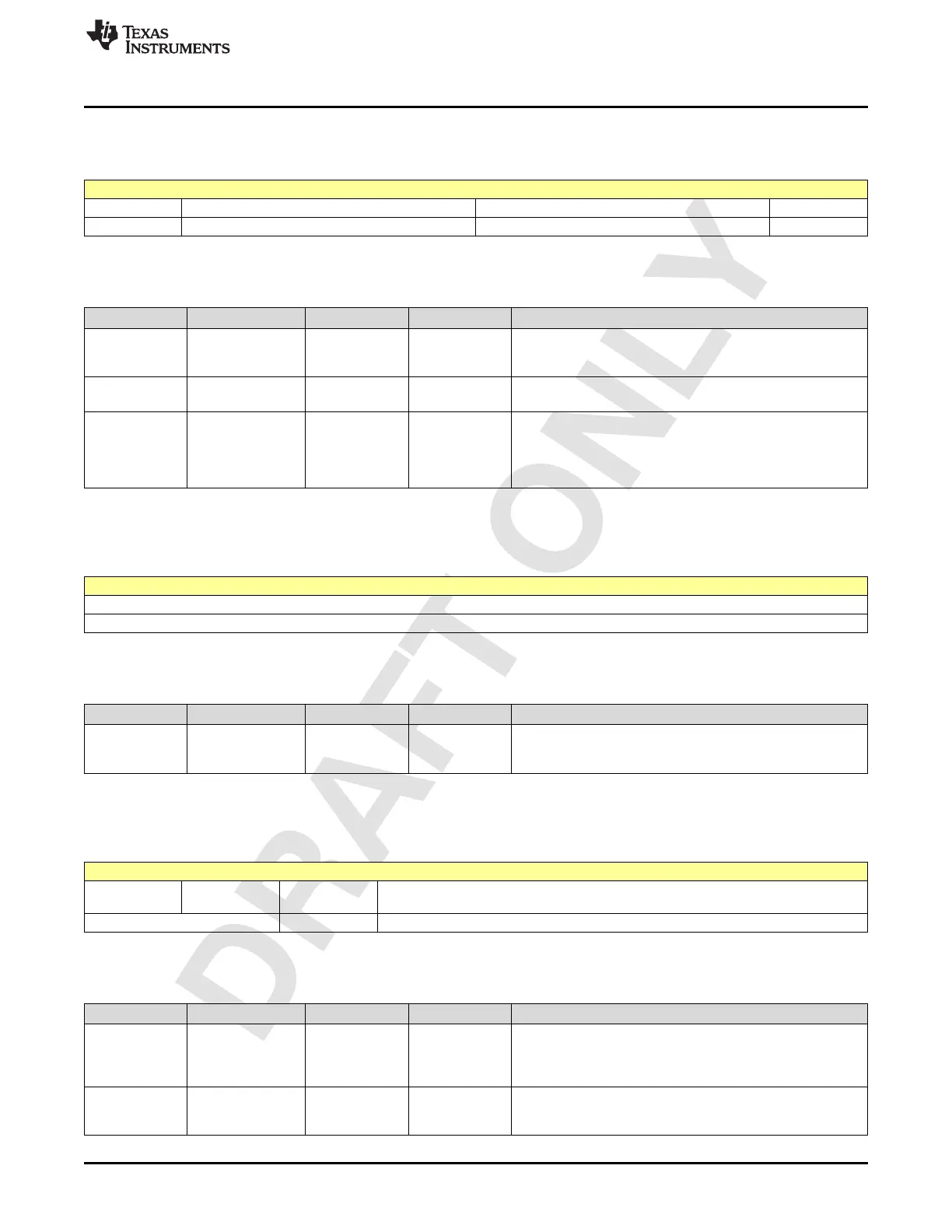

2.6.149 Register 49FDh (offset = 49FDh) [reset = A5h]

Figure 2-863. Register 49FDh

7 6 5 4 3 2 1 0

RX_PLL_N

R/W-A5h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-869. Register 49FD Field Descriptions

Bit Field Type Reset Description

7-0 RX_PLL_N R/W A5h

RX PLL clock multiplier where the PLL frequency = PLL

reference clock * 2 * PLL_N. The SerDes user rate = 2 * PLL

frequency.

2.6.150 Register 49FEh (offset = 49FEh) [reset = 20h]

Figure 2-864. Register 49FEh

7 6 5 4 3 2 1 0

REFCLK_DIV4

_EN

PU_RX_AGC_

MASTER

R/W-0h R/W-1h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-870. Register 49FE Field Descriptions

Bit Field Type Reset Description

6-6 REFCLK_DIV4_EN R/W 0h

Mux control to select the LVDS reference clock directly to the

PLLs or to a /4 version

0h: PLL reference = refclk / 1

1h: PLL reference = refclk / 4

5-5

PU_RX_AGC_MAS

TER

R/W 1h

Power up RX AGC master

0h: Power down

1h: Power up

Loading...

Loading...